# 3. MCU動作モード

3

## 第3章 目次

|                                 |    |

|---------------------------------|----|

| 3. 1 概要                         | 67 |

| 3. 1. 1 動作モードの種類の選択             | 67 |

| 3. 1. 2 レジスタ構成                  | 69 |

| 3. 2 モードコントロールレジスタ (M D C R)    | 70 |

| 3. 3 システムコントロールレジスタ (S Y S C R) | 71 |

| 3. 4 各動作モードの説明                  | 74 |

| 3. 4. 1 モード 1                   | 74 |

| 3. 4. 2 モード 2                   | 74 |

| 3. 4. 3 モード 3                   | 74 |

| 3. 4. 4 モード 4                   | 74 |

| 3. 4. 5 モード 5                   | 75 |

| 3. 4. 6 モード 6                   | 75 |

| 3. 4. 7 モード 7                   | 75 |

| 3. 5 各動作モードにおける端子機能             | 76 |

| 3. 6 各動作モードのメモリマップ              | 77 |

### 3.1 概要

#### 3.1.1 動作モードの種類の選択

H8/3048シリーズには、7種類の動作モード（モード1～7）があります。これらのモードは、モード端子(MD<sub>2</sub>～MD<sub>0</sub>)を表3.1のように設定することによってバスモードの初期状態とアドレス空間を選択することができます。

表3.1 動作モードの種類の選択

| 動作モード | 端子設定            |                 |                 | 内 容              |                          |       |                  |

|-------|-----------------|-----------------|-----------------|------------------|--------------------------|-------|------------------|

|       | MD <sub>2</sub> | MD <sub>1</sub> | MD <sub>0</sub> | アドレス空間           | バスモード 初期状態 <sup>*1</sup> | 内蔵ROM | 内蔵RAM            |

| —     | 0               | 0               | 0               | —                | —                        | —     | —                |

| モード1  | 0               | 0               | 1               | 拡張モード            | 8ビット                     | 無効    | 有効 <sup>*2</sup> |

| モード2  | 0               | 1               | 0               | 拡張モード            | 16ビット                    | 無効    | 有効 <sup>*2</sup> |

| モード3  | 0               | 1               | 1               | 拡張モード            | 8ビット                     | 無効    | 有効 <sup>*2</sup> |

| モード4  | 1               | 0               | 0               | 拡張モード            | 16ビット                    | 無効    | 有効 <sup>*2</sup> |

| モード5  | 1               | 0               | 1               | 拡張モード            | 8ビット                     | 有効    | 有効 <sup>*2</sup> |

| モード6  | 1               | 1               | 0               | 拡張モード            | 8ビット                     | 有効    | 有効 <sup>*2</sup> |

| モード7  | 1               | 1               | 1               | シングルチップアドバンストモード | —                        | 有効    | 有効               |

【注】<sup>\*1</sup> モード1～6において、バス幅コントロールレジスタ(ABWCR)を設定することによりデータバス幅をエリアごとに8ビットデータバスまたは16ビットデータバスにすることができます。

詳細は、「第6章 バスコントローラ」を参照してください。

<sup>\*2</sup> SYSCRのRAMEビットを“0”にクリアすると外部アドレス空間に切り換わります。

アドレス空間は、1Mバイト／16Mバイトのいずれかを選択することができます。外部データバスのバス幅はABWCRにより、8ビット／16ビットバスモードのいずれかになります。すべてのエリアを8ビットアクセス空間に設定した場合、8ビットバスモードとなります。詳細は「第6章 バスコントローラ」を参照してください。

モード1～4は、外部メモリおよび周辺デバイスをアクセスすることができる内蔵ROM無効拡張モードです。

モード1、2でサポートするアドレス空間は、最大1Mバイトです。また、モード3、4でサポートするアドレス空間は、最大16Mバイトです。

モード5、6は、外部メモリおよび周辺デバイスをアクセスすることができる内蔵ROM有効拡張モードです。モード5でサポートするアドレス空間は、最大1Mバイトです。また、モード6でサポートするアドレス空間は、最大16Mバイトです。

モード7は、内蔵ROMとRAM、内部I/Oレジスタで動作するシングルチップモードです。

すべてのポートを使用することができます。

アドレス空間は最大1Mバイトです。

モード1～7以外は、本LSIでは使用できません。したがって、モード端子は必ずモード1～7になるように設定してください。

モード端子は、動作中に変化させないでください。

### 3.1.2 レジスタ構成

本LSIにはモード端子(MD<sub>2</sub>～MD<sub>9</sub>)の状態が反映されるMDCRと、動作を制御するSYSCRがあります。レジスタ構成を表3.2に示します。

表3.2 レジスタ構成

| アドレス*  | 名 称            | 略 称   | R/W | 初期値  |

|--------|----------------|-------|-----|------|

| H'FFF1 | モードコントロールレジスタ  | MDCR  | R   | 不定   |

| H'FFF2 | システムコントロールレジスタ | SYSCR | R/W | H'0B |

【注】\* アドレスの下位16ビットを示しています。

### 3.2 モードコントロールレジスタ (MDCR)

MDCRは8ビットのリード専用のレジスタで、本LSIの現在の動作モードをモニタするのに用います。

| ビット: | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|------|---|---|---|---|---|------|------|------|

|      | — | — | — | — | — | MDS2 | MDS1 | MDS0 |

| 初期値: | 1 | 1 | 0 | 0 | 0 | —*   | —*   | —*   |

| R/W: | — | — | — | — | — | R    | R    | R    |

リザーブビット

リザーブビット

モードセレクト2～0

現在の動作モードを示すビットです。

【注】\* MD<sub>2</sub>～MD<sub>0</sub>端子により決定されます。

ビット7、6：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

ビット5～3：リザーブビット

リザーブビットです。リードすると常に“0”が読み出されます。ライトは無効です。

ビット2～0：モードセレクト2～0 (MDS2～0)

これらのビットは、モード端子(MD<sub>2</sub>～MD<sub>0</sub>)のレベルを反映した値(現在の動作モード)を示しています。MDS2～MDS0ビットはMD<sub>2</sub>～MD<sub>0</sub>端子にそれぞれ対応します。これらのビットは、リード専用でライトは無効です。MDCRをリードすると、モード端子(MD<sub>2</sub>～MD<sub>0</sub>)のレベルがこれらのビットにラッピングされます。

### 3.3 システムコントロールレジスタ (SYSCR)

SYSCRは8ビットのレジスタで本LSIの動作を制御します。

| ビット: | 7   | 6   | 5   | 4   | 3   | 2   | 1 | 0                                                                           |

|------|-----|-----|-----|-----|-----|-----|---|-----------------------------------------------------------------------------|

| 初期値: | 0   | 0   | 0   | 0   | 1   | 0   | 1 | 1                                                                           |

| R/W: | R/W | R/W | R/W | R/W | R/W | R/W | — | R/W                                                                         |

|      |     |     |     |     |     |     |   | <u>RAMイネーブル</u><br>内蔵RAMの有効／無効を選択するビットです。                                   |

|      |     |     |     |     |     |     |   | <u>リザーブビット</u><br><u>NMIエッジセレクト</u><br>NMI端子の入力エッジを選択するビットです。               |

|      |     |     |     |     |     |     |   | <u>ユーザビットイネーブル</u><br>CCRのUIビットをユーザビットとして使用するか、割込みマスクビットとして使用するかを選択するビットです。 |

|      |     |     |     |     |     |     |   | <u>スタンバイタイムセレクト2～0</u><br>ソフトウェアスタンバイモードから復帰する場合の待機時間を選択するビットです。            |

|      |     |     |     |     |     |     |   | <u>ソフトウェアスタンバイ</u><br>ソフトウェアスタンバイモードへの遷移を指定するビットです。                         |

#### ビット7:ソフトウェアスタンバイ (SSBY)

ソフトウェアスタンバイモードへの遷移を指定します（ソフトウェアスタンバイモードについては「第20章 低消費電力状態」を参照してください）。

なお、外部割込みによりソフトウェアスタンバイモードが解除され、通常動作に遷移したとき、このビットは“1”にセットされたままです。クリアする場合は、“0”をライトしてください。

| ビット7 | 説                            | 明     |

|------|------------------------------|-------|

| SSBY |                              |       |

| 0    | SLEEP命令実行後、スリープモードに遷移        | (初期値) |

| 1    | SLEEP命令実行後、ソフトウェアスタンバイモードに遷移 |       |

### ビット 6～4：スタンバイタイムセレクト 2～0 (S T S 2～0)

外部割込みによって、ソフトウェアスタンバイモードを解除する場合に、内部クロックが安定するまで C P U と内蔵周辺モジュールが待機する時間を指定します。

水晶発振の場合、動作周波数に応じて待機時間が 7 ms 以上となるように指定してください。

待機時間の設定については、「20.4.3 ソフトウェアスタンバイモード解除後の発振安定待機時間の設定」を参照してください。

| ビット 6   | ビット 5   | ビット 4   | 説明                    |

|---------|---------|---------|-----------------------|

| S T S 2 | S T S 1 | S T S 0 |                       |

| 0       | 0       | 0       | 待機時間 = 8192ステート (初期値) |

| 0       | 0       | 1       | 待機時間 = 16384ステート      |

| 0       | 1       | 0       | 待機時間 = 32768ステート      |

| 0       | 1       | 1       | 待機時間 = 65536ステート      |

| 1       | 0       | 0       | 待機時間 = 131072ステート     |

| 1       | 0       | 1       | 待機時間 = 1024ステート       |

| 1       | 1       | —       | 使用禁止                  |

### ビット 3：ユーザビットイネーブル (U E)

C C R の U I ビットをユーザビットとして使用するか、割込みマスクビットとして使用するかを選択します。

| ビット 3 | 説明                                 |

|-------|------------------------------------|

| U E   |                                    |

| 0     | C C R の U I ビットを、割込みマスクビットとして使用    |

| 1     | C C R の U I ビットを、ユーザビットとして使用 (初期値) |

### ビット 2：N M I エッジセレクト (N M I E G)

N M I 端子の入力エッジ選択を行います。

| ビット 2     | 説明                              |

|-----------|---------------------------------|

| N M I E G |                                 |

| 0         | N M I 入力の立下がりエッジで割込み要求を発生 (初期値) |

| 1         | N M I 入力の立上がりエッジで割込み要求を発生       |

### ビット 1：リザーブビット

リザーブビットです。リードすると常に “1” が読み出されます。ライトは無効です。

#### ビット0：RAMイネーブル（RAME）

内蔵RAMの有効／無効を選択します。RAMEビットは、RES端子の立上がりエッジでイニシャライズされます。ソフトウェアスタンバイモードでは、イニシャライズされません。

| ビット0 | 説明               |

|------|------------------|

| RAME |                  |

| 0    | 内蔵RAM無効          |

| 1    | 内蔵RAM有効<br>(初期値) |

### 3.4 各動作モードの説明

#### 3.4.1 モード1

ポート1、2、5の機能がアドレス端子A<sub>19</sub>～A<sub>0</sub>となり、最大1Mバイトのアドレス空間をアクセスできます。リセット直後は8ビットバスモードとなり、すべてのエリアは8ビットアクセス空間となります。ただし、ABWCRにより少なくとも1つのエリアを16ビットアクセス空間に設定した場合には、16ビットバスモードとなります。

#### 3.4.2 モード2

ポート1、2、5の機能がアドレス端子A<sub>19</sub>～A<sub>0</sub>となり、最大1Mバイトのアドレス空間をアクセスできます。リセット直後は16ビットバスモードとなり、すべてのエリアは16ビットアクセス空間となります。ただし、ABWCRによりすべてのエリアを8ビットアクセス空間に設定した場合には、8ビットバスモードとなります。

#### 3.4.3 モード3

ポート1、2、5およびポートAの一部の機能がアドレス端子A<sub>23</sub>～A<sub>0</sub>となり、最大16Mバイトのアドレス空間をアクセスできます。バスモードはリセット直後に8ビットバスモードとなり、すべてのエリアは8ビットアクセス空間となります。ただし、ABWCRにより少なくとも1つのエリアを16ビットアクセス空間に設定した場合には、16ビットバスモードとなります。A<sub>23</sub>～A<sub>21</sub>は、バスリリースコントロールレジスタ(BRCR)のビット7～5に“0”をライトすると有効になります(本モードではA<sub>20</sub>は常に出力となります)。

#### 3.4.4 モード4

ポート1、2、5およびポートAの一部の機能がアドレス端子A<sub>23</sub>～A<sub>0</sub>となり、最大16Mバイトのアドレス空間をアクセスできます。バスモードはリセット直後に16ビットバスモードとなり、すべてのエリアは16ビットアクセス空間となります。ただし、ABWCRによりすべてのエリアを8ビットアクセス空間に設定した場合には、8ビットバスモードとなります。A<sub>23</sub>～A<sub>21</sub>は、BRCRのビット7～5に“0”をライトすると有効になります(本モードではA<sub>20</sub>は常に出力となります)。

### 3.4.5 モード5

ポート1、2、5の機能がアドレス端子A<sub>19</sub>～A<sub>0</sub>となり、最大1Mバイトのアドレス空間をアクセスできます。リセット直後は入力ポートになっています。したがってアドレスバスとして使用する場合は各々の対応するデータディレクションレジスタ(P1DDR、P2DDR、P5DDR)を“1”にセットして、ポート1、2、5を出力に設定してください。バスモードはリセット直後に、8ビットバスモードとなり、すべてのエリアは8ビットアクセス空間となります。ただし、ABWCRにより、少なくとも1つのエリアを16ビットアクセス空間に設定した場合には、16ビットバスモードとなります。

### 3.4.6 モード6

ポート1、2、5およびポートAの一部の機能がアドレス端子A<sub>23</sub>～A<sub>0</sub>となり、最大16Mバイトのアドレス空間をアクセスできます。リセット直後は入力ポートになっています。したがってポート1、2、5をアドレスバスとして使用する場合は、各々の対応するデータディレクションレジスタ(P1DDR、P2DDR、P5DDR)を“1”にセットして、ポート1、2、5を出力に設定してください。また、A<sub>23</sub>～A<sub>21</sub>を出力する場合には、BRCRのビット7～5に“0”をライトしてください(本モードではA<sub>20</sub>は常に出力となります)。

バスモードはリセット直後に、8ビットバスモードとなり、すべてのエリアは8ビットアクセス空間となります。ただし、ABWCRにより、少なくとも1つのエリアを16ビットアクセス空間に設定した場合には、16ビットバスモードとなります。

### 3.4.7 モード7

内蔵ROMとRAM、内部I/Oレジスタで動作するモードです。すべてのポートを使用することができます。

モード7はアドレス空間が1Mバイトとなります。

### 3.5 各動作モードにおける端子機能

動作モードによりポート1～5、およびポートAの端子機能が切り換わります。各動作モードにおける端子機能の一覧を表3.3に示します。

表3.3 各動作モードにおけるポート1～5、およびポートAの機能

| ポート  | モード1                                            | モード2                                          | モード3                                                             | モード4                                                             | モード5                                            | モード6                                                             | モード7                             |

|------|-------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------|----------------------------------|

| ポート1 | A <sub>7</sub> ～A <sub>0</sub>                  | A <sub>7</sub> ～A <sub>0</sub>                | A <sub>7</sub> ～A <sub>0</sub>                                   | A <sub>7</sub> ～A <sub>0</sub>                                   | P1 <sub>7</sub> ～P1 <sub>0</sub> * <sup>2</sup> | P1 <sub>7</sub> ～P1 <sub>0</sub> * <sup>2</sup>                  | P1 <sub>7</sub> ～P1 <sub>0</sub> |

| ポート2 | A <sub>15</sub> ～A <sub>8</sub>                 | A <sub>15</sub> ～A <sub>8</sub>               | A <sub>15</sub> ～A <sub>8</sub>                                  | A <sub>15</sub> ～A <sub>8</sub>                                  | P2 <sub>7</sub> ～P2 <sub>0</sub> * <sup>2</sup> | P2 <sub>7</sub> ～P2 <sub>0</sub> * <sup>2</sup>                  | P2 <sub>7</sub> ～P2 <sub>0</sub> |

| ポート3 | D <sub>15</sub> ～D <sub>8</sub>                 | D <sub>15</sub> ～D <sub>8</sub>               | D <sub>15</sub> ～D <sub>8</sub>                                  | D <sub>15</sub> ～D <sub>8</sub>                                  | D <sub>15</sub> ～D <sub>8</sub>                 | D <sub>15</sub> ～D <sub>8</sub>                                  | P3 <sub>7</sub> ～P3 <sub>0</sub> |

| ポート4 | P4 <sub>7</sub> ～P4 <sub>0</sub> * <sup>1</sup> | D <sub>7</sub> ～D <sub>0</sub> * <sup>1</sup> | P4 <sub>7</sub> ～P4 <sub>0</sub> * <sup>1</sup>                  | D <sub>7</sub> ～D <sub>0</sub> * <sup>1</sup>                    | P4 <sub>7</sub> ～P4 <sub>0</sub> * <sup>1</sup> | P4 <sub>7</sub> ～P4 <sub>0</sub> * <sup>1</sup>                  | P4 <sub>7</sub> ～P4 <sub>0</sub> |

| ポート5 | A <sub>19</sub> ～A <sub>16</sub>                | A <sub>19</sub> ～A <sub>16</sub>              | A <sub>19</sub> ～A <sub>16</sub>                                 | A <sub>19</sub> ～A <sub>16</sub>                                 | P5 <sub>3</sub> ～P5 <sub>0</sub> * <sup>2</sup> | P5 <sub>3</sub> ～P5 <sub>0</sub> * <sup>2</sup>                  | P5 <sub>3</sub> ～P5 <sub>0</sub> |

| ポートA | PA <sub>7</sub> ～PA <sub>4</sub>                | PA <sub>7</sub> ～PA <sub>4</sub>              | PA <sub>7</sub> ～PA <sub>6</sub> * <sup>3</sup> 、A <sub>20</sub> | PA <sub>7</sub> ～PA <sub>6</sub> * <sup>3</sup> 、A <sub>20</sub> | PA <sub>7</sub> ～PA <sub>4</sub>                | PA <sub>7</sub> ～PA <sub>6</sub> 、A <sub>20</sub> * <sup>3</sup> | PA <sub>7</sub> ～PA <sub>4</sub> |

【注】\*<sup>1</sup> 初期状態を示しています。ABWCRの設定により、バスモードを切り替えることができます。8ビットモード時にはP4<sub>7</sub>～P4<sub>0</sub>に、16ビットバスモード時にはD<sub>7</sub>～D<sub>0</sub>となります。

\*<sup>2</sup> 初期状態を示しています。各々対応するデータディレクションレジスタ(P1DDR、P2DDR、P5DDR)を“1”に設定することにより、アドレスバスとなります。

\*<sup>3</sup> 初期状態を示しています。A<sub>20</sub>は常にアドレス出力です。PA<sub>7</sub>～PA<sub>6</sub>は、BRCRのビット7～5に“0”をライトすることによりA<sub>20</sub>～A<sub>21</sub>出力になります。

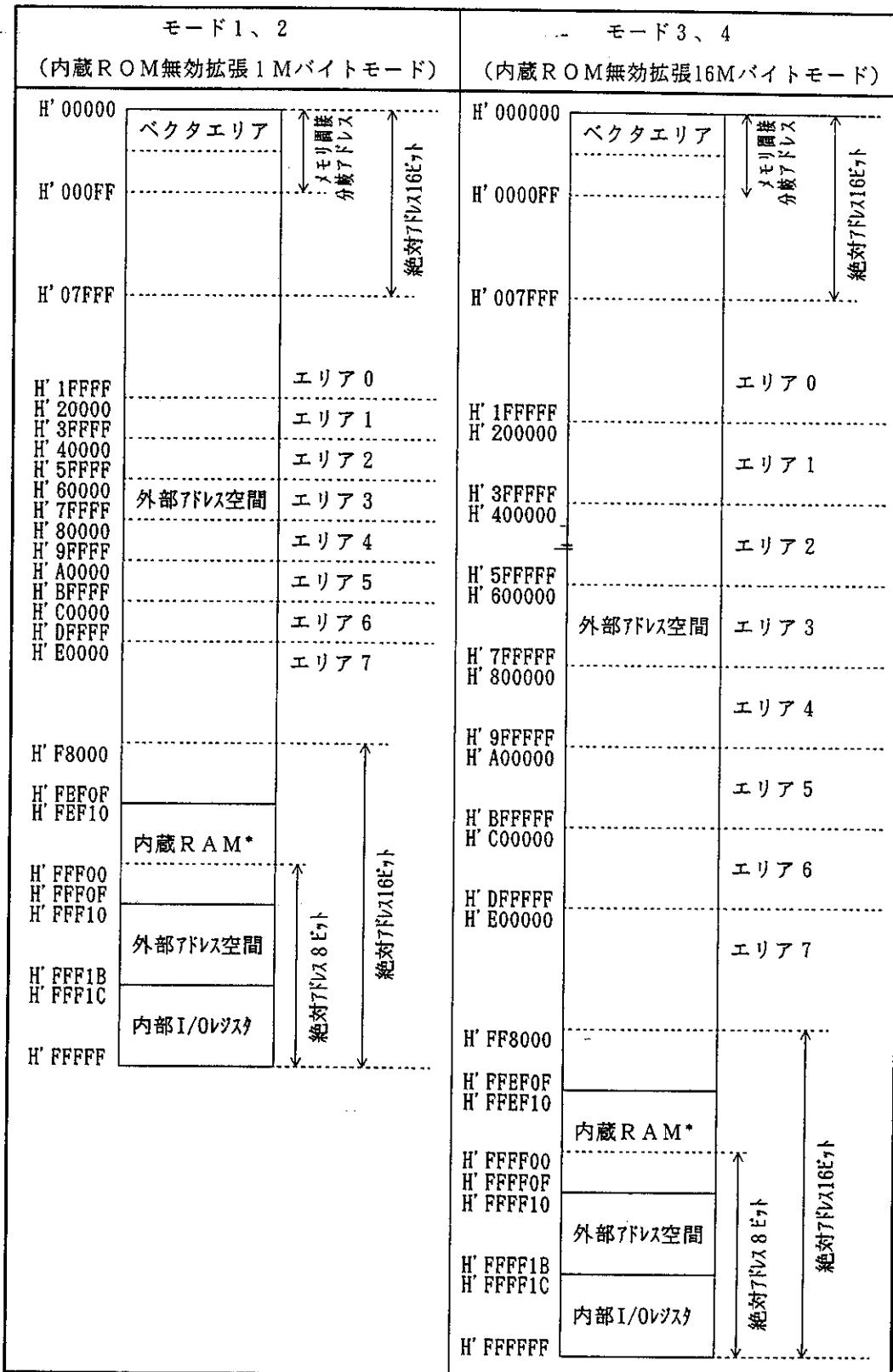

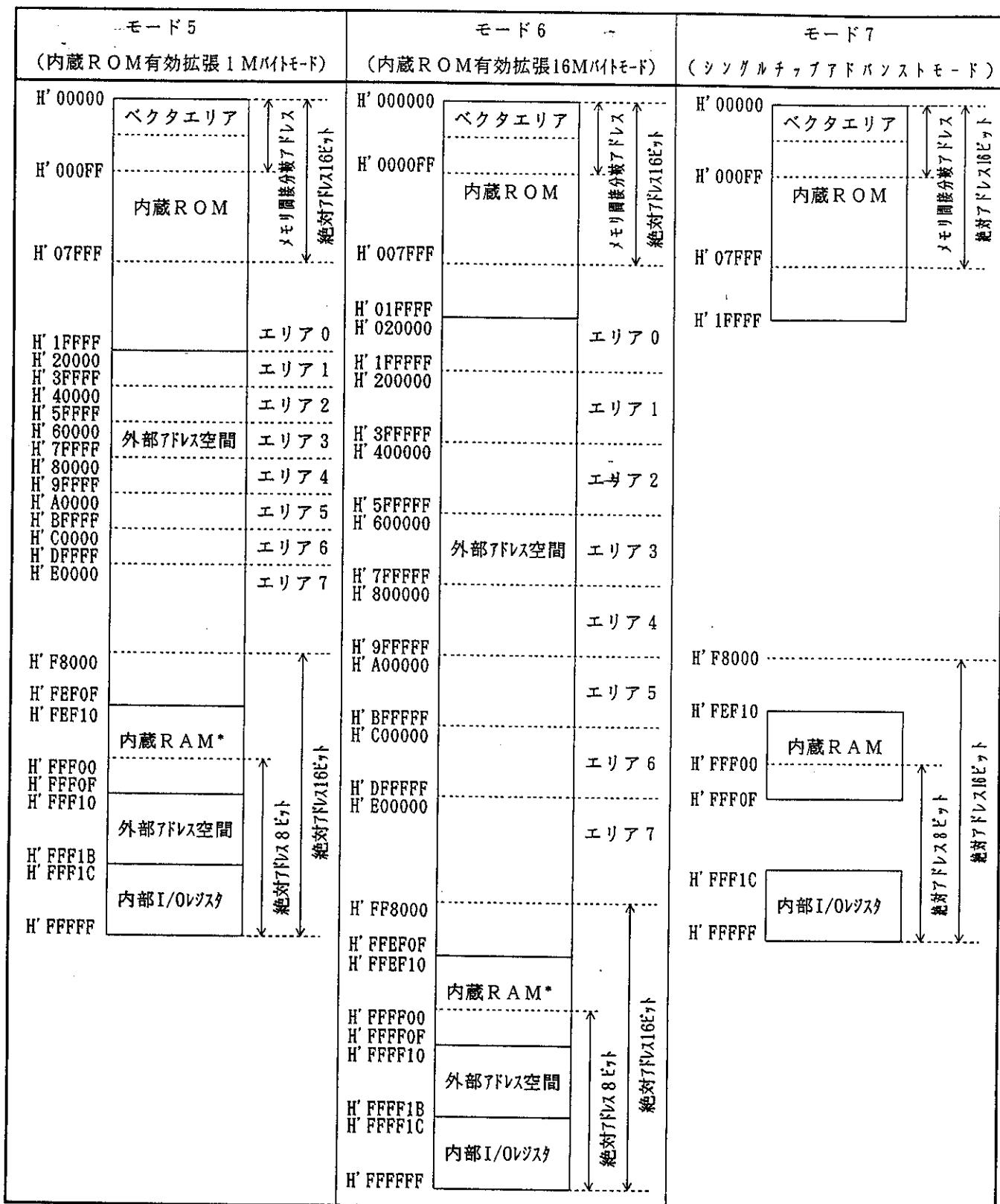

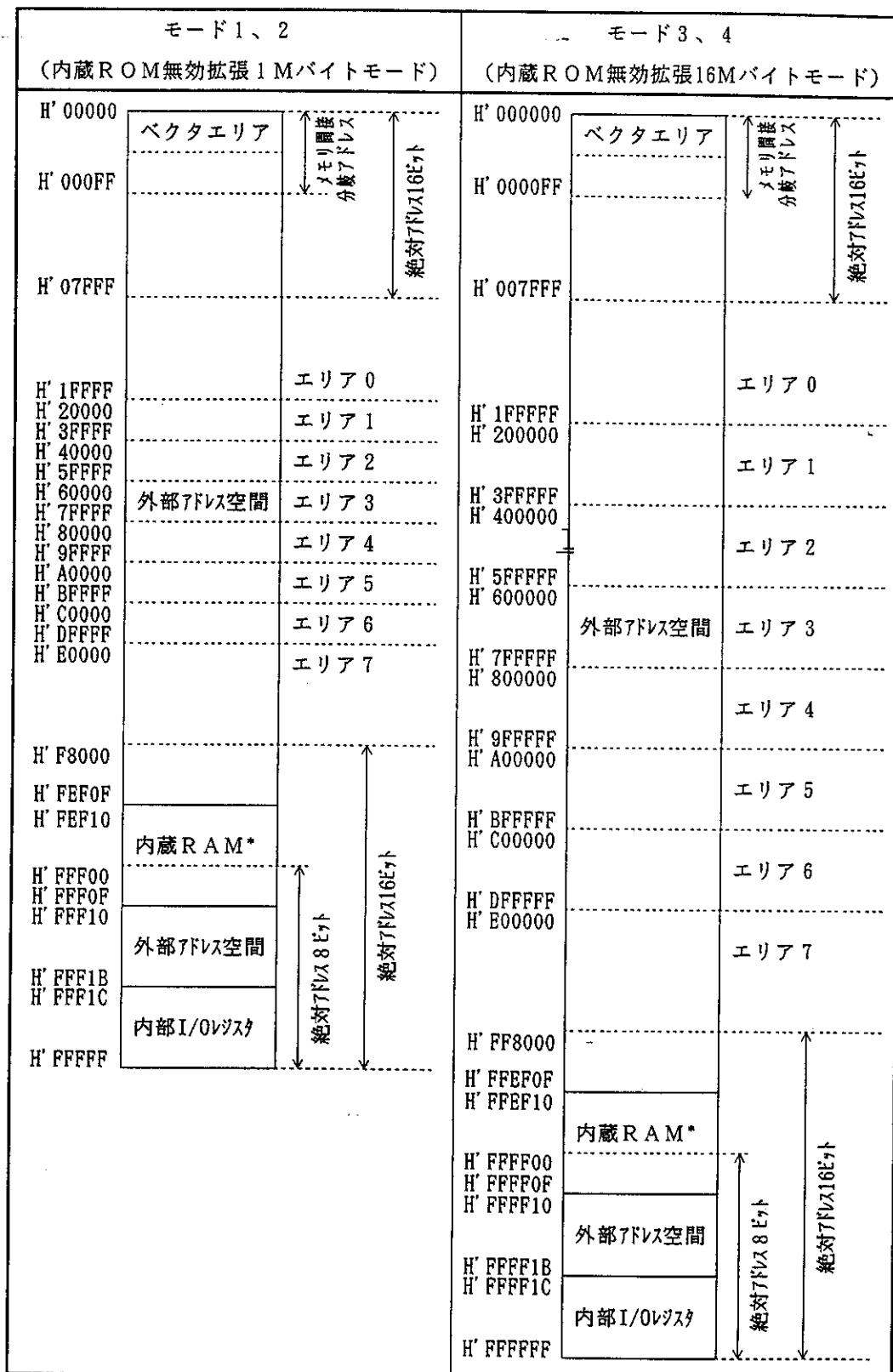

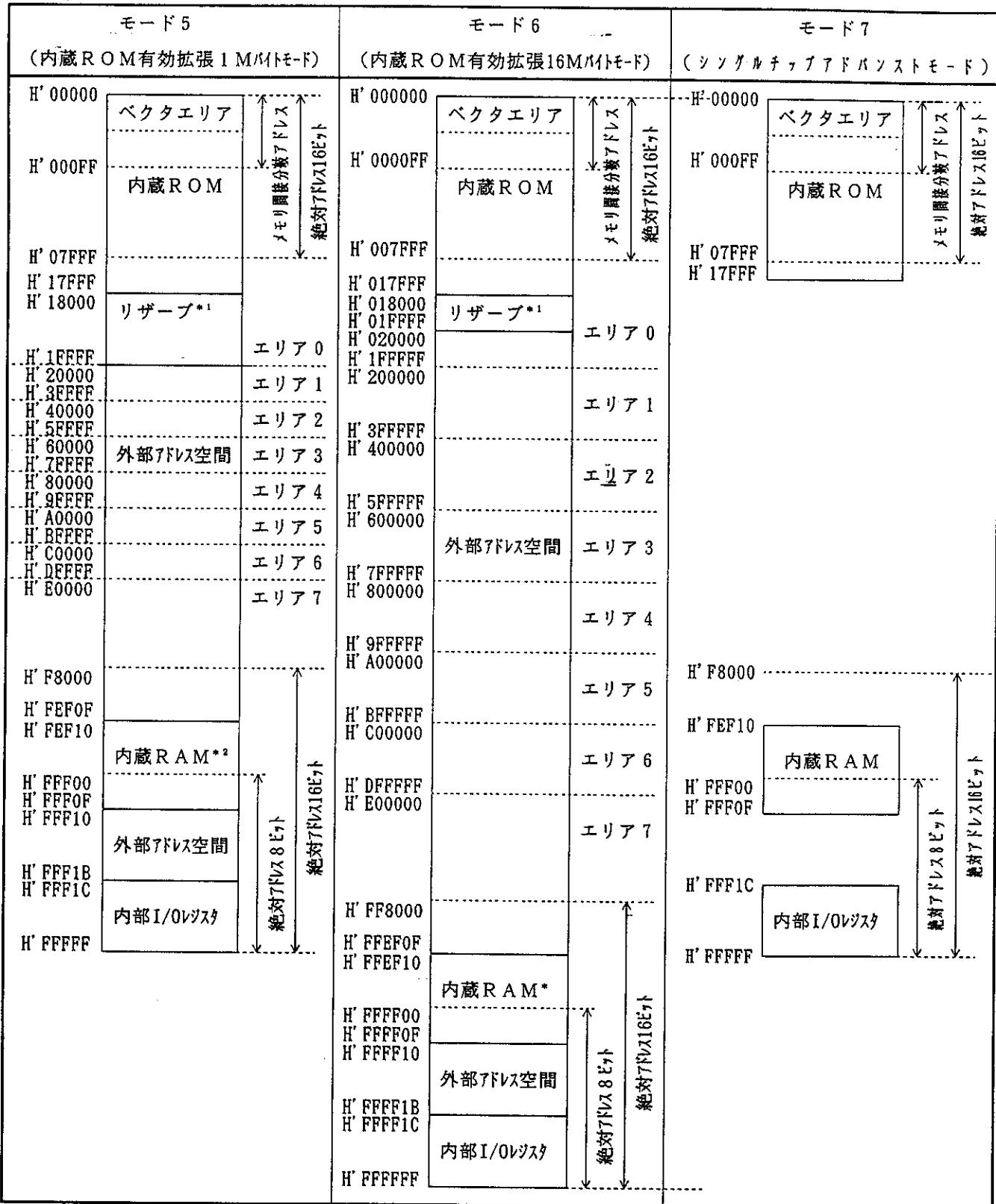

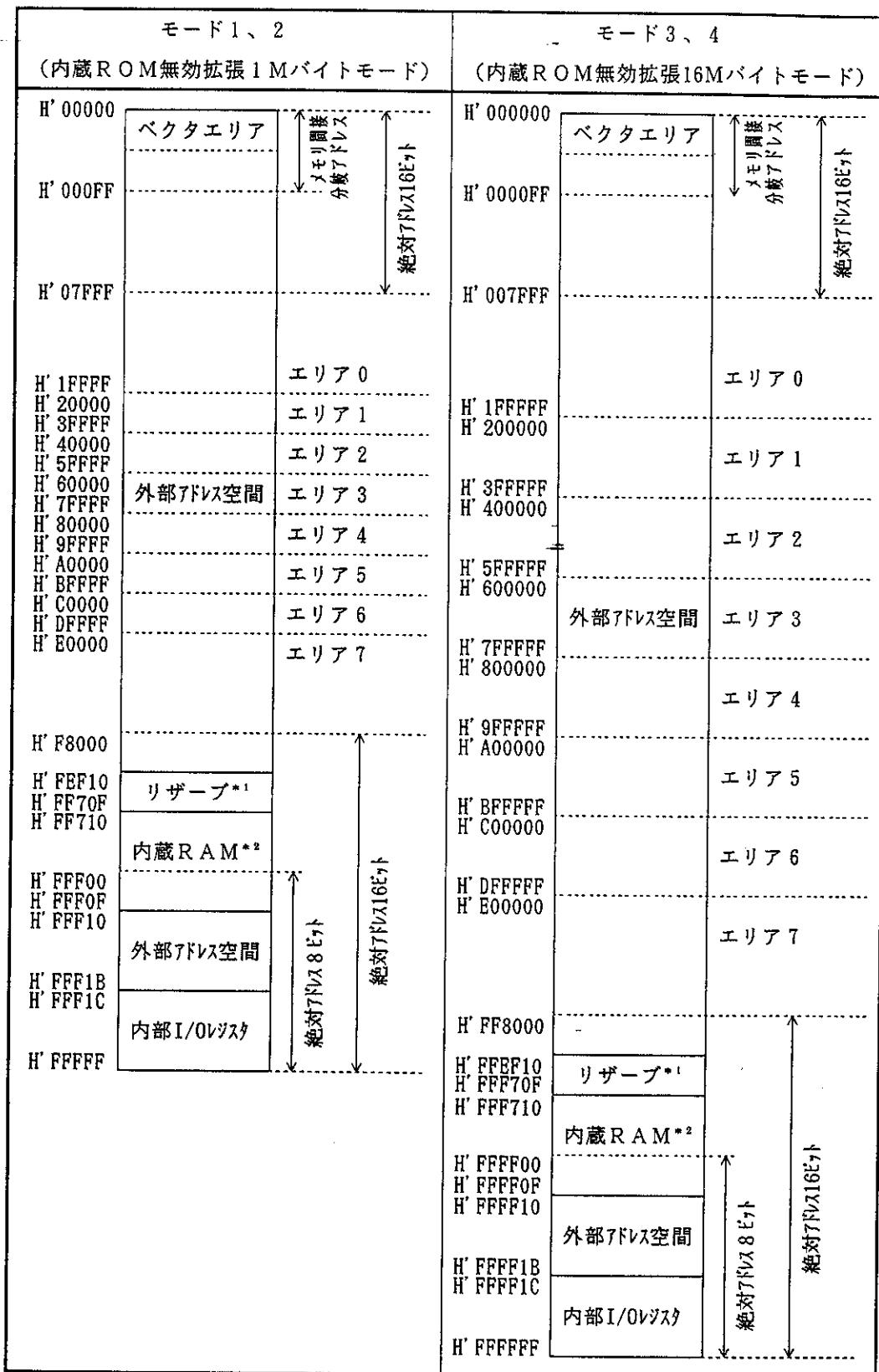

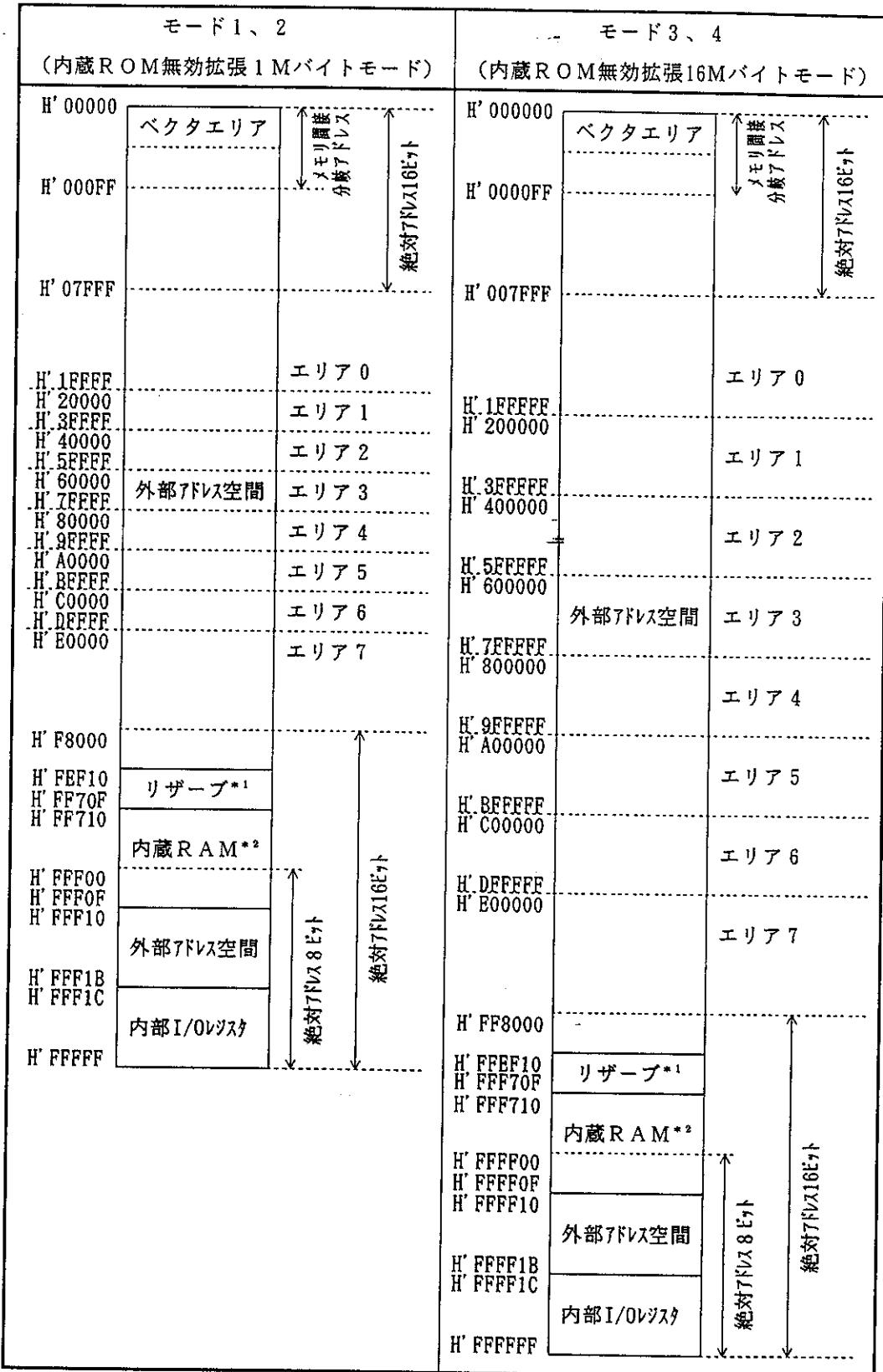

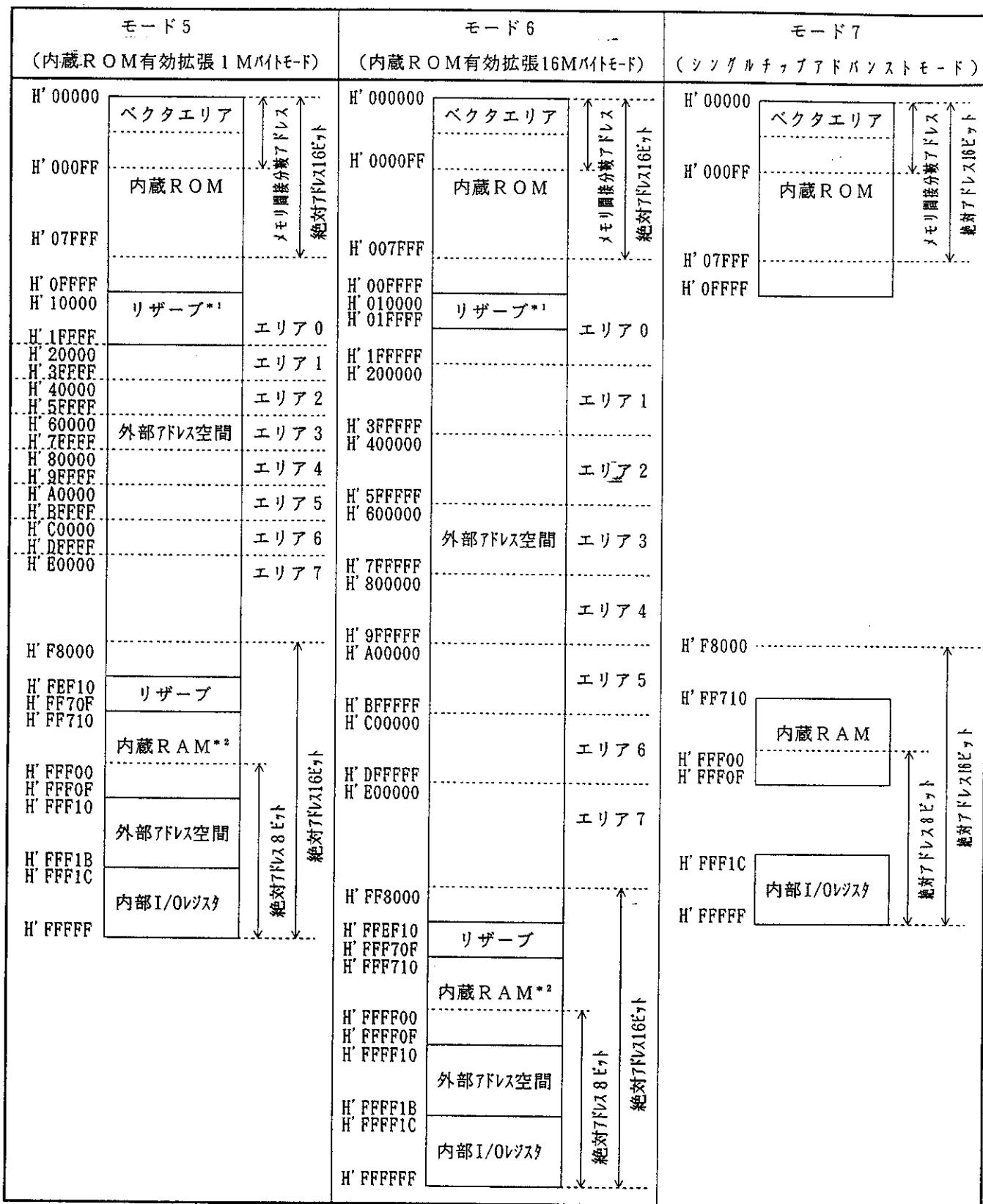

### 3.6 各動作モードのメモリマップ

H8/3048のメモリマップを図3.1に、H8/3047のメモリマップを図3.2に

H8/3044のメモリマップを図3.3に、H8/3045のメモリマップを図3.4に示します。

アドレス空間は8エリアに分割されています。 モード1とモード2、モード3とモード4ではそれぞれバスモードの初期状態が異なります。

また、モード1、2、5、7（1Mバイトモード）とモード3、4、6（16Mバイトモード）で、

内蔵RAMおよび内部I/Oレジスタの配置が異なります。また、CPUのアドレッシングモード

のうち、絶対アドレス8ビット／16ビット(@aa:8/@aa:16)で指定できる範囲が異なります。

【注】\* 内蔵RAMをディスエーブルにすると外部アドレス空間になります。

図3.1 H8/3048の各動作モードにおけるメモリマップ(1)

【注】\* 内蔵RAMをディスエーブルにすると外部アドレス空間になります。

図3.1 H8/3048の各動作モードにおけるメモリマップ(2)

【注】\* 内蔵RAMをディスエーブルにすると外部アドレス空間になります。

図3.2 H8/3047の各動作モードにおけるメモリマップ(1)

【注】<sup>\*1</sup> リザーブ領域はアクセスしないでください。

<sup>\*2</sup> 内蔵RAMをディスエーブルにすると外部アドレス空間になります。

図3.2 H8/3047の各動作モードにおけるメモリマップ(2)

【注】<sup>\*1</sup> リザーブ領域はアクセスしないでください。

<sup>\*2</sup> 内蔵RAMをディスエーブルにすると外部アドレス空間になります。

図3.3 H8/3044の各動作モードにおけるメモリマップ(1)

【注】<sup>\*1</sup> リザーブ領域はアクセスしないでください。

<sup>\*2</sup> 内蔵RAMをディスエーブルにすると外部アドレス空間になります。

図3.3 H8/3044の各動作モードにおけるメモリマップ(2)

【注】<sup>\*1</sup> リザーブ領域はアクセスしないでください。

<sup>\*2</sup> 内蔵RAMをディスエーブルにすると外部アドレス空間になります。

図3.4 H8/3045の各動作モードにおけるメモリマップ(1)

【注】<sup>\*1</sup> リザーブ領域はアクセスしないでください。

\*<sup>2</sup> 内蔵RAMをディスエーブルになると外部アドレス空間になります。

図3.4 H8/3045の各動作モードにおけるメモリマップ(2)