# 4. 例外処理

## 第4章 目次

|         |                 |    |

|---------|-----------------|----|

| 4. 1    | 概要              | 89 |

| 4. 1. 1 | 例外処理の種類と優先度     | 89 |

| 4. 1. 2 | 例外処理の動作         | 89 |

| 4. 1. 3 | 例外処理要因とベクターテーブル | 89 |

| 4. 2    | リセット            | 91 |

| 4. 2. 1 | 概要              | 91 |

| 4. 2. 2 | リセットシーケンス       | 91 |

| 4. 2. 3 | リセット直後の割込み      | 95 |

| 4. 3    | 割込み             | 95 |

| 4. 4    | トラップ命令          | 96 |

| 4. 5    | 例外処理後のスタックの状態   | 96 |

| 4. 6    | スタック使用上の注意      | 97 |

## 4.1 概要

### 4.1.1 例外処理の種類と優先度

例外処理には、表4.1に示すように、リセット、トラップ命令、および割込みによるものがあります。これらの例外処理には表4.1に示すように優先度が設けられており、複数の例外処理が同時に発生した場合は、この優先度に従って受け付けられ処理されます。トラップ命令例外処理は、プログラム実行状態で常に受け付けられます。

表4.1 例外処理の種類と優先度

| 優先度              | 例外処理の種類            | 例外処理開始タイミング                                |

|------------------|--------------------|--------------------------------------------|

| ↑<br>高<br>↓<br>低 | リセット               | RES端子が“Low”レベルから“High”レベルに変化すると、ただちに開始します。 |

|                  | 割込み                | 割込み要求が発生すると、命令の実行終了時または例外処理終了時に開始します。      |

|                  | トラップ命令<br>(TRAP A) | トラップ(TRAP A)命令の実行により開始します。                 |

### 4.1.2 例外処理の動作

例外処理は、各例外処理要因により起動されます。

トラップ命令および割込み例外処理は、次のように動作します。

- (1) プログラムカウンタ(PC)とコンディションコードレジスタ(CCR)をスタックに退避します。

- (2) CCRの割込みマスクビットを“1”にセットします。

- (3) 起動要因に対応するベクタアドレスを生成し、そのベクタアドレスの内容が示す番地からプログラムの実行が開始されます。

リセット例外処理の場合は上記(2)、(3)の動作を行います。

### 4.1.3 例外処理要因とベクタテーブル

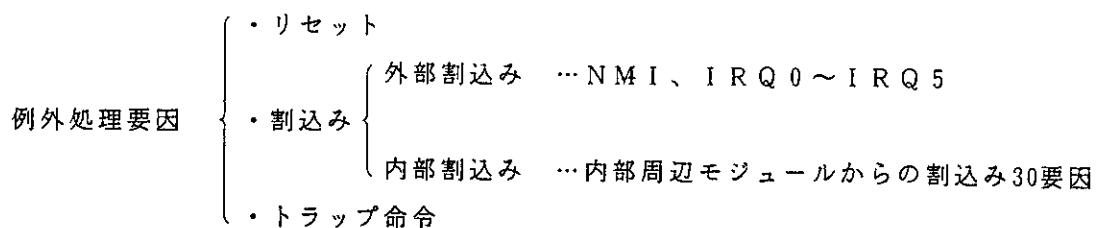

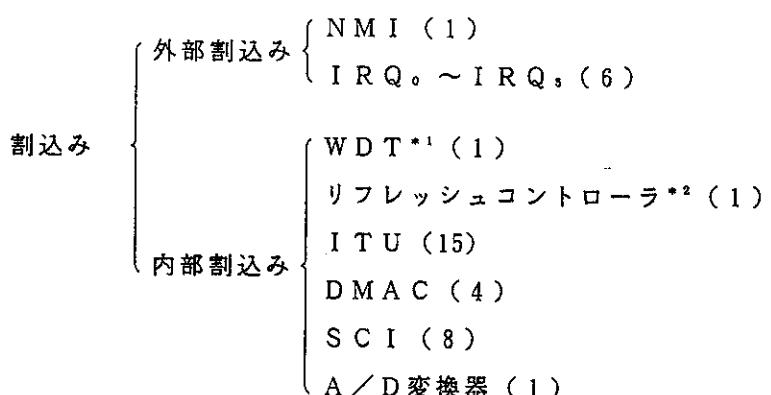

各例外処理要因は、図4.1に示すように分類されます。

これらの例外処理要因には、それぞれ異なるベクタアドレスが割り当てられています。

これらの要因とベクタアドレスとの対応を表4.2に示します。

図 4.1 例外処理要因

表 4.2 例外処理ベクターテーブル

| 例外処理要因              | ベクタ番号            | ベクタアドレス*      |

|---------------------|------------------|---------------|

| リセット<br>システム予約      | 0                | H'0000~H'0003 |

|                     | 1                | H'0004~H'0007 |

|                     | 2                | H'0008~H'000B |

|                     | 3                | H'000C~H'000F |

|                     | 4                | H'0010~H'0013 |

|                     | 5                | H'0014~H'0017 |

|                     | 6                | H'0018~H'001B |

| 外部割込み N M I         | 7                | H'001C~H'001F |

| トラップ命令<br>(4要因)     | 8                | H'0020~H'0023 |

|                     | 9                | H'0024~H'0027 |

|                     | 10               | H'0028~H'002B |

|                     | 11               | H'002C~H'002F |

|                     |                  |               |

| 外部割込み               | IRQ <sub>0</sub> | 12            |

|                     | IRQ <sub>1</sub> | 13            |

|                     | IRQ <sub>2</sub> | 14            |

|                     | IRQ <sub>3</sub> | 15            |

|                     | IRQ <sub>4</sub> | 16            |

|                     | IRQ <sub>5</sub> | 17            |

| システム予約              | 18               | H'0048~H'004B |

|                     | 19               | H'004C~H'004F |

| 内部割込み* <sup>2</sup> | 20               | H'0050~H'0053 |

|                     | 5                | 5             |

|                     | 60               | H'00F0~H'00F3 |

【注】\*1 アドレスの下位16ビットを示しています。

\*<sup>2</sup> 内部割込みのベクタテーブルは、「5.3.3 割込み例外処理ベクタテーブル」を参照してください。

## 4.2 リセット

### 4.2.1 概要

リセットは、最も優先順位の高い例外処理です。

RES端子が“Low”レベルになると、実行中の処理はすべて打ち切られ、本LSIはリセット状態になります。リセットによって、CPUの内部状態と内蔵周辺モジュールの各レジスタがイニシャライズされます。

RES端子が“Low”レベルから“High”レベルになるとリセット例外処理が開始されます。

ウォッチドッグタイマのオーバフローによって、リセット状態とすることもできます。詳細は、「第12章 ウォッチドッグタイマ」を参照してください。

### 4.2.2 リセットシーケンス

RES端子が“Low”レベルになると本LSIはリセット状態になります。

本LSIを確実にリセットするためには、電源投入時は最低20msの間、RES端子を“Low”レベルに保持してください。また、動作中は最低10システムクロック(φ)サイクルの間“Low”レベルにしてください。リセット状態の各端子の状態は「付録D.2 リセット時の端子状態」を参照してください。

RES端子が一定期間“Low”レベルの後、“High”レベルになるとリセット例外処理が開始され、本LSIは次のように動作します。

- (1) CPUの内部状態と内蔵周辺モジュールの各レジスタがイニシャライズされ、CCRのIビットが“1”にセットされます。

- (2) リセット例外処理ベクタアドレス(H'0000～H'0003)をリードして、そのベクタアドレスの内容が示すアドレスからプログラムの実行を開始します。

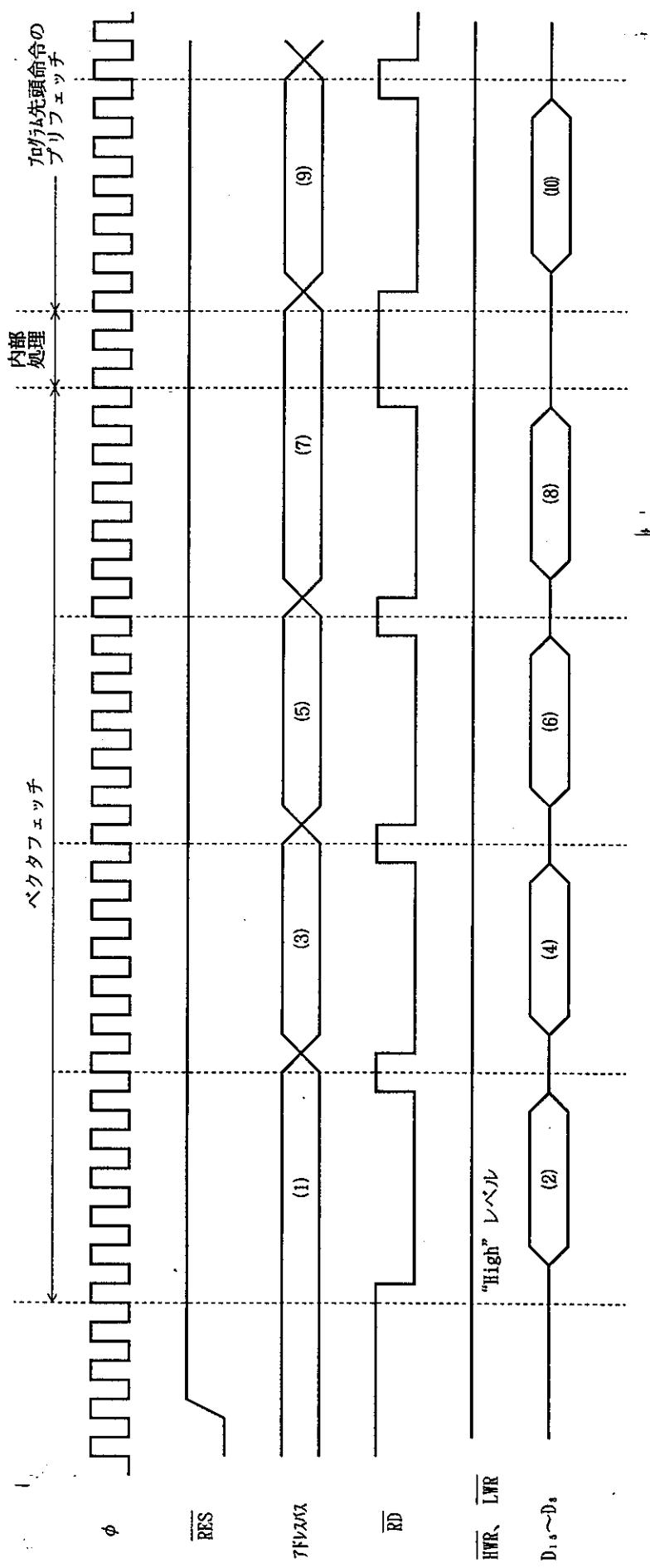

モード1、3のリセットシーケンスを図4.2に、モード2、4のリセットシーケンスを図4.3に、モード6のリセットシーケンスを図4.4に示します。

(1)(3)(5)(7) リセット例外処理ベクタアドレス ((1)=H' 00000、(3)=H' 00001、(5)=H' 00002、(7)=H' 00003)

(2)(4)(6)(8) スタートアドレス (リセット例外処理ベクタアドレスの内容)

(9) スタートアドレス

(10) プログラム先頭命令

【注】 リセット後は、ウェイットステートコントローラによって、3ステートのウェイットステートが、各バスサイクルに挿入されます。

図4.2 リセットシーケンス (モード1、3)

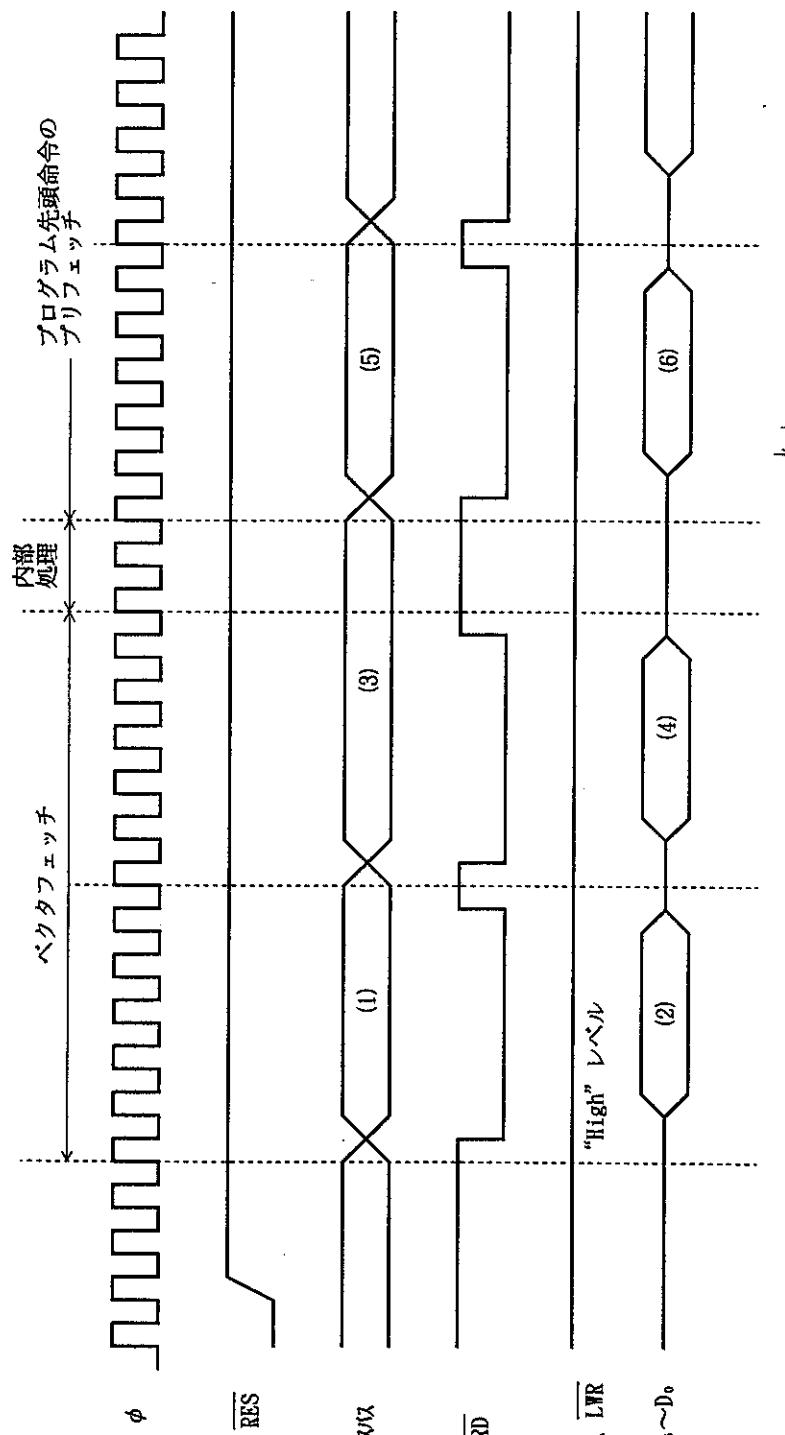

- (1)(3) リセット例外処理ベクタアドレス ((1)=FF'000000、(3)=FF'000002)

(2)(4) スタートアドレス (リセット例外処理ベクタアドレスの内容)

(5) スタートアドレス

(6) プログラム先頭命令

【注】 リセット後は、ウェイトステートコントローラによって、3ステートのウェイトステートが、各バスサイクルに挿入されます。

図4.3 リセットシーケンス (モード2、4)

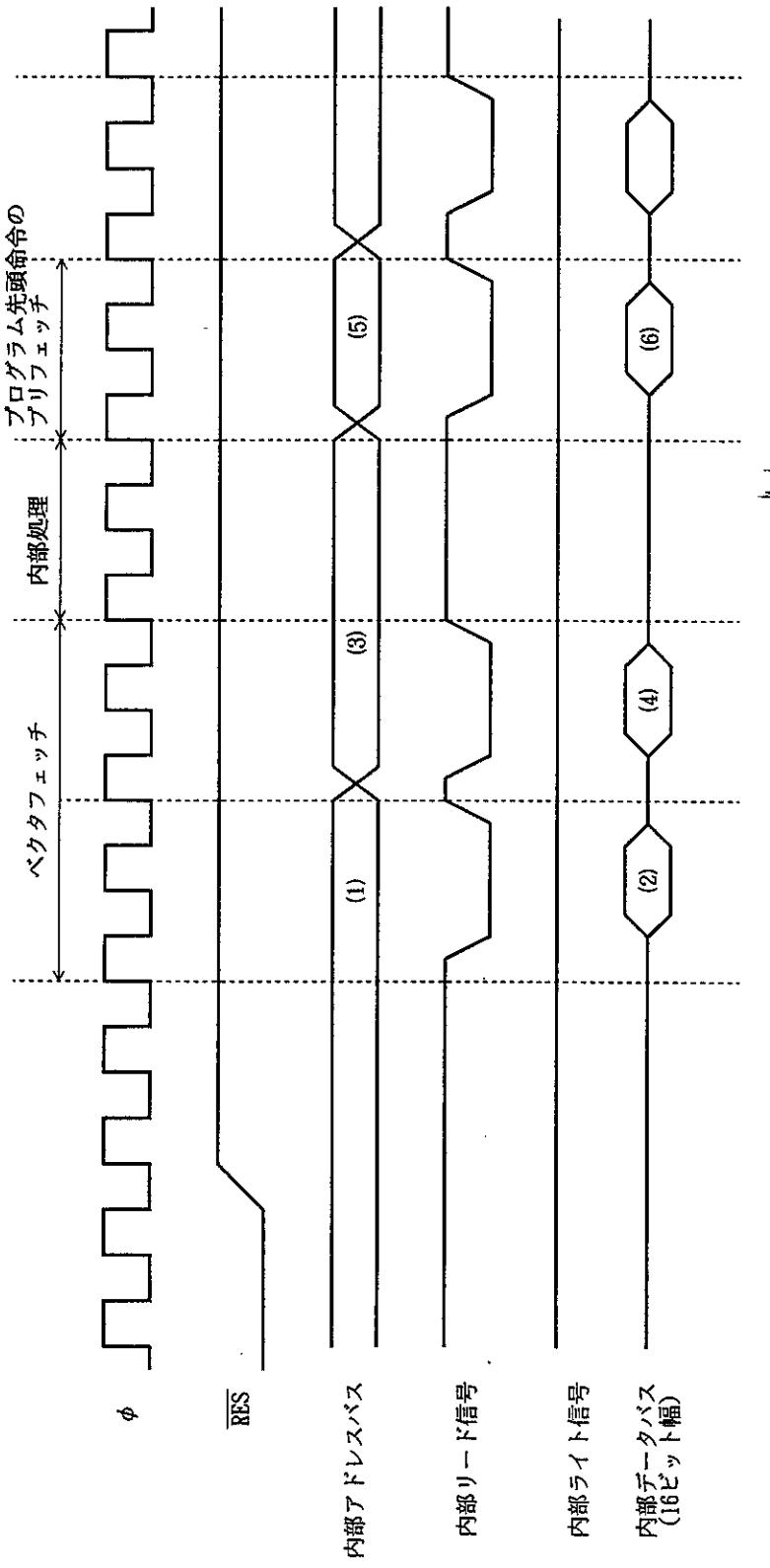

- (1)(3) リセット例外処理ベクタアドレス ((1)=H'0000000 (2)=H'0000002)

(2)(4) スタートアドレス (リセット例外処理ベクタアドレスの内容)

(5) スタートアドレス

(6) プログラム先頭命令

図4.4 リセットシーケンス (モード5、6、7)

#### 4.2.3 リセット直後の割込み

リセット直後、スタックポインタ (S P) をイニシャライズする前に割込みを受け付けると、P CとCCRの退避が正常に行われないため、プログラムの暴走につながります。これを防ぐため、リセット例外処理が実行された直後は、N M Iを含めたすべての割込み要求が禁止されます。すなわち、リセット直後はプログラムの先頭1命令が必ず実行されますので、プログラム先頭命令はS Pをイニシャライズする命令としてください（例：M O V, L # x x : 32, S P）。

### 4.3 割込み

割込み例外処理を開始させる要因には、7つの外部割込み (N M I、I R Q<sub>0</sub>～I R Q<sub>6</sub>) と、内蔵周辺モジュールからの要求による30の内部要因があります。割込み要因と要因数を図4.5に示します。

割込み要因を要求する内蔵周辺モジュールには、ウォッチドッグタイマ (W D T)、リフレッシュコントローラ、16ビットインテグレーテッドタイマエンジット (I T U)、DMAコントローラ (D M A C)、シリアルコミュニケーションインターフェース (S C I)、およびA/D変換器があります。割込みベクタアドレスは、各要因別に割り当てられています。

N M Iは最優先の割込みで、常に受け付けられます。割込みは、割込みコントローラによって制御されます。割込みコントローラは、N M I以外の割込みを2レベルの優先順位を設定して、多重割込みの制御を行うことができます。割込みの優先順位は、割込みコントローラのインタラプトブライオリティレジスタA、B (I P R A、B) に設定します。

割込みについての詳細は「第5章 割込みコントローラ」を参照してください。

【注】 ( ) 内は要因数を示します。

\*<sup>1</sup> W D Tをインターバルタイマとして使用したときは、カウンタがオーバフローすると割込み要求を発生します。

\*<sup>2</sup> リフレッシュコントローラをインターバルタイマとして使用したとき、コンペアマッチにより割込み要求を発生します。

図4.5 割込み要因と要因数

#### 4.4 ト ラ ッ プ 命 令

ト ラ ッ プ 命 令 例 外 处 理 は、 T R A P A 命 令 を 実 行 す る と 例 外 处 理 を 開 始 し ま す。

例 外 处 理 に よ っ て、 S Y S C R の U E ビ ッ ト が “1” の と き は C C R の I ビ ッ ト が “1” に セ ッ ト さ れ、 U E ビ ッ ト が “0” の と き に は C C R の I ビ ッ ト、 U I ビ ッ ト が そ れ ぞ れ “1” に セ ッ ト さ れ ま す。

T R A P A 命 令 は、 命 令 コ ー ド 中 で 指 定 し た 0 ~ 3 の ベ ク タ 番 号 に 対 応 す る ベ ク タ テ ー ブ ル か ら ス タ ー ト ア ド レ ス を 取 り 出 し ま す。

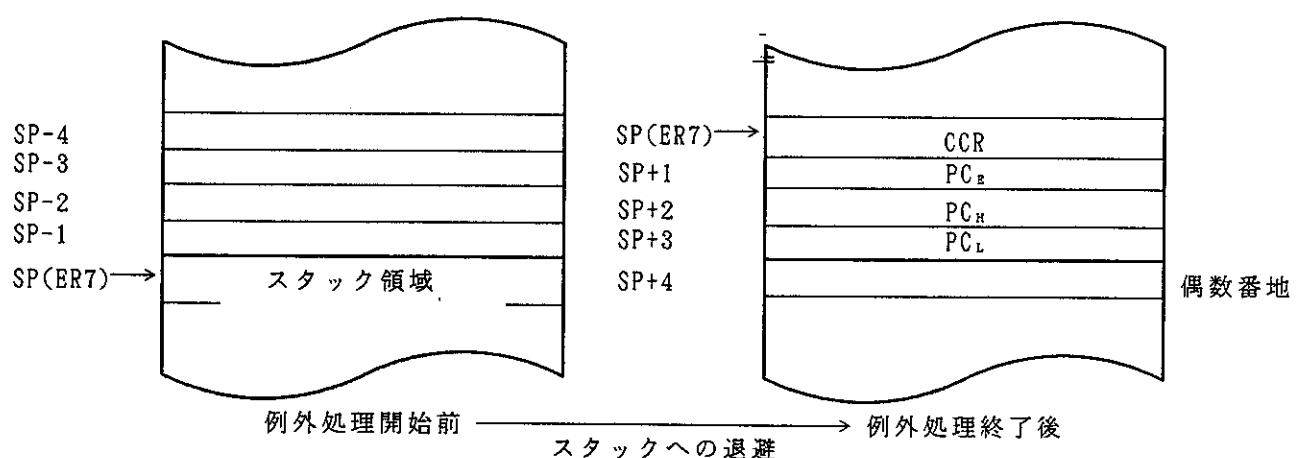

#### 4.5 例 外 处 理 後 の ス タ ッ ク の 状 態

ト ラ ッ プ 命 令 例 外 处 理 お よ び 割 込 み 例 外 处 理 後 の ス タ ッ ク 状 態 を 図 4.6 に 示 し ま す。

図 4.6 例 外 处 理 終 了 後 の ス タ ッ ク 状 態

##### 《記号説明》

|     |                                               |

|-----|-----------------------------------------------|

| PCE | プロ グ ラ ム カ ウ イ ナ タ (PC) の ビ ッ ト 23 ~ ビ ッ ト 16 |

| PCH | プロ グ ラ ム カ ウ イ ナ タ (PC) の ビ ッ ト 15 ~ ビ ッ ト 8  |

| PCL | プロ グ ラ ム カ ウ イ ナ タ (PC) の ビ ッ ト 7 ~ 0         |

| CCR | コン デ ィ シ ョ ナ コ ド レ ジ イ ス タ                    |

| SP  | ス タ ッ ク ポ イ ン タ                               |

- 【注】

1. PCはリターン後に実行する最初の命令のアドレスです。

2. レジスタの退避／復帰は必ずワードサイズまたはロングワードサイズで、偶数アドレスから行ってください。

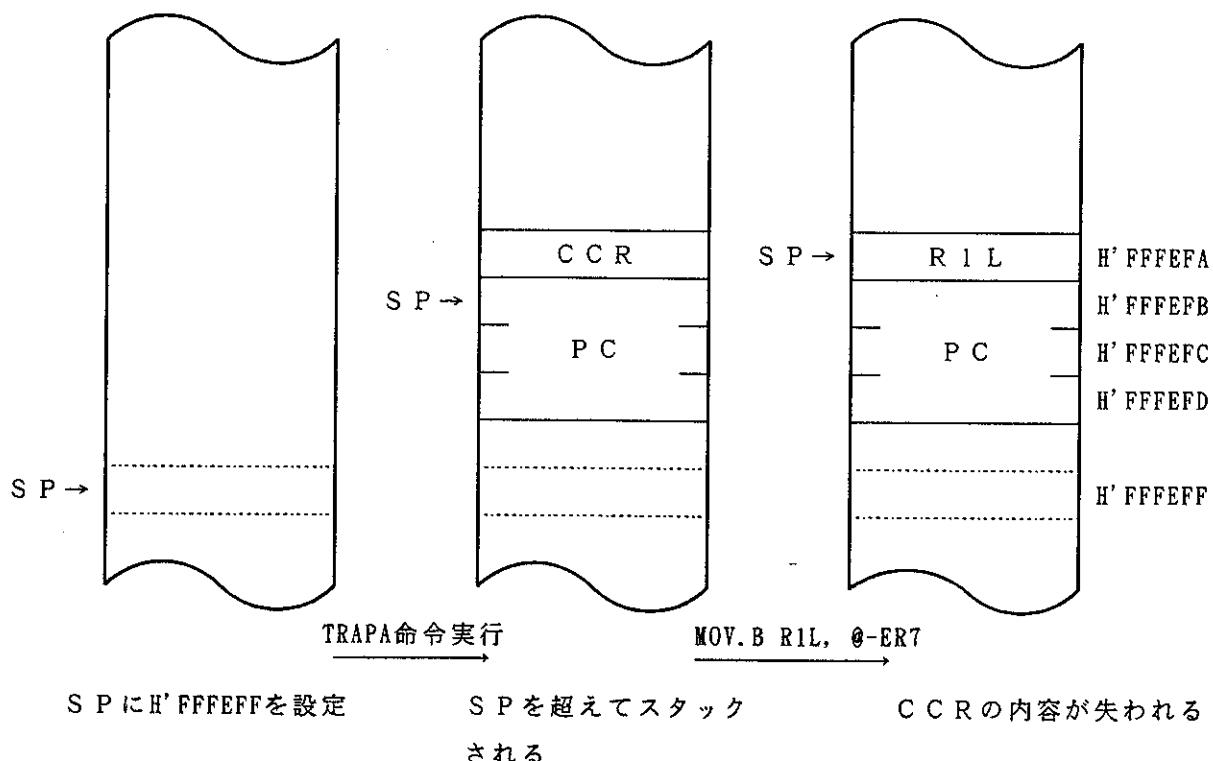

## 4.6 スタック使用上の注意

本LSIでは、ワードデータまたはロングワードデータをアクセスする場合は、アドレスの最下位ビットは0とみなされます。スタック領域に対するアクセスは、常にワードサイズまたはロングワードサイズで行い、スタックポインタ (SP : ER7) の内容は奇数にしないでください。すなわち、レジスタの退避は、

```

PUSH. W Rn (MOV. W Rn, @-SP)

PUSH. L ERn (MOV. L ERn, @-SP)

```

また、レジスタの復帰は、

```

POP. W Rn (MOV. W @SP+, Rn)

POP. L ERn (MOV. L @SP+, ERn)

```

を使用してください。

SPを奇数に設定すると、誤動作の原因となります。SPを奇数に設定した場合の動作例を図4.7に示します。

### 《記号説明》

CCR : コンディションコードレジスタ

PC : プログラムカウンタ

R1L : 汎用レジスタR1L

SP : スタックポインタ

【注】 モード3、4の場合です。

図4.7 SPを奇数に設定したときの動作