# 5. 割込みコントローラ

## 第5章 目次

|                                           |     |

|-------------------------------------------|-----|

| 5. 1 概要                                   | 101 |

| 5. 1. 1 特長                                | 101 |

| 5. 1. 2 ブロック図                             | 102 |

| 5. 1. 3 端子構成                              | 103 |

| 5. 1. 4 レジスタ構成                            | 103 |

| 5. 2 各レジスタの説明                             | 104 |

| 5. 2. 1 システムコントロールレジスタ (SYSCR)            | 104 |

| 5. 2. 2 インタラプトプライオリティレジスタ A、B (IPRA、IPRB) | 105 |

| 5. 2. 3 IRQステータスレジスタ (ISR)                | 112 |

| 5. 2. 4 IRQイネーブルレジスタ (IER)                | 113 |

| 5. 2. 5 IRQセンスコントロールレジスタ (ISCR)           | 114 |

| 5. 3 割込み要因                                | 115 |

| 5. 3. 1 外部割込み                             | 115 |

| 5. 3. 2 内部割込み                             | 116 |

| 5. 3. 3 割込み例外処理ベクターテーブル                   | 116 |

| 5. 4 割込み動作                                | 119 |

| 5. 4. 1 割込み動作の流れ                          | 119 |

| 5. 4. 2 割込み例外処理シーケンス                      | 125 |

| 5. 4. 3 割込み応答時間                           | 127 |

| 5. 5 使用上の注意                               | 128 |

| 5. 5. 1 割込み発生とディスエーブルとの競合                 | 128 |

| 5. 5. 2 割込みの受け付けを禁止している命令                 | 129 |

| 5. 5. 3 EEPMOV命令実行中の割込み                   | 129 |

| 5. 5. 4 外部割込み使用上の注意                       | 129 |

## 5.1 概要

### 5.1.1 特長

割込みコントローラには、次の特長があります。

#### ■ I P Rにより、優先順位を設定可能

割込み優先順位を設定するインタラプトプライオリティレジスタ A、B (I P R A、B) を備えており、N M I 以外の割込みを要因ごとまたはモジュールごとに 2 レベルの優先順位を設定できます。

#### ■ C P U のコンディションコードレジスタ (C C R) の I、U I ビットにより、3 レベルの許可／禁止状態を設定可能。

#### ■ 独立したベクタアドレス

すべての割込み要因には独立のベクタアドレスが割り当てられており、割込み処理ルーチンで要因を判別する必要がありません。

#### ■ 7 本の外部割込み端子

N M I は最優先の割込みで常に受け付けられます。N M I は立上がりエッジ／立下がりエッジを選択できます。また I R Q<sub>0</sub>～I R Q<sub>6</sub>は立下がりエッジ／レベルセンスを独立に選択できます。

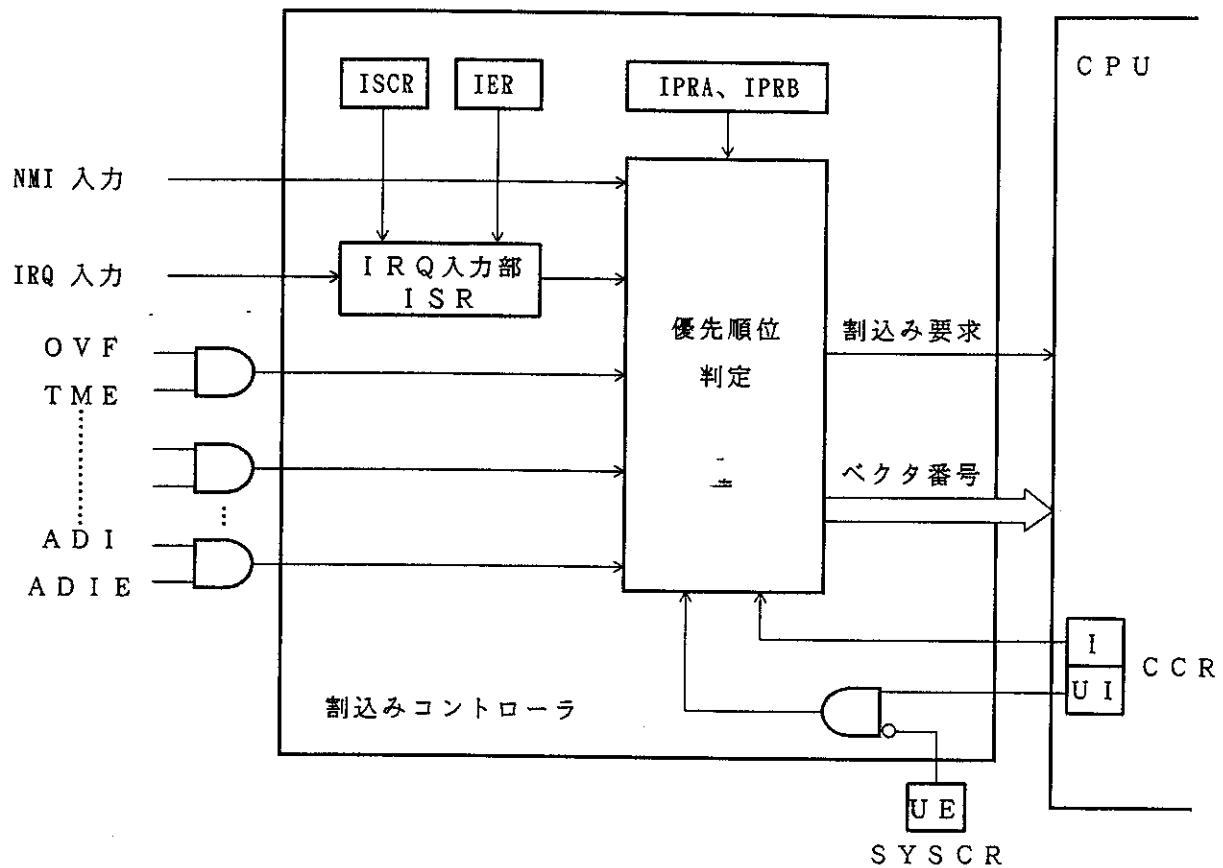

### 5.1.2 ブロック図

割込みコントローラのブロック図を図5.1に示します。

#### 《記号説明》

- I S C R : IRQ センスコントロールレジスタ

- I E R : IRQ イネーブルレジスタ

- I S R : IRQ ステータスレジスタ

- I P R A : インタラプトプライオリティレジスタ A

- I P R B : インタラプトプライオリティレジスタ B

- S Y S C R : システムコントロールレジスタ

図 5.1 割込みコントローラのブロック図

### 5.1.3 端子構成

割込みコントローラの端子構成を表5.1に示します。

表5.1 端子構成

| 名 称           | 略 称                                 | 入出力 | 機 能                              |

|---------------|-------------------------------------|-----|----------------------------------|

| ノンマスカブル割込み    | NMI                                 | 入力  | マスク不可能な外部割込み、立上がりエッジ/立下がりエッジ選択可能 |

| 外部割込み要求 5 ~ 0 | IRQ <sub>5</sub> ~ IRQ <sub>0</sub> | 入力  | マスク可能な外部割込み、立下がりエッジ/レベルセンス選択可能   |

### 5.1.4 レジスタ構成

割込みコントローラのレジスタ構成を表5.2に示します。

表5.2 レジスタ構成

| アドレス <sup>*1</sup> | 名 称                 | 略 称       | R/W                 | 初期値  |

|--------------------|---------------------|-----------|---------------------|------|

| H'FFF2             | システムコントロールレジスタ      | S Y S C R | R/W                 | H'0B |

| H'FFF4             | I R Q センスコントロールレジスタ | I S C R   | R/W                 | H'00 |

| H'FFF5             | I R Q イネーブルレジスタ     | I E R     | R/W                 | H'00 |

| H'FFF6             | I R Q ステータスレジスタ     | I S R     | R/(W) <sup>*2</sup> | H'00 |

| H'FFF8             | インタラプトプライオリティレジスタA  | I P R A   | R/W                 | H'00 |

| H'FFF9             | インタラプトプライオリティレジスタB  | I P R B   | R/W                 | H'00 |

【注】<sup>\*1</sup> アドレスの下位16ビットを示しています。

<sup>\*2</sup> フラグをクリアするための“0”ライトのみ可能です。

## 5.2 各レジスタの説明

### 5.2.1 システムコントロールレジスタ (SYSCR)

SYSCRは8ビットのリード／ライト可能なレジスタで、ソフトウェアスタンバイモードの制御、CCRのUIビットの動作の選択、NMIの検出エッジの選択、および内蔵RAMの有効／無効の選択を行います。

ここでは、ビット3、2についてのみ説明します。なお、その他のビットの詳細については「3.3 システムコントロールレジスタ (SYSCR)」を参照してください。

SYSCRはリセット、またはハードウェアスタンバイモード時にH'0Bにイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

| ビット: | 7    | 6    | 5    | 4    | 3                                                     | 2                      | 1       | 0        |

|------|------|------|------|------|-------------------------------------------------------|------------------------|---------|----------|

|      | SSBY | STS2 | STS1 | STS0 | UE                                                    | NMIEG                  | —       | RAME     |

| 初期値: | 0    | 0    | 0    | 0    | 1                                                     | 0                      | 1       | 1        |

| R/W: | R/W  | R/W  | R/W  | R/W  | R/W                                                   | R/W                    | —       | R/W      |

|      |      |      |      |      |                                                       |                        |         | RAMイネーブル |

|      |      |      |      |      |                                                       |                        | リザーブビット |          |

|      |      |      |      |      |                                                       | NMIエッジセレクト             |         |          |

|      |      |      |      |      |                                                       | NMI端子の入力エッジを選択するビットです。 |         |          |

|      |      |      |      |      | ユーザビットイネーブル                                           |                        |         |          |

|      |      |      |      |      | CCRのUIビットをユーザビットとして使用するか、割込みマスクビットとして使用するかを選択するビットです。 |                        |         |          |

|      |      |      |      |      | スタンバイタイマセレクト2~0                                       |                        |         |          |

|      |      |      |      |      | ソフトウェアスタンバイ                                           |                        |         |          |

**ビット3：ユーザビットイネーブル（UE）**

CCRのUIビットをユーザビットとして使用するか、割込みマスクビットとして使用するかを選択します。

| ビット3 | 説明                             |

|------|--------------------------------|

| UE   |                                |

| 0    | CCRのUIビットを割込みマスクビットとして使用       |

| 1    | CCRのUIビットをユーザビットとして使用<br>(初期値) |

**ビット2：NMIエッジセレクト（NMIEG）**

NMI端子の入力エッジ選択を行います。

| ビット2  | 説明                              |

|-------|---------------------------------|

| NMIEG |                                 |

| 0     | NMI入力の立下がりエッジで割込み要求を発生<br>(初期値) |

| 1     | NMI入力の立上がりエッジで割込み要求を発生          |

**5.2.2 インタラプトプライオリティレジスタA、B（IPRA、IPRB）**

IPRA、IPRBは各々8ビットのリード／ライト可能なレジスタで割込みの優先順位を制御します。

(1) インタラプトプライオリティレジスタA (IPRA)

IPRAは8ビットのリード/ライト可能なレジスタで、プライオリティレベルを設定できます。

ビット：

|  | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--|-------|-------|-------|-------|-------|-------|-------|-------|

|  | IPRA7 | IPRA6 | IPRA5 | IPRA4 | IPRA3 | IPRA2 | IPRA1 | IPRA0 |

初期値：

0 0 0 0 0 0 0 0

R/W：

R/W R/W R/W R/W R/W R/W R/W R/W

プライオリティレベルA0

ITUチャネル2の割込み要求のプライオリティレベルを設定するビットです。

プライオリティレベルA1

ITUチャネル1の割込み要求のプライオリティレベルを設定するビットです。

プライオリティレベルA2

ITUチャネル0の割込み要求のプライオリティレベルを設定するビットです。

プライオリティレベルA3

WDT、リフレッシュコントローラの割込み要求のプライオリティレベルを設定するビットです。

プライオリティレベルA4

IRQ<sub>4</sub>、IRQ<sub>5</sub>の割込み要求のプライオリティレベルを設定するビットです。

プライオリティレベルA5

IRQ<sub>2</sub>、IRQ<sub>3</sub>の割込み要求のプライオリティレベルを設定するビットです。

プライオリティレベルA6

IRQ<sub>1</sub>の割込み要求のプライオリティレベルを設定するビットです。

プライオリティレベルA7

IRQ<sub>0</sub>の割込み要求のプライオリティレベルを設定するビットです。

IPRAはリセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。

#### ビット7：プライオリティレベルA7 (IPRA7)

IRQ<sub>0</sub>の割込み要求のプライオリティレベルを設定します。

| ビット7  | 説                                        | 明     |

|-------|------------------------------------------|-------|

| IPRA7 |                                          |       |

| 0     | IRQ <sub>0</sub> の割込み要求はプライオリティレベル0（非優先） | （初期値） |

| 1     | IRQ <sub>0</sub> の割込み要求はプライオリティレベル1（優先）  |       |

#### ビット6：プライオリティレベルA6 (IPRA6)

IRQ<sub>1</sub>の割込み要求のプライオリティレベルを設定します。

| ビット6  | 説                                        | 明     |

|-------|------------------------------------------|-------|

| IPRA6 |                                          |       |

| 0     | IRQ <sub>1</sub> の割込み要求はプライオリティレベル0（非優先） | （初期値） |

| 1     | IRQ <sub>1</sub> の割込み要求はプライオリティレベル1（優先）  |       |

#### ビット5：プライオリティレベルA5 (IPRA5)

IRQ<sub>2</sub>、IRQ<sub>3</sub>の割込み要求のプライオリティレベルを設定します。

| ビット5  | 説                                                          | 明     |

|-------|------------------------------------------------------------|-------|

| IPRA5 |                                                            |       |

| 0     | IRQ <sub>2</sub> 、IRQ <sub>3</sub> の割込み要求はプライオリティレベル0（非優先） | （初期値） |

| 1     | IRQ <sub>2</sub> 、IRQ <sub>3</sub> の割込み要求はプライオリティレベル1（優先）  |       |

#### ビット4：プライオリティレベルA4 (IPRA4)

IRQ<sub>4</sub>、IRQ<sub>5</sub>の割込み要求のプライオリティレベルを設定します。

| ビット4  | 説                                                          | 明     |

|-------|------------------------------------------------------------|-------|

| IPRA4 |                                                            |       |

| 0     | IRQ <sub>4</sub> 、IRQ <sub>5</sub> の割込み要求はプライオリティレベル0（非優先） | （初期値） |

| 1     | IRQ <sub>4</sub> 、IRQ <sub>5</sub> の割込み要求はプライオリティレベル1（優先）  |       |

### ビット3：プライオリティレベルA3 (IPRA3)

WDT、リフレッシュコントローラの割込み要求のプライオリティレベルを設定します。

| ビット3  | 説明                                                |

|-------|---------------------------------------------------|

| IPRA3 |                                                   |

| 0     | WDT、リフレッシュコントローラの割込み要求はプライオリティレベル0<br>(非優先) (初期値) |

| 1     | WDT、リフレッシュコントローラの割込み要求はプライオリティレベル1<br>(優先)        |

### ビット2：プライオリティレベルA2 (IPRA2)

ITUチャネル0割込み要求のプライオリティレベルを設定します。

| ビット2  | 説明                                     |

|-------|----------------------------------------|

| IPRA2 |                                        |

| 0     | ITUチャネル0の割込み要求はプライオリティレベル0 (非優先) (初期値) |

| 1     | ITUチャネル0の割込み要求はプライオリティレベル1 (優先)        |

### ビット1：プライオリティレベルA1 (IPRA1)

ITUチャネル1の割込み要求のプライオリティレベルを設定します。

| ビット1  | 説明                                     |

|-------|----------------------------------------|

| IPRA1 |                                        |

| 0     | ITUチャネル1の割込み要求はプライオリティレベル0 (非優先) (初期値) |

| 1     | ITUチャネル1の割込み要求はプライオリティレベル1 (優先)        |

### ビット0：プライオリティレベルA0 (IPRA0)

ITUチャネル2の割込み要求のプライオリティレベルを設定します。

| ビット0  | 説明                                     |

|-------|----------------------------------------|

| IPRA0 |                                        |

| 0     | ITUチャネル2の割込み要求はプライオリティレベル0 (非優先) (初期値) |

| 1     | ITUチャネル2の割込み要求はプライオリティレベル1 (優先)        |

(2) インタラプトプライオリティレジスタB (IPRB)

IPRBは8ビットのリード／ライト可能なレジスタで、プライオリティレベルを設定できます。

ビット：

|      | 7     | 6     | 5     | 4   | 3     | 2     | 1     | 0   |

|------|-------|-------|-------|-----|-------|-------|-------|-----|

| 初期値： | IPRB7 | IPRB6 | IPRB5 | —   | IPRB3 | IPRB2 | IPRB1 | —   |

| R/W： | R/W   | R/W   | R/W   | R/W | R/W   | R/W   | R/W   | R/W |

初期値：

0 0 0 0 0 0 0 0

R/W：

R/W R/W R/W R/W R/W R/W R/W R/W

リザーブビット

プライオリティレベルB 1

A/D変換器の割込み要求の

プライオリティレベルを設定

するビットです。

プライオリティレベルB 2

SCIチャネル1の割込み要求のプライ

オリティレベルを設定するビットです。

プライオリティレベルB 3

SCIチャネル0の割込み要求のプライ

オリティレベルを設定するビットです。

リザーブビット

プライオリティレベルB 5

DMAC(チャネル0、1)の割込み要求の

プライオリティレベルを設定するビットです。

プライオリティレベルB 6

ITUチャネル4の割込み要求のプライオリティ

レベルを設定するビットです。

プライオリティレベルB 7

ITUチャネル3の割込み要求のプライオリティレベルを設定するビットです。

IPRBはリセット、ハードウェアスタンバイモード時に、H'00にイニシャライズされます。

#### ビット7：プライオリティレベルB7 (IPRB7)

ITUチャネル3の割込み要求のプライオリティレベルを設定します。

| ビット7  | 説明                                   |

|-------|--------------------------------------|

| IPRB7 |                                      |

| 0     | ITUチャネル3の割込み要求はプライオリティレベル0（非優先）（初期値） |

| 1     | ITUチャネル3の割込み要求はプライオリティレベル1（優先）       |

#### ビット6：プライオリティレベルB6 (IPRB6)

ITUチャネル4の割込み要求のプライオリティレベルを設定します。

| ビット6  | 説明                                   |

|-------|--------------------------------------|

| IPRB6 |                                      |

| 0     | ITUチャネル4の割込み要求はプライオリティレベル0（非優先）（初期値） |

| 1     | ITUチャネル4の割込み要求はプライオリティレベル1（優先）       |

#### ビット5：プライオリティレベルB5 (IPRB5)

DMA（チャネル0、1）の割込み要求のプライオリティレベルを設定します。

| ビット5  | 説明                                               |

|-------|--------------------------------------------------|

| IPRB5 |                                                  |

| 0     | DMA（チャネル0、1）の割込み要求はプライオリティレベル0<br>（非優先）<br>(初期値) |

| 1     | DMA（チャネル0、1）の割込み要求はプライオリティレベル1<br>（優先）           |

#### ビット4：リザーブビット

リザーブビットです。リード／ライト可能ですが、優先順位には関係ありません。

**ビット3：プライオリティレベルB3（IPRB3）**

SCIチャネル0の割込み要求のプライオリティレベルを設定します。

| ビット3  | 説明                                   |

|-------|--------------------------------------|

| IPRB3 |                                      |

| 0     | SCIチャネル0の割込み要求はプライオリティレベル0（非優先）（初期値） |

| 1     | SCIチャネル0の割込み要求はプライオリティレベル1（優先）       |

**ビット2：プライオリティレベルB2（IPRB2）**

SCIチャネル1の割込み要求のプライオリティレベルを設定します。

| ビット2  | 説明                                   |

|-------|--------------------------------------|

| IPRB2 |                                      |

| 0     | SCIチャネル1の割込み要求はプライオリティレベル0（非優先）（初期値） |

| 1     | SCIチャネル1の割込み要求はプライオリティレベル1（優先）       |

**ビット1：プライオリティレベルB1（IPRB1）**

A/D変換器の割込み要求のプライオリティレベルを設定します。

| ビット1  | 説明                                 |

|-------|------------------------------------|

| IPRB1 |                                    |

| 0     | A/D変換器の割込み要求はプライオリティレベル0（非優先）（初期値） |

| 1     | A/D変換器の割込み要求はプライオリティレベル1（優先）       |

**ビット0：リザーブビット**

リザーブビットです。リード/ライト可能ですが、優先順位には関係ありません。

### 5.2.3 IRQステータスレジスタ (ISR)

ISRは8ビットのリード/ライト可能なレジスタで、IRQ<sub>n</sub>～IRQ<sub>0</sub>割込み要求のステータスの表示を行います。

| ビット:    | 7 | 6 | 5      | 4      | 3                                                             | 2      | 1      | 0      |

|---------|---|---|--------|--------|---------------------------------------------------------------|--------|--------|--------|

|         | — | — | IRQ5F  | IRQ4F  | IRQ3F                                                         | IRQ2F  | IRQ1F  | IRQ0F  |

| 初期値:    | 0 | 0 | 0      | 0      | 0                                                             | 0      | 0      | 0      |

| R/W:    | — | — | R/(W)* | R/(W)* | R/(W)*                                                        | R/(W)* | R/(W)* | R/(W)* |

| リザーブビット |   |   |        |        | <u>IRQ<sub>n</sub>～IRQ<sub>0</sub>フラグ</u>                     |        |        |        |

|         |   |   |        |        | IRQ <sub>n</sub> ～IRQ <sub>0</sub> 割込み要求の<br>ステータスを表示するビットです。 |        |        |        |

【注】\* フラグをクリアするための“0”ライトのみ可能です。

ISRはリセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。

ビット7、6：リザーブビット

リザーブビットです。リードすると常に“0”が読み出されます。ライトは無効です。

ビット5～0：IRQ<sub>n</sub>～IRQ<sub>0</sub>フラグ (IRQ5F～IRQ0F)

IRQ<sub>n</sub>～IRQ<sub>0</sub>割込み要求のステータスの表示を行います。

| ビット5～0      | 説明                                                                                                                                                                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ5F～IRQ0F |                                                                                                                                                                                                                                                                           |

| 0           | <p>[クリア条件] (初期値)</p> <p>(1) IRQ<sub>n</sub>F = “1”的状態でIRQ<sub>n</sub>Fフラグをリードした後、IRQ<sub>n</sub>Fフラグに“0”をライトしたとき</p> <p>(2) IRQ<sub>n</sub>SC = “0”、IRQ<sub>n</sub>入力が“High”レベルの状態で割込み例外処理を実行したとき</p> <p>(3) IRQ<sub>n</sub>SC = “1”的状態でIRQ<sub>n</sub>割込み例外処理を実行したとき</p> |

| 1           | <p>[セット条件]</p> <p>(1) IRQ<sub>n</sub>SC = “0”的状態でIRQ<sub>n</sub>入力が“Low”レベルになったとき</p> <p>(2) IRQ<sub>n</sub>SC = “1”的状態でIRQ<sub>n</sub>入力に立下がりエッジが発生したとき</p>                                                                                                              |

(n = 5～0)

### 5.2.4 I R Q イネーブルレジスタ (I E R)

I E R は 8 ビットのリード／ライト可能なレジスタで、I R Q<sub>5</sub>～I R Q<sub>0</sub>割込み要求の許可／禁止を制御します。

| ビット：    | 7   | 6   | 5     | 4                                                                                                                 | 3     | 2     | 1     | 0     |

|---------|-----|-----|-------|-------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

|         | —   | —   | IRQ5E | IRQ4E                                                                                                             | IRQ3E | IRQ2E | IRQ1E | IRQ0E |

| 初期値：    | 0   | 0   | 0     | 0                                                                                                                 | 0     | 0     | 0     | 0     |

| R/W：    | R/W | R/W | R/W   | R/W                                                                                                               | R/W   | R/W   | R/W   | R/W   |

| リザーブビット |     |     |       | <u>I R Q<sub>5</sub>～I R Q<sub>0</sub>イネーブル</u><br>I R Q <sub>5</sub> ～I R Q <sub>0</sub> 割込みを許可／禁止するかを選択するビットです。 |       |       |       |       |

I E R はリセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。

#### ビット 7、6：リザーブビット

リザーブビットです。リード／ライト可能ですが割込み要求の許可／禁止には関係ありません。

#### ビット 5～0：I R Q<sub>5</sub>～I R Q<sub>0</sub>イネーブル (IRQ5E～IRQ0E)

I R Q<sub>5</sub>～I R Q<sub>0</sub>割込みを許可／禁止するかを選択します。

| ビット 5～0     | 説明                                                     |

|-------------|--------------------------------------------------------|

| IRQ5E～IRQ0E |                                                        |

| 0           | I R Q <sub>5</sub> ～I R Q <sub>0</sub> 割込みを禁止<br>(初期値) |

| 1           | I R Q <sub>5</sub> ～I R Q <sub>0</sub> 割込みを許可          |

### 5.2.5 IRQ センスコントロールレジスタ (ISCR)

ISCR は 8 ビットのリード／ライト可能なレジスタで、IRQ<sub>5</sub>～IRQ<sub>0</sub>端子の入力のレベルセンスまたは立下がりエッジを選択します。

| ビット：                                                               | 7   | 6   | 5   | 4                                               | 3   | 2   | 1   | 0   |

|--------------------------------------------------------------------|-----|-----|-----|-------------------------------------------------|-----|-----|-----|-----|

| 初期値：                                                               | 0   | 0   | 0   | 0                                               | 0   | 0   | 0   | 0   |

| R/W：                                                               | R/W | R/W | R/W | R/W                                             | R/W | R/W | R/W | R/W |

| リザーブビット                                                            |     |     |     | <u>IRQ<sub>5</sub>～IRQ<sub>0</sub>センスコントロール</u> |     |     |     |     |

| IRQ <sub>5</sub> ～IRQ <sub>0</sub> 割込みのレベルセンスまたは立下がりエッジを選択するビットです。 |     |     |     |                                                 |     |     |     | —   |

ISCR はリセットまたは、ハードウェアスタンバイモード時に、H'00にイニシャライズされます。

ビット 7、6：リザーブビット

リザーブビットです。リード／ライト可能ですが、レベルセンスまたは立下がりエッジの選択には関係ありません。

ビット 5～0：IRQ<sub>5</sub>～IRQ<sub>0</sub>センスコントロール (IRQ5SC～IRQ0SC)

IRQ<sub>5</sub>～IRQ<sub>0</sub>割込みをIRQ<sub>5</sub>～IRQ<sub>0</sub>端子のレベルセンスで要求するか、立下がりエッジで要求するかを選択します。

| ビット 5～0       | 説                                                       | 明     |

|---------------|---------------------------------------------------------|-------|

| IRQ5SC～IRQ0SC |                                                         |       |

| 0             | IRQ <sub>5</sub> ～IRQ <sub>0</sub> 入力の“Low”レベルで割込み要求を発生 | (初期値) |

| 1             | IRQ <sub>5</sub> ～IRQ <sub>0</sub> 入力の立下がりエッジで割込み要求を発生  |       |

## 5.3 割込み要因

割込み要因には、外部割込み（NMI、IRQ<sub>n</sub>～IRQ<sub>0</sub>）と内部割込み（30要因）があります。

### 5.3.1 外部割込み

外部割込みには、NMI、IRQ<sub>n</sub>～IRQ<sub>0</sub>の7要因があります。このうち、NMI、IRQ<sub>n</sub>～IRQ<sub>0</sub>はソフトウェアスタンバイモードからの復帰に使用できます。

#### (1) NMI割込み

NMIは最優先の割込みで、CCRのIビット、UIビットの状態にかかわらず常に受け付けられます。NMI端子の立上がりエッジまたは立下がりエッジのいずれかで割込みを要求するか、SCRのNMIEGビットで選択できます。

NMI割込み例外処理のベクタ番号は7です。

#### (2) IRQ<sub>n</sub>～IRQ<sub>0</sub>割込み

IRQ<sub>n</sub>～IRQ<sub>0</sub>割込みはIRQ<sub>n</sub>～IRQ<sub>0</sub>端子の入力信号により要求されます。IRQ<sub>n</sub>～IRQ<sub>0</sub>割込みには次の特長があります。

- ① IRQ<sub>n</sub>～IRQ<sub>0</sub>端子の“Low”レベルまたは立下がりエッジのどちらで割込みを要求するか、ISRで選択できます。

- ② IRQ<sub>n</sub>～IRQ<sub>0</sub>割込み要求を許可するか禁止するかを、IERで選択できます。また、IPRAのIPRA7～IPRA4ビットにより割込みプライオリティレベルを設定できます。

- ③ IRQ<sub>n</sub>～IRQ<sub>0</sub>割込み要求のステータスは、ISRに表示されます。ISRのフラグはソフトウェアで“0”にクリアすることができます。

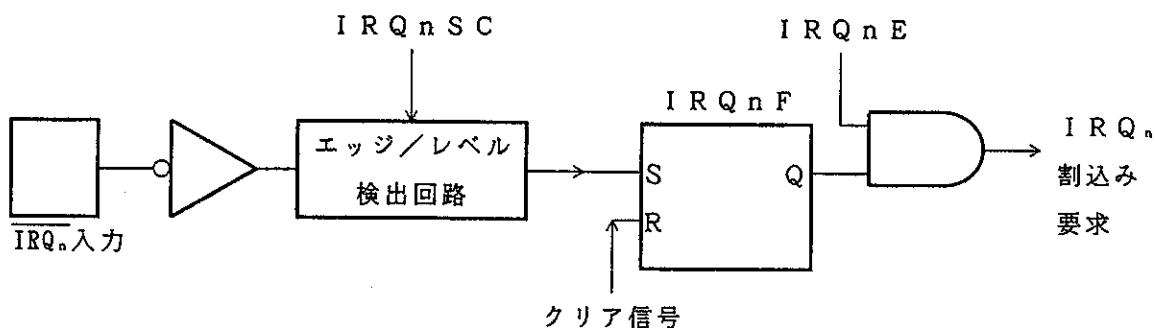

IRQ<sub>n</sub>～IRQ<sub>0</sub>割込みのブロック図を図5.2に示します。

【注】 n : 5～0

図5.2 IRQ<sub>n</sub>～IRQ<sub>0</sub>割込みのブロック図

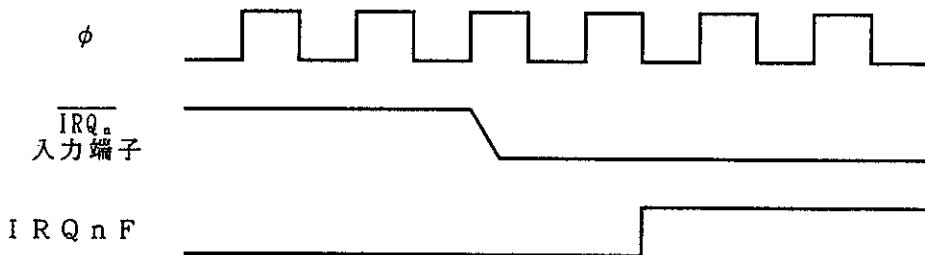

I R Q n F のセットタイミングを図 5.3 に示します。

【注】 n = 5 ~ 0

図 5.3 I R Q n F セットタイミング

I R Q<sub>0</sub>～I R Q<sub>5</sub>割込み例外処理のベクタ番号は12～17です。

I R Q<sub>0</sub>～I R Q<sub>5</sub>割込みの検出は、当該の端子が入力に設定されているか、出力に設定されているかに依存しません。したがって、外部割込み入力端子として使用する場合は、対応する D D R を“0”にクリアし、チップセレクト出力端子、リフレッシュ出力端子、S C I の入出力端子としては使用しないでください。

### 5.3.2 内部割込み

内蔵周辺モジュールからの割込みによる内部割込みは30要因あります。

- (1) 各内蔵周辺モジュールには割込み要求のステータスを表示するフラグと、これらの割込みを許可するか禁止するかを選択するイネーブルビットがあります。

- (2) I P R A、B によって割込みプライオリティレベルを設定できます。

- (3) I T U、S C I の割込み要求でD M A C の起動ができます。この場合、割込みコントローラに対して割込みは要求されません。このときは I、U I ビットの影響を受けません。

### 5.3.3 割込み例外処理ベクタテーブル

表 5.3 に割込み例外処理要因とベクタアドレスおよび割込み優先順位の一覧を示します。デフォルトの優先順位はベクタ番号の小さいものほど高くなります。I P R A、B によりN M I 以外の割込みの優先順位を変更することができます。

リセット後の割込み優先順位は表 5.3 に示されるデフォルトの順位となります。

表 5.3 割込み要因とベクタアドレスおよび割込み優先順位一覧(1)

| 割込み要因                       | 要因発生元          | ベクタ番号           | ベクタアドレス*        | I P R | 優先順位 |  |

|-----------------------------|----------------|-----------------|-----------------|-------|------|--|

| NMI                         | 外部端子           | 7               | H' 001C~H' 001F | ---   | 高↑   |  |

| IRQ <sub>0</sub>            |                | 12              | H' 0030~H' 0033 | IPRA7 |      |  |

| IRQ <sub>1</sub>            |                | 13              | H' 0034~H' 0037 | IPRA6 |      |  |

| IRQ <sub>2</sub>            |                | 14              | H' 0038~H' 003B | IPRA5 |      |  |

| IRQ <sub>3</sub>            |                | 15              | H' 003C~H' 003F |       |      |  |

| IRQ <sub>4</sub>            |                | 16              | H' 0040~H' 0043 | IPRA4 |      |  |

| IRQ <sub>5</sub>            |                | 17              | H' 0044~H' 0047 |       |      |  |

| リザーブ                        |                | 18              | H' 0048~H' 004B | IPRA3 |      |  |

|                             |                | 19              | H' 004C~H' 004F |       |      |  |

| W0VI(インターバルタイマ)             | ウォッチドッグタイマ     | 20              | H' 0050~H' 0053 |       |      |  |

| CMI(コンペアマッチ)                | リフレッシュコントローラ   | 21              | H' 0054~H' 0057 |       |      |  |

| リザーブ                        | 22             | H' 0058~H' 005B | IPRA2           |       |      |  |

| OV10 (オーバフロー0)              | 23             | H' 005C~H' 005F |                 |       |      |  |

| IMIA0(コンペアマッチ/インプットキャプチャA0) | I T U<br>チャネル0 | 24              | H' 0060~H' 0063 | IPRA2 |      |  |

| IMIB0(コンペアマッチ/インプットキャプチャB0) |                | 25              | H' 0064~H' 0067 |       |      |  |

| OV10 (オーバフロー0)              |                | 26              | H' 0068~H' 006B |       |      |  |

| リザーブ                        |                | 27              | H' 006C~H' 006F |       |      |  |

| IMIA1(コンペアマッチ/インプットキャプチャA1) | I T U<br>チャネル1 | 28              | H' 0070~H' 0073 | IPRA1 |      |  |

| IMIB1(コンペアマッチ/インプットキャプチャB1) |                | 29              | H' 0074~H' 0077 |       |      |  |

| OV11 (オーバフロー1)              |                | 30              | H' 0078~H' 007B |       |      |  |

| リザーブ                        |                | 31              | H' 007C~H' 007F |       |      |  |

| IMIA2(コンペアマッチ/インプットキャプチャA2) | I T U<br>チャネル2 | 32              | H' 0080~H' 0083 | IPRA0 |      |  |

| IMIB2(コンペアマッチ/インプットキャプチャB2) |                | 33              | H' 0084~H' 0087 |       |      |  |

| OV12 (オーバフロー2)              |                | 34              | H' 0088~H' 008B |       |      |  |

| リザーブ                        |                | 35              | H' 008C~H' 008F |       |      |  |

| IMIA3(コンペアマッチ/インプットキャプチャA3) | I T U<br>チャネル3 | 36              | H' 0090~H' 0093 | IPRB7 |      |  |

| IMIB3(コンペアマッチ/インプットキャプチャB3) |                | 37              | H' 0094~H' 0097 |       |      |  |

| OV13 (オーバフロー3)              |                | 38              | H' 0098~H' 009B |       |      |  |

| リザーブ                        |                | 39              | H' 009C~H' 009F |       |      |  |

| IMIA4(コンペアマッチ/インプットキャプチャA4) | I T U<br>チャネル4 | 40              | H' 00A0~H' 00A3 | IPRB6 |      |  |

| IMIB4(コンペアマッチ/インプットキャプチャB4) |                | 41              | H' 00A4~H' 00A7 |       |      |  |

| OV14 (オーバフロー4)              |                | 42              | H' 00A8~H' 00AB |       |      |  |

| リザーブ                        |                | 43              | H' 00AC~H' 00AF |       |      |  |

【注】\* アドレスの下位16ビットを示しています。

表5.3 割込み要因とベクタアドレスおよび割込み優先順位一覧(2)

| 割込み要因             | 要因発生元          | ベクタ番号 | ベクタアドレス       | IPR   | 優先順位 |

|-------------------|----------------|-------|---------------|-------|------|

| DEND0A            | D M A C        | 44    | H'00B0~H'00B3 | IPRB5 | ↑    |

| DEND0B            |                | 45    | H'00B4~H'00B7 |       |      |

| DEND1A            |                | 46    | H'00B8~H'00BB |       |      |

| DEND1B            |                | 47    | H'00BC~H'00BF |       |      |

| リザーブ              | —              | 48    | H'00C0~H'00C3 | —     | ↓    |

|                   |                | 49    | H'00C4~H'00C7 |       |      |

|                   |                | 50    | H'00C8~H'00CB |       |      |

|                   |                | 51    | H'00CC~H'00CF |       |      |

| ERI0(受信エラー0)      | S C I<br>チャネル0 | 52    | H'00D0~H'00D3 | IPRB3 | ↓    |

| RXI0(受信データフル0)    |                | 53    | H'00D4~H'00D7 |       |      |

| TXI0(送信データエンプティ0) |                | 54    | H'00D8~H'00DB |       |      |

| TEI0(送信終了0)       |                | 55    | H'00DC~H'00DF |       |      |

| ERI1(受信エラー1)      | S C I<br>チャネル1 | 56    | H'00E0~H'00E3 | IPRB2 | ↓    |

| RXI1(受信データフル1)    |                | 57    | H'00E4~H'00E7 |       |      |

| TXI1(送信データエンプティ1) |                | 58    | H'00E8~H'00EB |       |      |

| TEI1(送信終了1)       |                | 59    | H'00EC~H'00EF |       |      |

| ADI(A/Dエンド)       | A / D          | 60    | H'00F0~H'00F3 | IPRB1 | 低    |

【注】\* アドレスの下位16ビットを示しています。

## 5.4 割込み動作

### 5.4.1 割込み動作の流れ

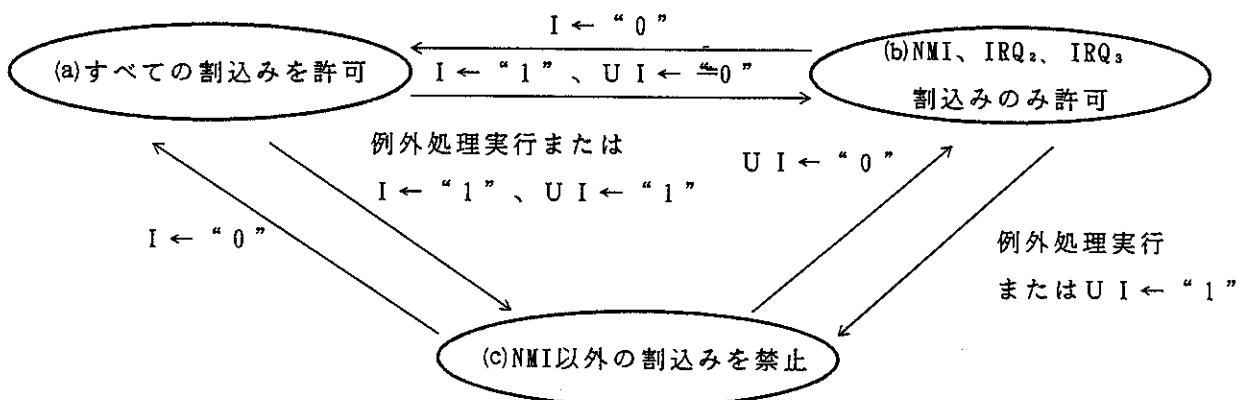

本LSIでは、割込みの動作はUEビットの状態によって異なります。UE = “1”的ときはIビットで割込みの制御が行われます。UE = “0”的ときは、I、UIビットの組み合わせで割込みの制御が行われます。表5.4にUE、I、UIビットの各組み合わせのときの割込みの状態を示します。

NMI割込みはリセット状態、ハードウェアスタンバイ状態を除き常に受付けられます。IRQ割込みおよび内蔵周辺モジュールの割込みは、それぞれの割込みに対応したイネーブルビットがあります。このイネーブルビットを“0”にクリアすると、その割込み要求は無視されます。

表5.4 UE、I、UIビットの組み合わせによる割込みの状態

| S Y S C R | C C R |   | 状 態                                           |

|-----------|-------|---|-----------------------------------------------|

|           | U E   | I |                                               |

| 1         | 0     | — | すべての割込みを受け付けます。プライオリティレベル1の割込み要因の優先順位が高くなります。 |

|           | 1     | — | NMI以外の割込みを受け付けません。                            |

| 0         | 0     | — | すべての割込みを受け付けます。プライオリティレベル1の割込み要因の優先順位が高くなります。 |

|           | 1     | 0 | NMIおよびプライオリティレベル1の割込み要因のみを受け付けます。             |

|           |       | 1 | NMI以外の割込みを受け付けません。                            |

#### (1) UEビット = “1”的場合

IRQ～IRQ割込みおよび内蔵周辺モジュールの割込みはCPUのCCRのIビットにより一括して、許可／禁止を設定できます。Iビットが“0”にクリアされているときは許可状態、“1”にセットされているときは禁止状態です。プライオリティレベル1の割込み要因の優先順位は高くなります。

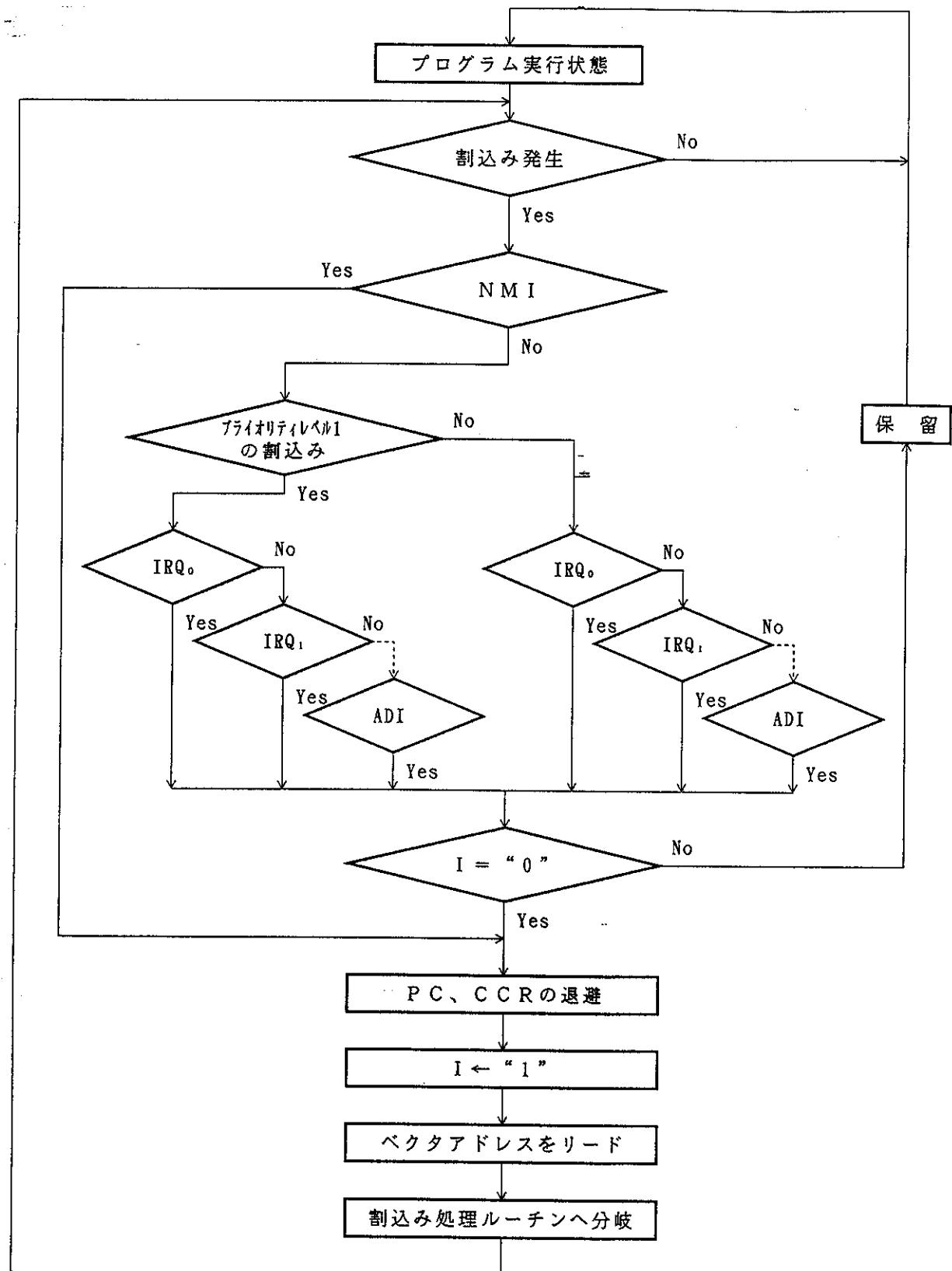

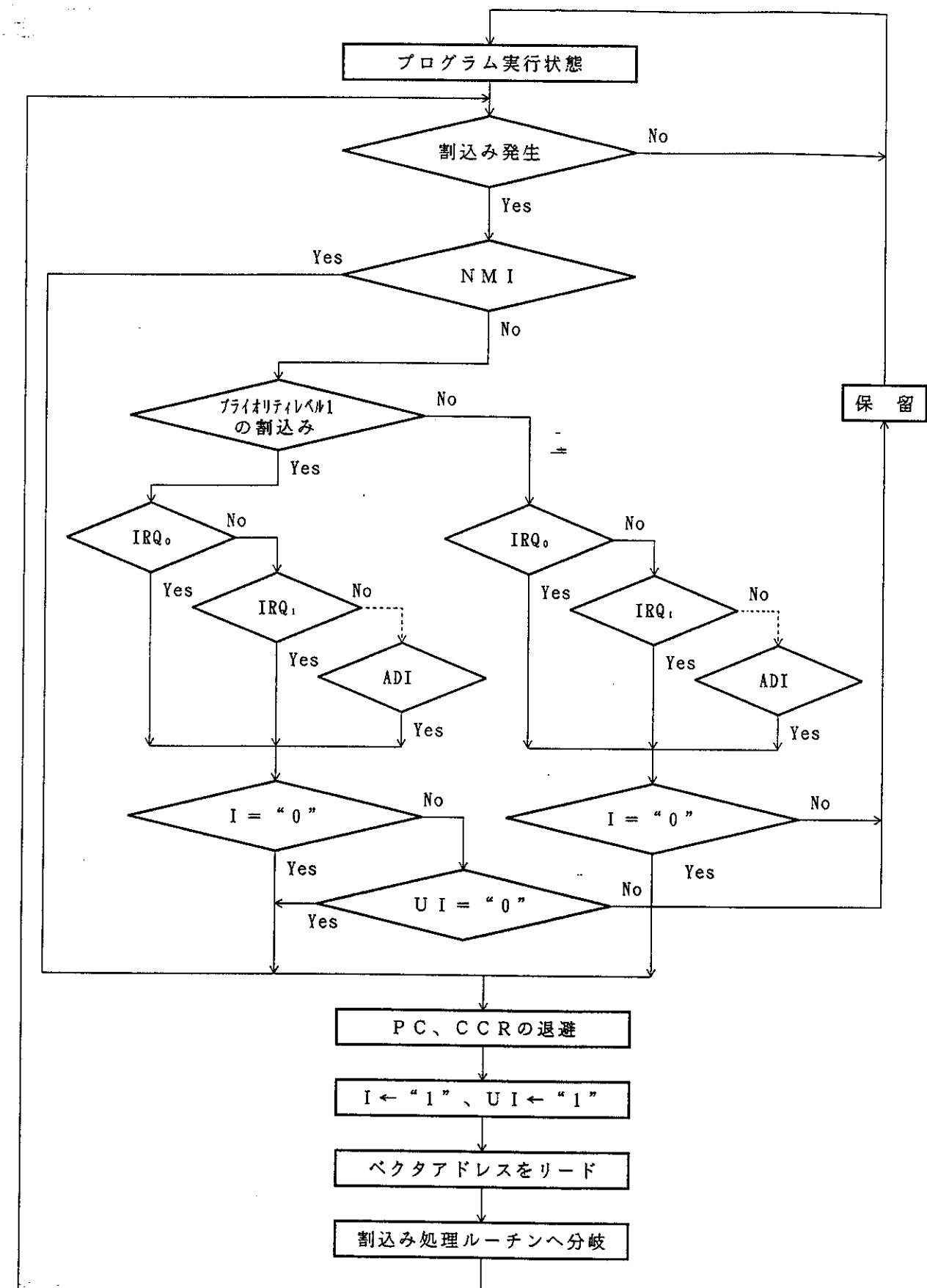

この場合の割込み受付けの動作フローチャートを図5.4に示します。

図 5.4  $UE = "1"$  の場合の割込み受付けまでのフロー

- ① 対応する割込みイネーブルビットが“1”にセットされている状態で割込み要因が発生したとき、割込みコントローラに対して、割込み要求が送られます。

- ② 割込みコントローラに対して割込み要求が送られると、IPRに設定された割込み優先順位に従って優先順位が最も高い割込み要求が選択され、その他は保留となります。IPRの設定が同一の割込み要求が同時に発生したときは、表5.3に示す優先度に従って、優先順位の最も高い割込み要求が選択されます。

- ③ Iビットを参照します。Iビットが“0”にクリアされているときは、割込み要求が受け付けられます。Iビットが“1”にセットされているときは、NMI割込みのみ受け付けられ、その他の割込み要求は保留されます。

- ④ 割込み要求が受け付けられると、そのとき実行中の命令の処理が終了した後、割込み例外処理を起動します。

- ⑤ 割込み例外処理によって、PCとCCRがスタック領域に退避されます。退避されるPCは、リターン後に実行する最初の命令のアドレスを示しています。

- ⑥ 次にCCRのIビットが“1”にセットされます。これにより、NMIを除く割込みはマスクされます。

- ⑦ 受け付けた割込み要求に対応するベクタアドレスを生成し、そのベクタアドレスの内容によって示されるアドレスから、割込み処理ルーチンの実行が開始されます。

## (2) UEビット = “0”的場合

IRQ<sub>0</sub>～IRQ<sub>7</sub>割込みおよび内蔵周辺モジュールの割込みはCPUのCCRのI、UIビット、IPRによって3レベルの許可／禁止状態を実現できます。

- (a) プライオリティレベル0の割込み要求は、Iビットが“0”にクリアされているとき許可状態、“1”にセットされているとき禁止状態となります。

- (b) プライオリティレベル1の割込み要求は、IビットまたはUIビットが“0”にクリアされているとき許可状態、IビットおよびUIビットがいずれも“1”にセットされているとき禁止状態となります。

例えば、各割込み要求の対応する割込みイネーブルビットを“1”にセット、IPRA、IPRBをそれぞれH'20、H'00に設定した場合（IRQ<sub>2</sub>、IRQ<sub>3</sub>割込み要求の優先順位を他の割込みより高くした場合）、次のようにになります。

- (a) I = “0”的とき、すべての割込みを許可

(優先順位：NMI > IRQ<sub>2</sub> > IRQ<sub>3</sub> > IRQ<sub>0</sub>…)

- (b) I = “1”、UI = “0”的とき、NMI、IRQ<sub>2</sub>、IRQ<sub>3</sub>割込みのみを許可

- (c) I = “1”、UI = “1”的とき、NMI以外の割込みを禁止

また、このときの状態遷移を図5.5に示します。

図5.5 割込み許可／禁止状態の遷移例

UE ビット = “0” のときの割込み受付けの動作フローチャートを図 5.6 に示します。

- ① 対応する割込みイネーブルビットが “1” にセットされている状態で割込み要因が発生したとき、割込みコントローラに対して割込み要求が送られます。

- ② 割込みコントローラに対して割込み要求が送られると、IPR に設定された割込み優先順位に従って優先順位が最も高い割込み要求が選択され、その他は保留となります。このとき、IPR の設定が同一の割込み要求が同時に発生したときは、表 5.3 に示す優先度に従って、優先順位の最も高い割込み要求が選択されます。

- ③ I ビットを参照します。I ビットが “0” にクリアされているときは、IPR に関係なく割込み要求が受け付けられます。このときは UI ビットの影響を受けません。I ビットが “1” にセットされ、UI ビットが “0” にクリアされているときは、プライオリティレベル 1 の割込み要求のみが受け付けられ、プライオリティレベル 0 の割込み要求は保留となります。I、UI ビットがいずれも “1” にセットされているときは、割込み要求は保留となります。

- ④ 割込み要求が受け付けられると、そのとき実行中の命令の処理が終了した後、割込み例外処理を起動します。

- ⑤ 割込み例外処理によって PC と CCR がスタック領域に退避されます。退避される PC は、リターン後に実行する最初の命令のアドレスを示しています。

- ⑥ CCR の I、UI ビットが “1” にセットされます。これにより、NMI を除く割込みはマスクされます。

- ⑦ 受け付けた割込み要求に対応するベクタアドレスを生成し、そのベクタアドレスの内容によって示されるアドレスから、割込み処理ルーチンの実行が開始されます。

図 5.6  $UE = "0"$  の場合の割込み受付けまでのフロー

#### 5.4.2 割込み例外処理シーケンス

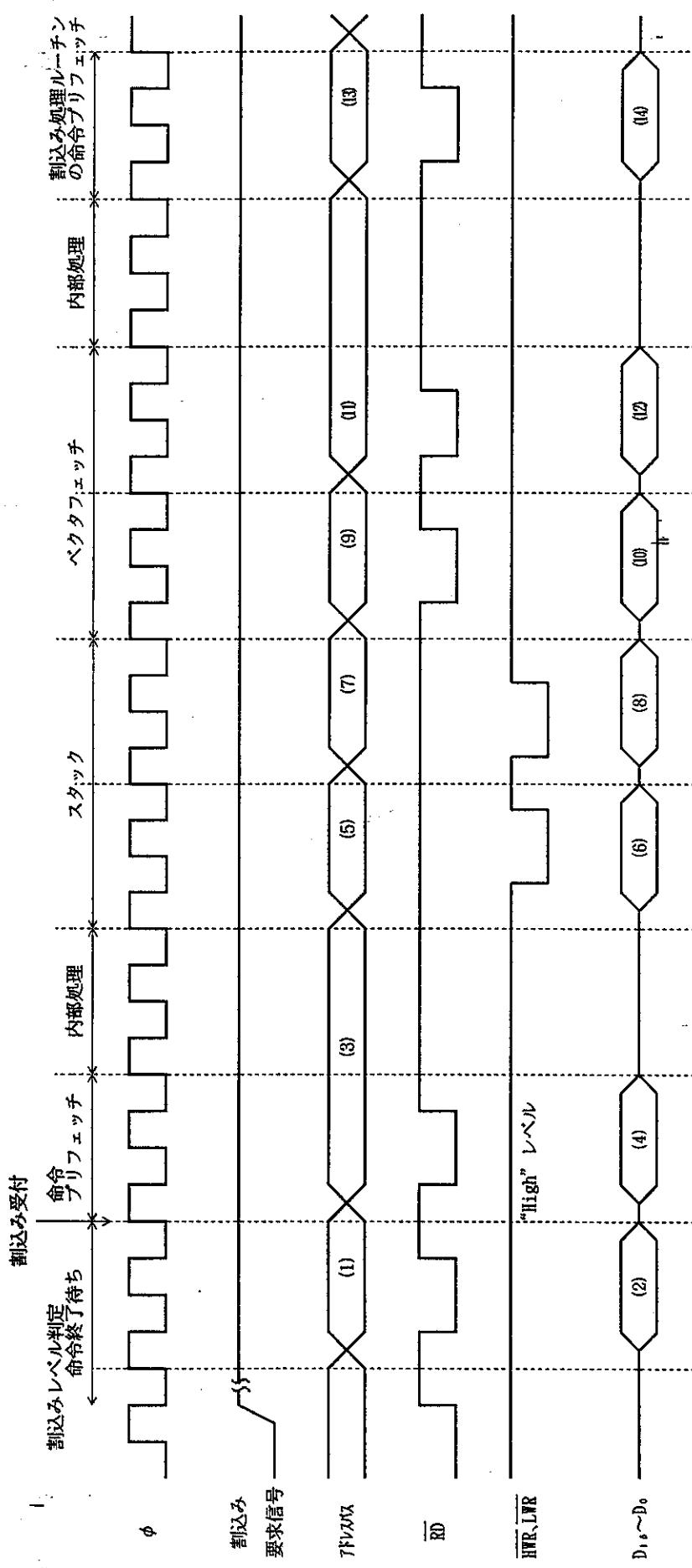

モード2で、プログラム領域とスタック領域を外部メモリ16ビット2ステートアクセス空間にとった場合の割込みシーケンスを図5.7に示します。

- (1) 命令のプリフェッチアドレス（実行されません。退避PCの内容であり、リターンアドレスです。）

(2)(4) 命令コード（実行されません。）

(3) 命令のプリフェッチアドレス（実行されません。）

(5) SP - 2      (7) SP - 4

(6)(8) 退避PCと退避CCR

- (9)(11) ベクタアドレス

(10)(12) 割込み処理ルーチン開始アドレス（ベクタアドレスの内容）

(13) 割込み処理ルーチン開始アドレス（(9)=(10)(12)）

(14) 割込み処理ルーチン先頭命令

【注】 モード2でプログラム領域とスタック領域を外部メモリ16ビット2ステートアクセス、スタック外部メモリ

図5.7 割込みシーケンス（モード2、2ステートアクセス、スタック外部メモリ）

### 5.4.3 割込み応答時間

割込み要求発生後、割込み処理ルーチンの先頭命令を実行するまでの、割込み応答時間を表5.5に示します。

表5.5 割込み応答時間

| No. | 項目                      | 内蔵メモリ | 外部メモリ           |                    |                  |                    |

|-----|-------------------------|-------|-----------------|--------------------|------------------|--------------------|

|     |                         |       | 8ビット2ステートアクセス空間 | 8ビット3ステートアクセス空間    | 16ビット2ステートアクセス空間 | 16ビット3ステートアクセス空間   |

| 1   | 割込み優先順位判定               |       |                 |                    | 2 <sup>*1</sup>  |                    |

| 2   | 実行中の命令が終了するまでの最大待ちステート数 | 1~23  | 1~27            | 1~31 <sup>*4</sup> | 1~23             | 1~25 <sup>*4</sup> |

| 3   | P C、C C R のスタック         | 4     | 8               | 12 <sup>*4</sup>   | 4                | 6 <sup>*4</sup>    |

| 4   | ベクタフェッチ                 | 4     | 8               | 12 <sup>*4</sup>   | 4                | 6 <sup>*4</sup>    |

| 5   | 命令フェッチ <sup>*2</sup>    | 4     | 8               | 12 <sup>*4</sup>   | 4                | 6 <sup>*4</sup>    |

| 6   | 内部処理 <sup>*3</sup>      | 4     | 4               | 4                  | 4                | 4                  |

| 合 計 |                         | 19~41 | 31~57           | 43~73              | 19~41            | 25~49              |

単位：ステート

【注】<sup>\*1</sup> 内部割込みの場合1ステートとなります。

<sup>\*2</sup> 割込み受付け後のプリフェッチおよび割込み処理ルーチンのプリフェッチ

<sup>\*3</sup> 割込み受付け後の内部処理およびベクタフェッチ後の内部処理

<sup>\*4</sup> 外部メモリアクセス時にウェイトが挿入される場合には、ステート数が増加します。

## 5.5 使用上の注意

### 5.5.1 割込みの発生とディスエーブルとの競合

割込みイネーブルビットを“0”にクリアして割込みを禁止する場合、割込みの禁止はその命令実行終了後有効になります。すなわち、B C L R 命令、M O V 命令などで割込みイネーブルビットを“0”にクリアする場合、命令実行中にその割込みが発生すると、命令実行終了時点では当該割込み許可状態にあるため命令実行終了後にその割込み例外処理を実行します。ただし、その割込みより優先順位の高い割込み要求がある場合には優先順位の高い割込み例外処理を実行し、その割込みは無視されます。割込み要因フラグを“0”にクリアする場合も同様です。

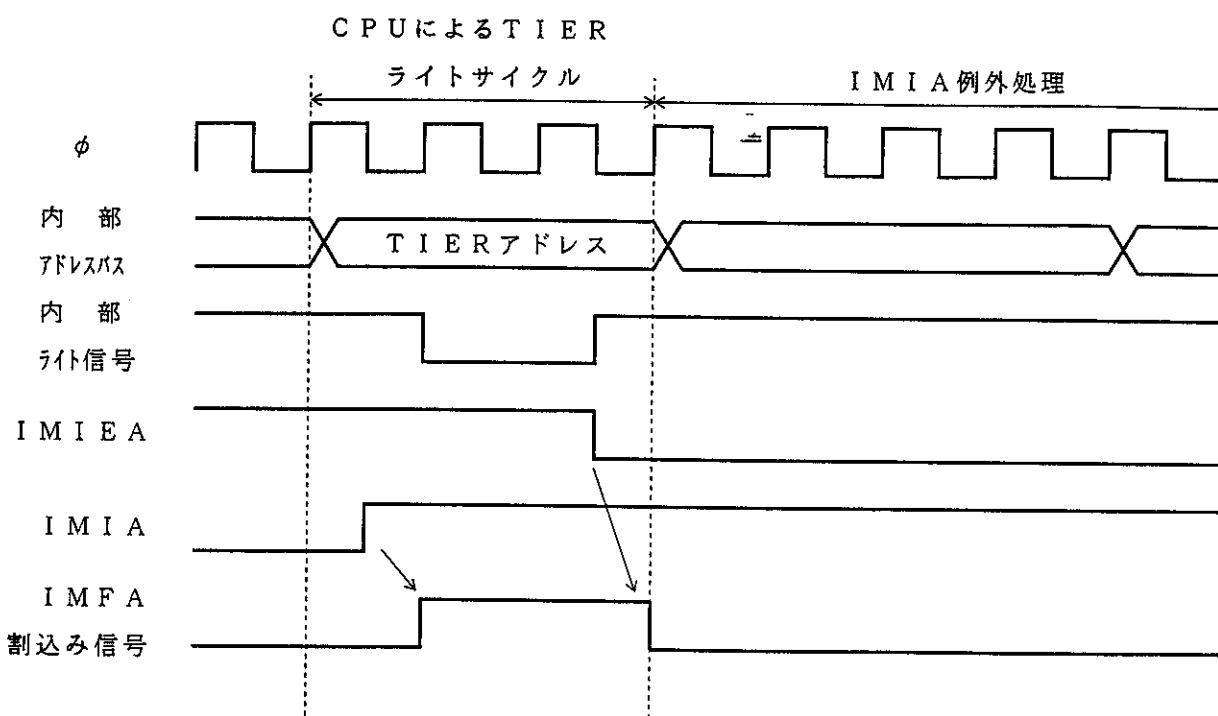

ITUのTIERのIMIEAビットを“0”にクリアする場合の例を図5.8に示します。

図5.8 割込みの発生とディスエーブルの競合

なお、割込みをマスクした状態でイネーブルビットまたは割込み要因フラグを“0”にクリアすれば、上記の競合は発生しません。

## 5.5.2 割込みの受け付けを禁止している命令

割込みを禁止している命令には、LDC、ANDC、ORC、XORC命令があります。割込み要求が発生すると、割込みコントローラが優先順位を判定した後、CPUに対して割込みを要求します。そのとき、CPUが割込みを禁止している命令を実行している場合は、その命令の実行を終了した後、必ず次の命令を実行します。

## 5.5.3 EEPMOV命令実行中の割込み

EEPMOV命令は、EEPMOV.W命令とEEPMOV.B命令では、割込み動作が異なります。

EEPMOV.B命令は、転送中にNMIを含めた割込み要求があっても転送終了まで割込みを受け付けません。

EEPMOV.W命令のときは、転送中にNMI以外の割込み要求があっても転送終了まで割込みを受け付けません。NMI割込み要求の場合は、転送サイクルの切れ目でNMI例外処理が開始されます。このときスタックされるPCの値は次命令のアドレスとなります。

このため、EEPMOV.W命令実行中にNMI割込みが発生する場合には、以下のプログラムとしてください。

```

L1 : EEPMOV.W

MOV.W R4, R4

BNE L1

```

## 5.5.4 外部割込み使用上の注意

IRQnFフラグは、IRQnF = “1”の状態でIRQnFフラグをリードした後、IRQnFフラグに“0”をライトしたとき、クリアされる仕様になっています。しかしながら、IRQnF = “1”の状態をリードしていないにも関わらず、IRQnFフラグに“0”をライトしただけで、誤ってIRQnFフラグがクリアされ、割込み例外処理が実行されない場合があります。

これは、以下のような条件が満たされたときに起こります。

### (1) 設定条件

- ① 複数の外部割込み(IRQn、IRQn+)を使用している。

- ② IRQnFフラグは“0”ライトによるクリア、IRQnFフラグはハードウェアによるクリアと異なったクリア方法を用いている。

- ③ IRQnFフラグのクリアに、IRQステータスレジスタ(ISR)に対するビット操作命令を使用、もしくはISRをバイト単位でリードし、IRQnFフラグのビットをクリアし、他のビットはリードした値をバイト単位でライトしている。

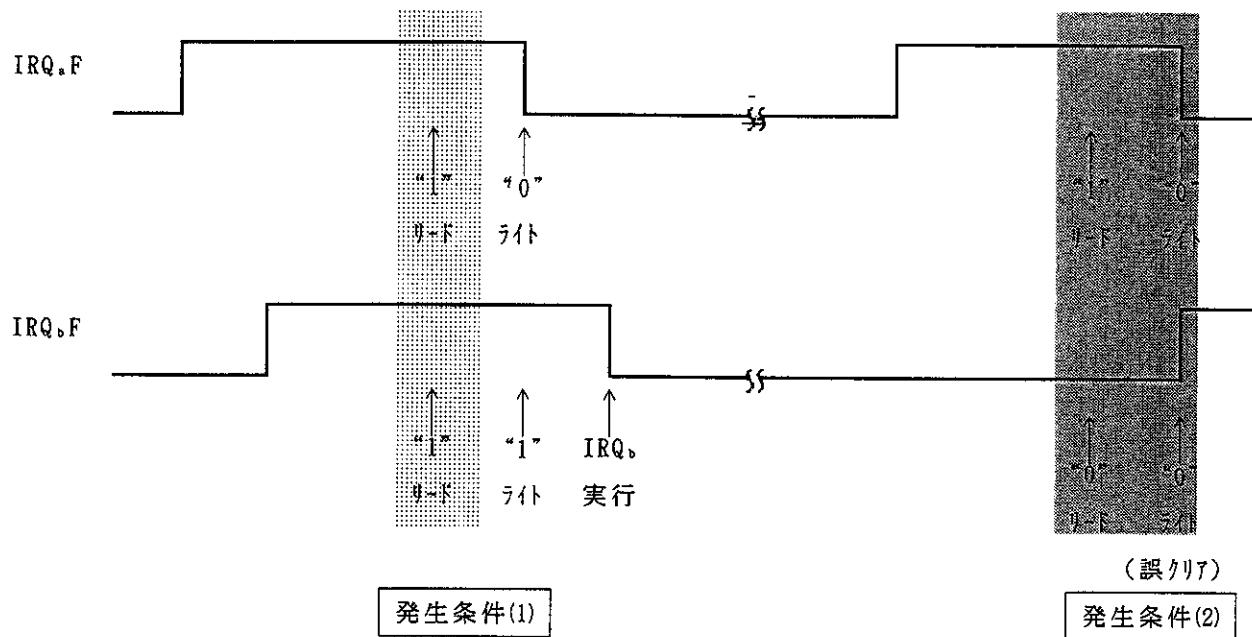

## (2) 発生条件

- ①  $IRQ_a.F = "1"$  の状態で  $IRQ_a.F$  フラグをクリアするための ISR レジスタのリードが実行され、その後、割込み例外処理の発生により、 $IRQ_b.F$  フラグがクリアされた。

- ②  $IRQ_a.F$  フラグのクリアと  $IRQ_b$  の発生 ( $IRQ_a.F$  フラグのセット) が競合したとき。

( $IRQ_a.F$  フラグをクリアするための ISR をリードしたときには、 $IRQ_b.F = "0"$  であったが、ISR にライトするまでの期間に  $IRQ_b.F = "1"$  となってしまった状態)

上記の設定条件①～③と発生条件①、②がすべて成立した場合、発生条件②の ISR のライト時に  $IRQ_b.F$  は誤ってクリアされ、割り込み例外処理は実行されません。

ただし、発生条件①、②の間に一度でも  $IRQ_b.F$  フラグに “0” をライトすると、 $IRQ_b.F$  フラグが誤ってクリアされることはありません。

図 5.9 割込み例外処理が実行されない場合の  $IRQ_b.F$  フラグ

このような場合には、以下の対策 1 または 2 を行い、対処してください。

### ■ 対策 1

$IRQ_a.F$  フラグをクリアする際には、ビット演算命令を使用せず、ISR をバイト単位でリードし、 $IRQ_a.F$  フラグだけを “0”、その他のビットは “1” となる値をバイト単位で書き込んでください。

〈例： $a = 0$  の場合〉

```

MOV. B  @ISR, R0L

MOV. B  #HFE, R0L

MOV. B  R0L, @ISR

```

## ■対策 2

I R Q, 割込み例外処理の中で、I R Q, F フラグをクリアするダミー処理を行ってください。

（例：b = 1 の場合）

```

I R Q B      M O V. B  # H F D, R 0 L

M O V. B  R 0 L, @ I S R

:

```