# 6. バスコントローラ

## 第6章 目次

|         |                                |     |

|---------|--------------------------------|-----|

| 6. 1    | 概要                             | 135 |

| 6. 1. 1 | 特長                             | 135 |

| 6. 1. 2 | ブロック図                          | 136 |

| 6. 1. 3 | 端子構成                           | 137 |

| 6. 1. 4 | レジスタ構成                         | 137 |

| 6. 2    | 各レジスタの説明                       | 138 |

| 6. 2. 1 | バス幅コントロールレジスタ (ABWCR)          | 138 |

| 6. 2. 2 | アクセスステートコントロールレジスタ (ASTCR)     | 139 |

| 6. 2. 3 | ウェイトコントロールレジスタ (WCR)           | 140 |

| 6. 2. 4 | ウェイトステートコントローライネーブルレジスタ (WCER) | 141 |

| 6. 2. 5 | バスリリースコントロールレジスタ (BRCR)        | 142 |

| 6. 2. 6 | チップセレクトコントロールレジスタ (CSCR)       | 144 |

| 6. 3    | 動作説明                           | 145 |

| 6. 3. 1 | エリア分割                          | 145 |

| 6. 3. 2 | チップセレクト信号                      | 146 |

| 6. 3. 3 | データバス                          | 147 |

| 6. 3. 4 | バス制御信号タイミング                    | 148 |

| 6. 3. 5 | ウェイトモード                        | 156 |

| 6. 3. 6 | メモリとの接続例                       | 162 |

| 6. 3. 7 | バスアービタの動作                      | 164 |

| 6. 4    | 使用上の注意                         | 167 |

| 6. 4. 1 | DRAMおよびPSRAMの接続                | 167 |

| 6. 4. 2 | レジスタライトタイミング                   | 167 |

| 6. 4. 3 | BREQ端子の入力タイミング                 | 168 |

| 6. 4. 4 | ソフトウェアスタンバイモードへの遷移             | 169 |

## 6.1 概要

H8/3048シリーズはバスコントローラを内蔵しており、外部アドレス空間を8つのエリアに分割し、エリアごとにバス仕様を設定し、バス制御を行います。これにより、複数のメモリを容易に接続することができます。

また、バスコントローラはバス権の調停機能をもっており、DMAコントローラ(DMAC)やリフレッシュコントローラの動作を制御するとともに、外部にバス権を解放することができます。

### 6.1.1 特長

バスコントローラの特長を次に示します。

#### ■ 外部アドレス空間をエリア0～7に分割し、エリアごとに独立して設定可能

- ・1Mバイトモードでは128kバイト、16Mバイトモードでは2Mバイトごとにエリアを設定

- ・エリア0～7に対してチップセレクト( $\overline{CS_0} \sim \overline{CS_7}$ )を出力可能

- ・8ビットアクセス空間／16ビットアクセス空間の選択可能

- ・2ステートアクセス空間／3ステートアクセス空間の選択可能

#### ■ 4種類のウェイトモード

- ・プログラマブルウェイトモード、端子オートウェイトモード、端子ウェイトモード0、1を選択可能

- ・0～3ステートのウェイットステートを自動的に挿入可能

#### ■ バス権調停機能

- ・バスアービタを内蔵し、CPU、DMAC、リフレッシュコントローラ、外部バスマスターのバス権を調停

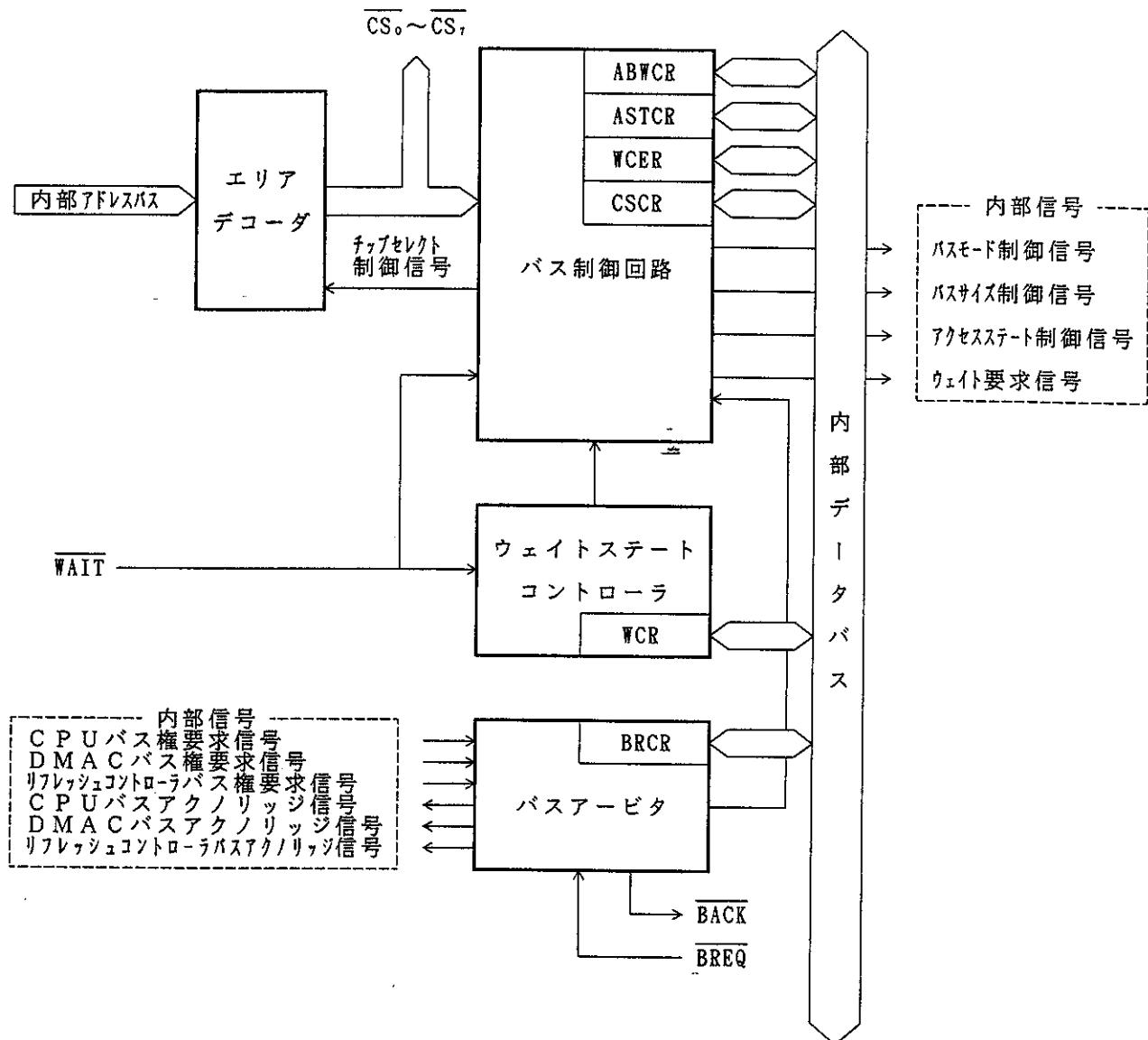

### 6.1.2 ブロック図

バスコントローラのブロック図を図6.1に示します。

#### 《記号説明》

- ABWCR : バス幅コントロールレジスタ

- ASTCR : アクセスステートコントロールレジスタ

- WCER : ウェイタステートコントローラライネーブルレジスタ

- WCR : ウェイタコントロールレジスタ

- BRCR : バスリリースコントロールレジスタ

- CSCR : チップセレクトコントロールレジスタ

図6.1 バスコントローラのブロック図

### 6.1.3 端子構成

バスコントローラの入出力端子を表6.1に示します。

表6.1 端子構成

| 名 称             | 略 称                                    | 入出力 | 機 能                                                              |

|-----------------|----------------------------------------|-----|------------------------------------------------------------------|

| チップセレクト0～7      | $\overline{CS_0} \sim \overline{CS_7}$ | 出力  | エリア0～7が選択されていることを示すストローブ信号                                       |

| アドレスストローブ       | $\overline{AS}$                        | 出力  | アドレスバス上のアドレス出力が有効であることを示すストローブ信号                                 |

| リード             | $\overline{RD}$                        | 出力  | 外部アドレス空間をリードしていることを示すストローブ信号                                     |

| ハイライト           | $\overline{HWR}$                       | 出力  | 外部アドレス空間をライトし、データバスの上位側 ( $D_{15} \sim D_8$ ) が有効であることを示すストローブ信号 |

| ロウライト           | $\overline{LWR}$                       | 出力  | 外部アドレス空間をライトし、データバスの下位側 ( $D_7 \sim D_0$ ) が有効であることを示すストローブ信号    |

| ウェイト            | $\overline{WAIT}$                      | 入力  | 外部3ステートアクセス空間をアクセスするときのウェイト要求信号                                  |

| バス権要求           | $\overline{BREQ}$                      | 入力  | バス権を外部に解放する要求信号                                                  |

| バス権要求<br>アクノリッジ | $\overline{BACK}$                      | 出力  | バス権を外部に解放したことを示すアクノリッジ信号                                         |

### 6.1.4 レジスタ構成

バスコントローラのレジスタ構成を表6.2に示します。

表6.2 レジスタ構成

| アドレス*  | 名 称                     | 略 称   | R/W | 初 期 値          |              |

|--------|-------------------------|-------|-----|----------------|--------------|

|        |                         |       |     | モード1、<br>3、5、6 | モード<br>2、4、7 |

| H'FFEC | バス幅コントロールレジスタ           | ABWCR | R/W | H'FF           | H'00         |

| H'FFED | アクセスステートコントロールレジスタ      | ASTCR | R/W | H'FF           | H'FF         |

| H'FFEE | ウェイトコントロールレジスタ          | WCR   | R/W | H'F3           | H'F3         |

| H'FFEF | ウェイタステートコントローライネーブルレジスタ | WCER  | R/W | H'FF           | H'FF         |

| H'FFF3 | バスリリースコントロールレジスタ        | BRCR  | R/W | H'FE           | H'FE         |

| H'FF5F | チップセレクトコントロールレジスタ       | CSCR  | R/W | H'0F           | H'0F         |

【注】\* アドレスは下位16ビットを示しています。

## 6.2 各レジスタの説明

### 6.2.1 パス幅コントロールレジスタ (ABWCR)

ABWCRは8ビットのリード／ライト可能なレジスタで、各エリアを8ビットアクセス空間または16ビットアクセス空間のいずれかに設定します。

| ビット： | 7                       | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|-------------------------|--------|--------|--------|--------|--------|--------|--------|

|      | ABW7                    | ABW6   | ABW5   | ABW4   | ABW3   | ABW2   | ABW1   | ABW0   |

| 初期値： | {モード1,3,5,6<br>モード2,4,7 | 1<br>0 |

| R/W： | R/W                     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

各エリアのバス幅を選択するビットです。

ABWCRの内容がH'FF（全エリア8ビットアクセス空間）の場合、8ビットバスモードとなり、データバスは上位側（D<sub>15</sub>～D<sub>8</sub>）が有効となります。このときポート4は入出力ポートとなります。ABWCRの少なくとも1ビットを“0”にクリアした場合には、16ビットバスモードとなり、データバスは16ビット（D<sub>15</sub>～D<sub>0</sub>）となります。ABWCRはリセット、またはハードウェアスタンバイモード時にモード1、3、5、6ではH'FFに、モード2、4、7ではH'00にイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

#### ビット7～0：エリア7～0バス幅コントロール (ABW7～ABW0)

対応するエリアを8ビットアクセス空間とするか16ビットアクセス空間とするかを選択します。

| ビット7～0    | 説明                    |

|-----------|-----------------------|

| ABW7～ABW0 |                       |

| 0         | エリア7～0を16ビットアクセス空間に設定 |

| 1         | エリア7～0を8ビットアクセス空間に設定  |

ABWCRは、外部メモリ空間のデータバス幅を指定します。内蔵メモリ、内部I/Oレジスタのデータバス幅はABWCRの設定値にかかわらず固定です。したがって、シングルチップモード（モード7）では設定値には意味がありません。

## 6.2.2 アクセスステートコントロールレジスタ (A S T C R)

A S T C R は 8 ビットのリード／ライト可能なレジスタで、各エリアを 2 ステートアクセス空間または 3 ステートアクセス空間のいずれかに設定します。

| ビット : | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

|       | AST7 | AST6 | AST5 | AST4 | AST3 | AST2 | AST1 | AST0 |

| 初期値 : | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| R／W : | R／W  |

各エリアのアクセスステート数を選択するビットです。

A S T C R はリセット、またはハードウェアスタンバイモード時に、H'FFにイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

ビット 7～0 : エリア 7～0 アクセスステートコントロール (A S T 7～A S T 0)

対応するエリアを 2 ステートアクセス空間とするか 3 ステートアクセス空間とするかを選択します。

| ビット 7～0         | 説明                              |

|-----------------|---------------------------------|

| A S T 7～A S T 0 |                                 |

| 0               | エリア 7～0 を 2 ステートアクセス空間に設定       |

| 1               | エリア 7～0 を 3 ステートアクセス空間に設定 (初期値) |

A S T C R は、外部メモリ空間のアクセスステート数を設定します。内蔵メモリ、内部 I／O レジスタに対するアクセスステート数は A S T C R の設定値にかかわらず固定です。したがって、シングルチップモード (モード 7) では設定値には意味がありません。

### 6.2.3 ウェイトコントロールレジスタ (WCR)

WCRは8ビットのリード/ライト可能なレジスタで、ウェイトステートコントローラ(WSC)のウェイトモードとウェイトステート数を設定します。

| ビット: | 7 | 6 | 5 | 4 | 3    | 2    | 1   | 0   |

|------|---|---|---|---|------|------|-----|-----|

| 初期値: | — | — | — | — | WMS1 | WMS0 | WC1 | WC0 |

| R/W: | 1 | 1 | 1 | 1 | 0    | 0    | 1   | 1   |

|      | — | — | — | — | R/W  | R/W  | R/W | R/W |

リザーブビット

ウェイトカウント1、0

握入するウェイトステート数を

設定するビットです。

ウェイトモードセレクト1、0

ウェイトモードを設定するビットです。

WCRはリセット、またはハードウェアスタンバイモード時にH'F3にイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

#### ビット7～4：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です

ビット3、2：ウェイトモードセレクト1、0 (WMS1、0)

ウエイトモードを設定します。

| ビット3    | ビット2    | 説明                       |       |

|---------|---------|--------------------------|-------|

| W M S 1 | W M S 0 |                          |       |

| 0       | 0       | プログラマブルウェイトモード           | (初期値) |

| 0       | 1       | ウェイトステートコントローラによるウェイトを禁止 |       |

| 1       | 0       | 端子ウェイトモード1               |       |

| 1       | 1       | 端子オートウェイトモード             |       |

ビット1、0：ウェイトカウント1、0 (W C 1、0)

外部3ステートアクセス空間をアクセスするときに、挿入するウェイトステート数を設定します。

| ビット1  | ビット0  | 説明               |

|-------|-------|------------------|

| W C 1 | W C 0 |                  |

| 0     | 0     | W S Cによるウェイトを禁止  |

| 0     | 1     | 1ステート挿入          |

| 1     | 0     | 2ステート挿入          |

| 1     | 1     | 3ステート挿入<br>(初期値) |

#### 6.2.4 ウェイトステートコントローライネーブルレジスタ (W C E R)

W C E Rは8ビットのリード／ライト可能なレジスタで、外部3ステートアクセス空間について、W S Cの動作を許可／禁止します。

| ビット  | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|------|---------|---------|---------|---------|---------|---------|---------|---------|

|      | W C E 7 | W C E 6 | W C E 5 | W C E 4 | W C E 3 | W C E 2 | W C E 1 | W C E 0 |

| 初期値： | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       |

R/W : R/W R/W R/W R/W R/W R/W R/W R/W R/W

ウェイトステートコントローライネーブル7～0

W S Cの動作を許可／禁止するビットです。

W C E Rはリセット、またはハードウェアスタンバイモード時にH'FFにイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

#### ビット7～0：ウェイトステートコントローライネーブル7～0 (W C E 7～W C E 0)

外部3ステートアクセス空間について、W S Cの動作を許可／禁止します。

| ビット7～0          | 説明                       |

|-----------------|--------------------------|

| W C E 7～W C E 0 |                          |

| 0               | W S Cの動作を禁止 (端子ウェイトモード0) |

| 1               | W S Cの動作を許可<br>(初期値)     |

W C E Rは、外部3ステートアクセス空間についてW S Cの動作を許可／禁止します。したがって、シングルチップモード(モード7)では設定値に意味はありません。

### 6.2.5 バスリリースコントロールレジスタ (B R C R)

B R C R は 8 ビットのリード／ライト可能なレジスタで、アドレスバス( $A_{23} \sim A_{21}$ )出力の選択、バス権の外部に対する解放を許可／禁止します。

ビット：

|                 | 7    | 6    | 5    | 4 | 3 | 2 | 1 | 0    |

|-----------------|------|------|------|---|---|---|---|------|

|                 | A23E | A22E | A21E | — | — | — | — | BRLE |

| 初期値             | 1    | 1    | 1    | 1 | 1 | 1 | 1 | 0    |

| モード 1,2,5,7 R/W | —    | —    | —    | — | — | — | — | R/W  |

| モード 3,4,6 R/W   | R/W  | R/W  | R/W  | — | — | — | — | R/W  |

リザーブビット

アドレス23～21イネーブル

PA<sub>6</sub>～PA<sub>4</sub> をアドレス出力端子

$A_{23} \sim A_{21}$  として使用するため

のビットです。

バスリリースイネーブル

バス権の外部に対する解放を

許可／禁止するビットです

B R C R はリセット、またはハードウェアスタンバイモード時にH'FEにイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

#### ビット7：アドレス23イネーブル (A23E)

PA<sub>4</sub>をアドレス出力端子A<sub>23</sub>として使用するためのビットです。“0”をライトするとPA<sub>4</sub>はアドレス出力A<sub>23</sub>となります。モード3、4、6以外ではこのビットはライトできず、PA<sub>4</sub>は通常のポート機能となります。

| ビット7 | 説明                                                             |       |

|------|----------------------------------------------------------------|-------|

| A23E |                                                                |       |

| 0    | PA <sub>4</sub> はアドレス出力端子A <sub>23</sub>                       |       |

| 1    | PA <sub>4</sub> はPA <sub>4</sub> /TP4/TIOCA <sub>1</sub> 入出力端子 | (初期値) |

#### ビット 6 : アドレス22イネーブル (A 22E)

PA<sub>5</sub>をアドレス出力端子A<sub>22</sub>として使用するためのビットです。“0”をライトするとPA<sub>5</sub>はアドレス出力A<sub>22</sub>となります。モード3、4、6以外ではこのビットはライトできず、PA<sub>5</sub>は通常のポート機能となります。

| ビット 6 | 説明                                                                          |       |

|-------|-----------------------------------------------------------------------------|-------|

| A 22E |                                                                             |       |

| 0     | PA <sub>5</sub> はアドレス出力端子A <sub>22</sub>                                    |       |

| 1     | PA <sub>5</sub> はPA <sub>5</sub> /TP <sub>5</sub> /TIOCB <sub>1</sub> 入出力端子 | (初期値) |

#### ビット 5 : アドレス21イネーブル (A 21E)

PA<sub>6</sub>をアドレス出力端子A<sub>21</sub>として使用するためのビットです。“0”をライトするとPA<sub>6</sub>はアドレス出力A<sub>21</sub>となります。モード3、4、6以外ではこのビットはライトできず、PA<sub>6</sub>は通常のポート機能となります。

| ビット 5 | 説明                                                                          |       |

|-------|-----------------------------------------------------------------------------|-------|

| A 21E |                                                                             |       |

| 0     | PA <sub>6</sub> はアドレス出力端子A <sub>21</sub>                                    |       |

| 1     | PA <sub>6</sub> はPA <sub>6</sub> /TP <sub>6</sub> /TIOCA <sub>2</sub> 入出力端子 | (初期値) |

#### ビット 4～1 : リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット 0 : バスリリースイネーブル (B R L E)

バス権の外部に対する解放を許可／禁止します。

| ビット 0   | 説明                                       |       |

|---------|------------------------------------------|-------|

| B R L E |                                          |       |

| 0       | バス権の外部に対する解放を禁止し、BREQ、BACK端子は入出力端子として使用可 | (初期値) |

| 1       | バス権の外部に対する解放を許可                          |       |

### 6.2.6 チップセレクトコントロールレジスタ (CSCR)

CSCR は 8 ビットのリード／ライト可能なレジスタで、チップセレクト信号( $\overline{CS_1}$ ～ $\overline{CS_4}$ )の出力を許可／禁止します。

本レジスタでチップセレクト信号( $\overline{CS_1}$ ,  $\overline{CS_2}$ )出力を選択すると、端子機能は他の機能に優先してチップセレクト信号( $\overline{CS_1}$ ,  $\overline{CS_2}$ )出力となります。なお、本レジスタはシングルチップモードではライトできません。

| ビット: | 7                | 6    | 5    | 4   | 3       | 2 | 1 | 0 |

|------|------------------|------|------|-----|---------|---|---|---|

| CS7E | CS6E             | CS5E | CS4E | —   | —       | — | — | — |

| 初期値: | 0                | 0    | 0    | 0   | 1       | 1 | 1 | 1 |

| R/W: | R/W              | R/W  | R/W  | R/W | —       | — | — | — |

|      |                  |      |      |     |         |   |   |   |

|      | チップセレクト7～4イネーブル  |      |      |     | リザーブビット |   |   |   |

|      | チップセレクト信号の出力を許可／ |      |      |     | —       |   |   |   |

|      | 禁止するビットです。       |      |      |     | —       |   |   |   |

C S C R はリセット、またはハードウェアスタンバイモード時にH'0Fにイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

ビット7～4：チップセレクト7～4イネーブル (CS7E～CS4E)

対応するチップセレクト信号の出力を許可／禁止します。

| ビットn    | 説明                       |       |

|---------|--------------------------|-------|

| C S n E |                          |       |

| 0       | チップセレクト信号 (C S n) の出力を禁止 | (初期値) |

| 1       | チップセレクト信号 (C S n) の出力を許可 |       |

【注】  $n = 7 \sim 4$

### リザーブド・マーク

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

## 6.3 動作説明

### 6.3.1 エリア分割

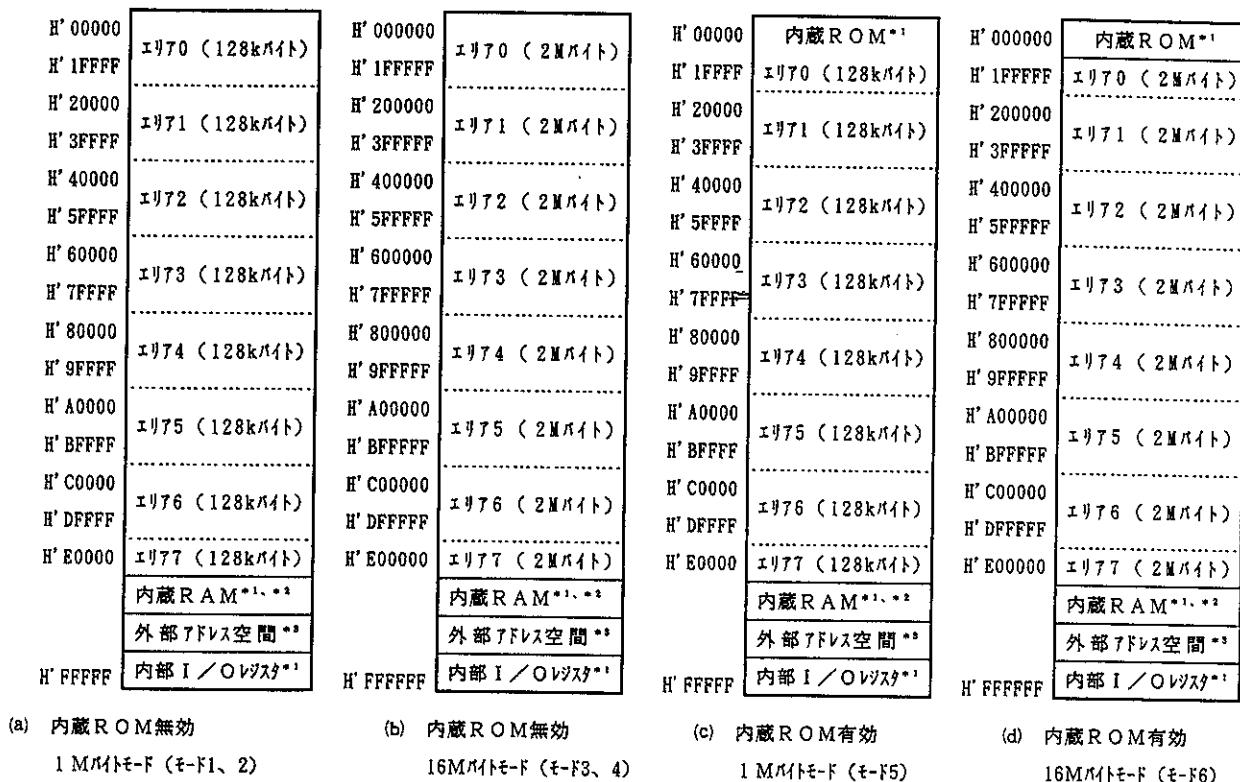

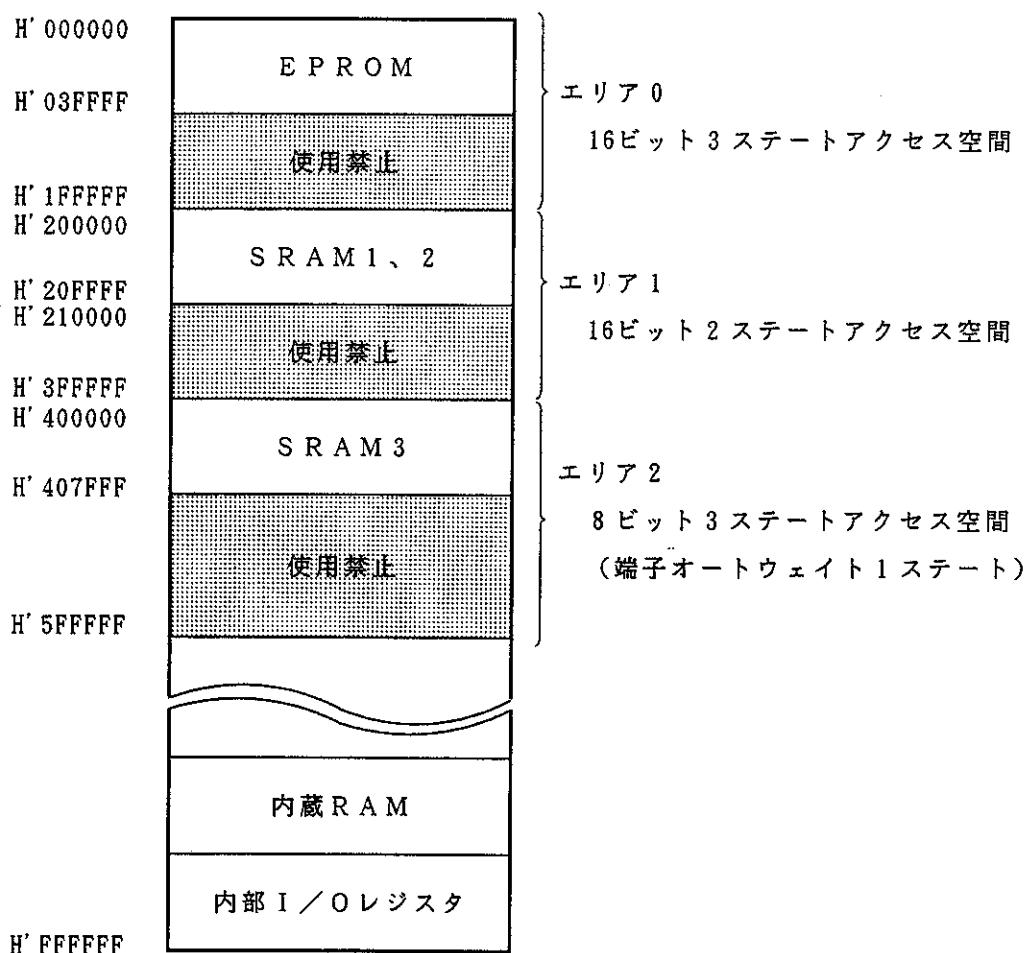

外部アドレス空間は、1Mバイトモードのとき128kバイト、16Mバイトモードのとき2Mバイトごとのエリア0～7に分割されています。メモリマップの概要を図6.2に示します。

【注】<sup>\*1</sup> 内蔵ROM、内蔵RAM、内部I/Oレジスタのバス幅、アクセスステート数は固定です。

<sup>\*2</sup> SYSCRのRAMEビットを“0”にクリアするとエリア7の指定に従います。

<sup>\*3</sup> 外部アドレス空間は、エリア7の指定に従います。

図6.2 各動作モードにおけるアクセスエリアマップ

各エリアごとに選択信号 (CS<sub>0</sub>～CS<sub>7</sub>) を出力することができます。また、各エリアのバス仕様は、ABWCR、ASTCR、WCER、WCRで指定されます。

各エリアのバス仕様を表6.3に示します。

表 6.3 各エリアのバス仕様

| ABWCR | ASTCR | WCER | W C R |      | バス仕様 |      |      |                |              |

|-------|-------|------|-------|------|------|------|------|----------------|--------------|

|       |       |      | ABWn  | ASTn | WCEn | WMS1 | WMS0 | バス幅            | アクセス<br>ステート |

| 0     | 0     | —    | —     | —    | —    | 16   | 2    | 禁止             |              |

|       | 1     | 0    | —     | —    | —    | 16   | 3    | 端子ウェイトモード0     |              |

|       | 1     | 1    | 0     | 0    | 0    | 16   | 3    | プログラマブルウェイトモード |              |

|       |       |      | 0     | 1    | 1    | 16   | 3    | 禁止             |              |

|       |       |      | 1     | 0    | 0    | 16   | 3    | 端子ウェイトモード1     |              |

|       |       |      | 1     | 1    | 1    | 16   | 3    | 端子オートウェイトモード   |              |

|       |       |      | 0     | —    | —    | 8    | 2    | 禁止             |              |

| 1     | 1     | 0    | —     | —    | —    | 8    | 3    | 端子ウェイトモード0     |              |

|       | 1     | 1    | 0     | 0    | 0    | 8    | 3    | プログラマブルウェイトモード |              |

|       |       |      | 0     | 1    | 1    | 8    | 3    | 禁止             |              |

|       |       |      | 1     | 0    | 0    | 8    | 3    | 端子ウェイトモード1     |              |

|       |       |      | 1     | 1    | 1    | 8    | 3    | 端子オートウェイトモード   |              |

【注】 n = 0 ~ 7

### 6.3.2 チップセレクト信号

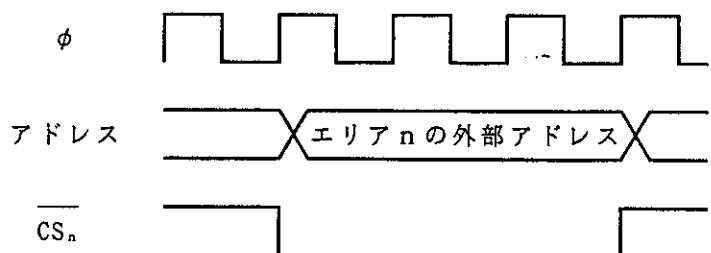

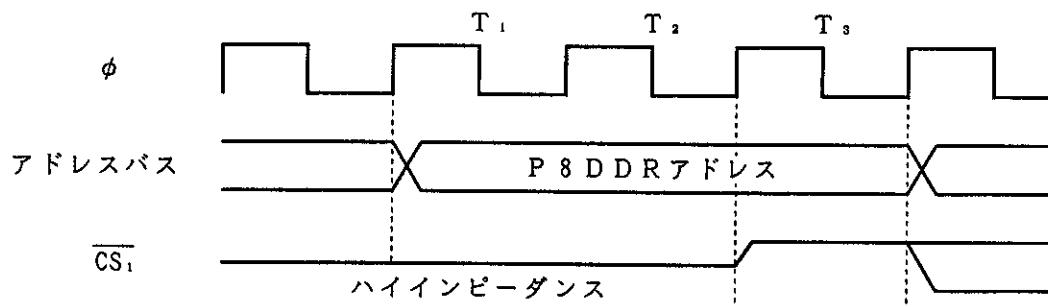

本LSIは、エリア0~7に対してそれぞれチップセレクト信号( $\overline{CS}_0 \sim \overline{CS}_7$ )を出力することができます、拡張モードで当該エリアが選択されたとき、“Low”レベルを出力します。図6.3に $\overline{CS}_n$ 信号出力タイミングを示します。

#### (1) $\overline{CS}_0 \sim \overline{CS}_3$ 出力方法

$\overline{CS}_0 \sim \overline{CS}_3$ の出力の許可または禁止は各 $\overline{CS}_n$ 端子に対応するポートのデータディレクションレジスタ(DDR)を設定することにより行います。

内蔵ROM無効拡張モード時、 $\overline{CS}_0$ 端子はリセット直後に出力状態となっています。 $\overline{CS}_1 \sim \overline{CS}_3$ 端子はリセット直後に入力状態となっていますので、 $\overline{CS}_1 \sim \overline{CS}_3$ を出力する場合には対応するDDRを“1”にセットしてください。内蔵ROM有効拡張モード時、 $\overline{CS}_0 \sim \overline{CS}_3$ 端子はリセット直後に入力状態となっていますので、 $\overline{CS}_0 \sim \overline{CS}_3$ を出力する場合には、対応するDDRを“1”にセットしてください。

詳細は「第9章 I/Oポート」を参照してください。

#### (2) $\overline{CS}_4 \sim \overline{CS}_7$ 出力方法

$\overline{CS}_4 \sim \overline{CS}_7$ の出力許可または禁止はチップセレクトコントロールレジスタ(CSCR)を設定することにより行います。 $\overline{CS}_4 \sim \overline{CS}_7$ 端子はリセット直後に入力状態となっていますので、 $\overline{CS}_4 \sim \overline{CS}_7$ 端子を出力する場合にはCSCRの対応するビットを“1”にセットしてください。詳細は「第9章 I/Oポート」を参照してください。

図 6.3  $\overline{CS_n}$  信号の出力タイミング ( $n = 0 \sim 7$ )

内蔵ROM、内蔵RAMおよび内部I/Oレジスタを選択した場合、 $\overline{CS_0}$ 、 $\overline{CS_1}$ 端子は“High”レベルです。 $\overline{CS_n}$ 信号はアドレスをデコードした信号で、SRAMなどのチップセレクト信号として使用することができます。

### 6.3.3 データバス

本LSIは、エリア0～7をそれぞれ8ビットアクセス空間または16ビットアクセス空間のいずれかに設定することができます。8ビットアクセス空間では、データバスの上位側( $D_{15} \sim D_8$ )を使用します。また16ビットアクセス空間ではデータバスの上位側( $D_{15} \sim D_8$ )、下位側( $D_7 \sim D_0$ )を使用します。

リード時には、データバスの上位側、下位側の区別なく、 $\overline{RD}$ 信号が有効です。

ライト時にはデータバスの上位側に対してHWR信号が、データバスの下位側に対してLWR信号が有効です。

表6.4にアクセス空間と使用するデータバスを示します。

表 6.4 アクセス空間と使用するデータバス

| エリア             | アクセス<br>サイズ | リード/<br>ライト | アドレス | 有効な<br>ストローブ                        | データバス上位<br>( $D_{15} \sim D_8$ ) | データバス下位<br>( $D_7 \sim D_0$ ) |

|-----------------|-------------|-------------|------|-------------------------------------|----------------------------------|-------------------------------|

| 8ビット<br>アクセス空間  | —           | リード         | —    | $\overline{RD}$                     | 有効                               | 無効                            |

|                 |             | ライト         | —    | $\overline{HWR}$                    |                                  | 不定                            |

| 16ビット<br>アクセス空間 | バイト         | リード         | 偶数   | $\overline{RD}$                     | 有効                               | 無効                            |

|                 |             |             | 奇数   |                                     | 無効                               | 有効                            |

|                 |             | ライト         | 偶数   | $\overline{HWR}$                    | 有効                               | 不定                            |

|                 |             |             | 奇数   | $\overline{LWR}$                    | 不定                               | 有効                            |

|                 | ワード         | リード         | —    | $\overline{RD}$                     | 有効                               | 有効                            |

|                 |             | ライト         | —    | $\overline{HWR}$ 、 $\overline{LWR}$ | 有効                               | 有効                            |

【注】 不定：不定データが出力されます。

無効：入力状態であり、入力値は無視されます。

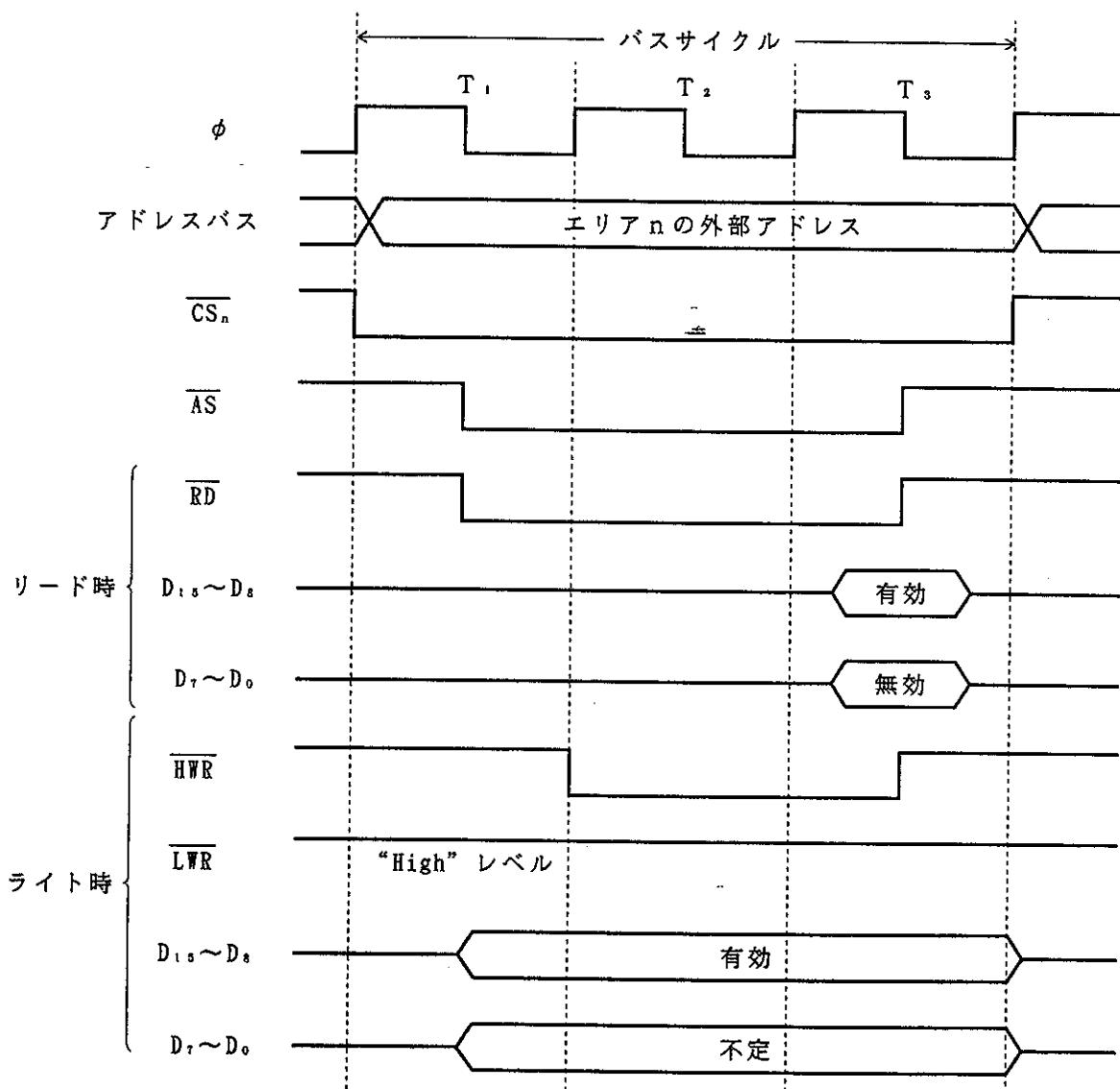

### 6.3.4 バス制御信号タイミング

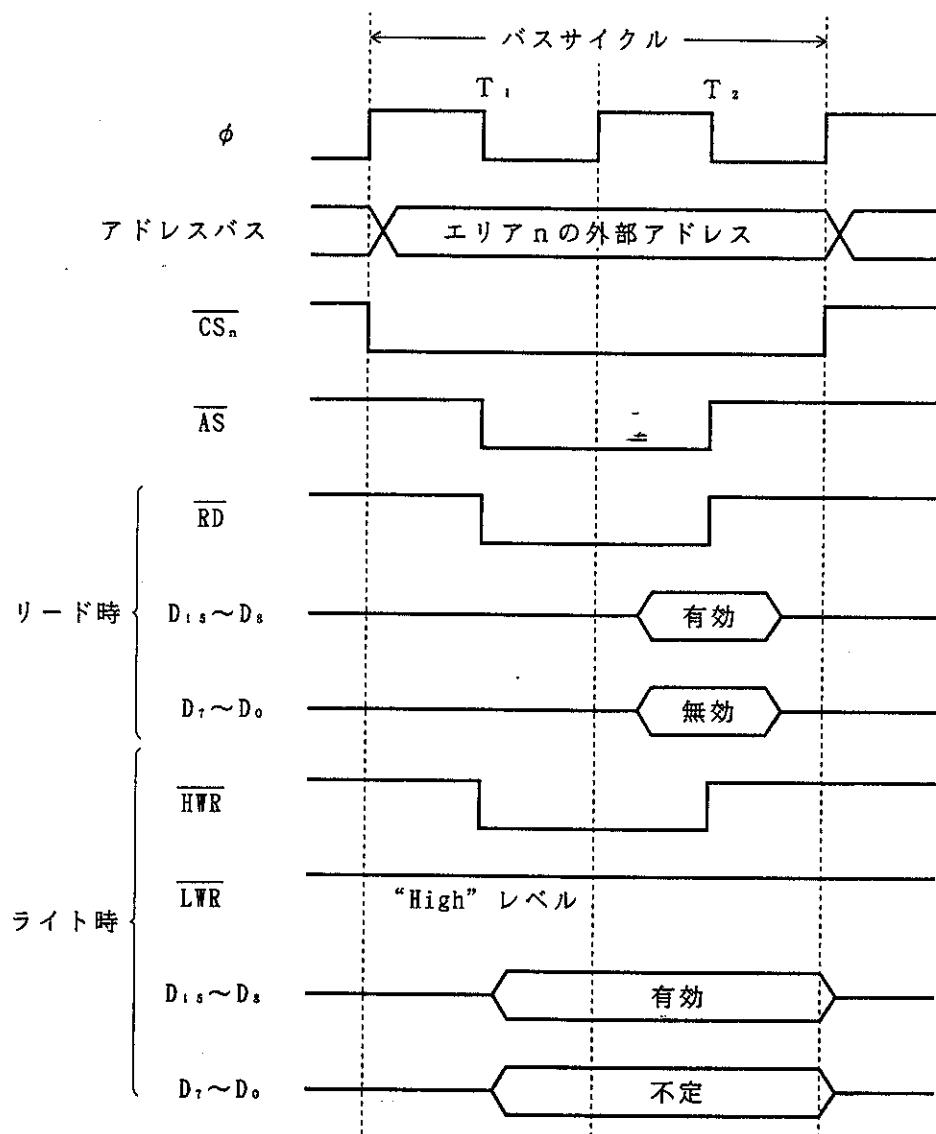

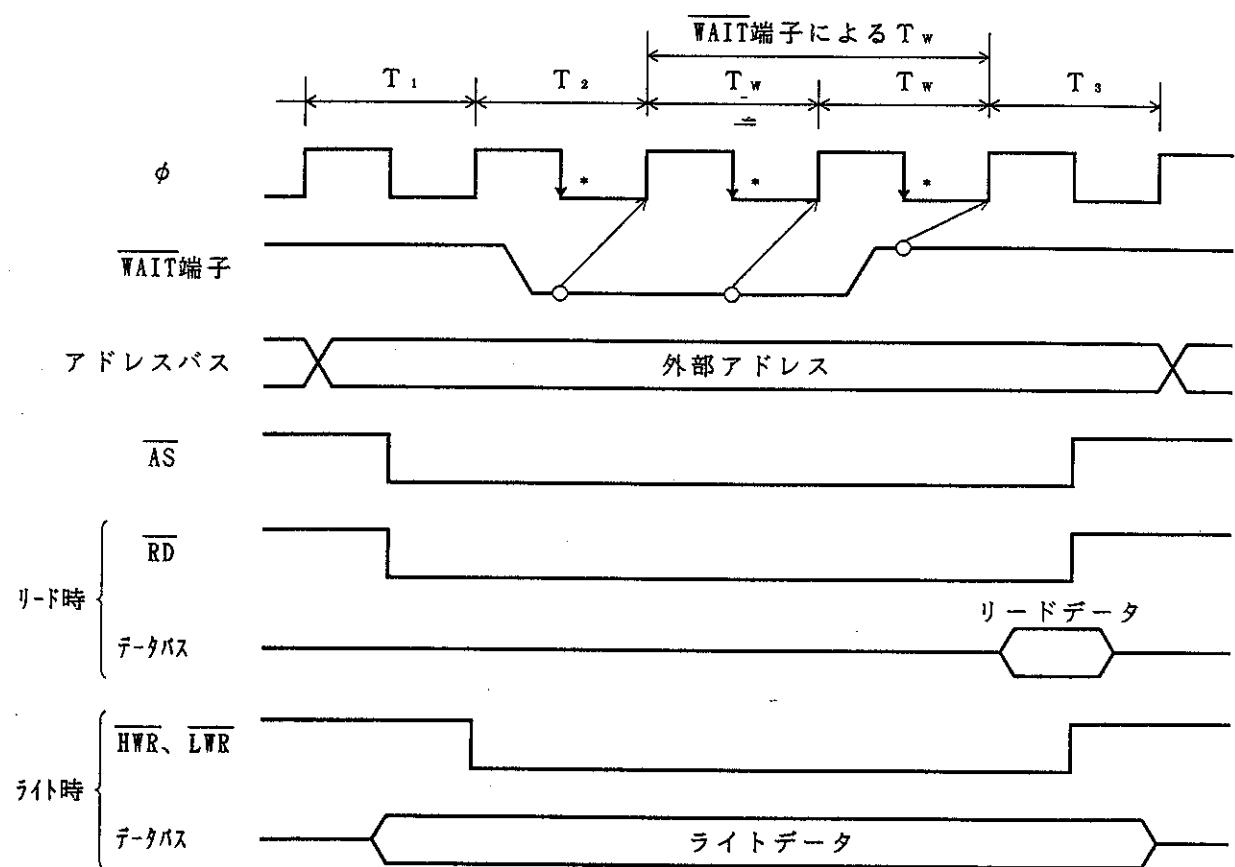

#### (1) 8ビット3ステートアクセス空間

図6.4に8ビット3ステートアクセス空間のバス制御信号タイミングを示します。8ビットアクセス空間をアクセスする場合データバスの上位側 ( $D_{15} \sim D_8$ ) を使用します。

LWR端子は常に“High”レベルとなっています。ウェイタステートを挿入することができます。

【注】  $n = 7 \sim 0$

図6.4 8ビット3ステートアクセス空間のバス制御信号タイミング

(2) 8 ビット 2 ステートアクセス空間

図 6.5 に 8 ビット 2 ステート空間のバス制御信号タイミングを示します。8 ビットアクセス空間をアクセスする場合データバスの上位側 ( $D_{15} \sim D_8$ ) を使用します。

LWR端子は常に "High" レベルとなっています。ウェイトステートを挿入することはできません。

【注】  $n = 7 \sim 0$

図 6.5 8 ビット 2 ステートアクセス空間のバス制御信号タイミング

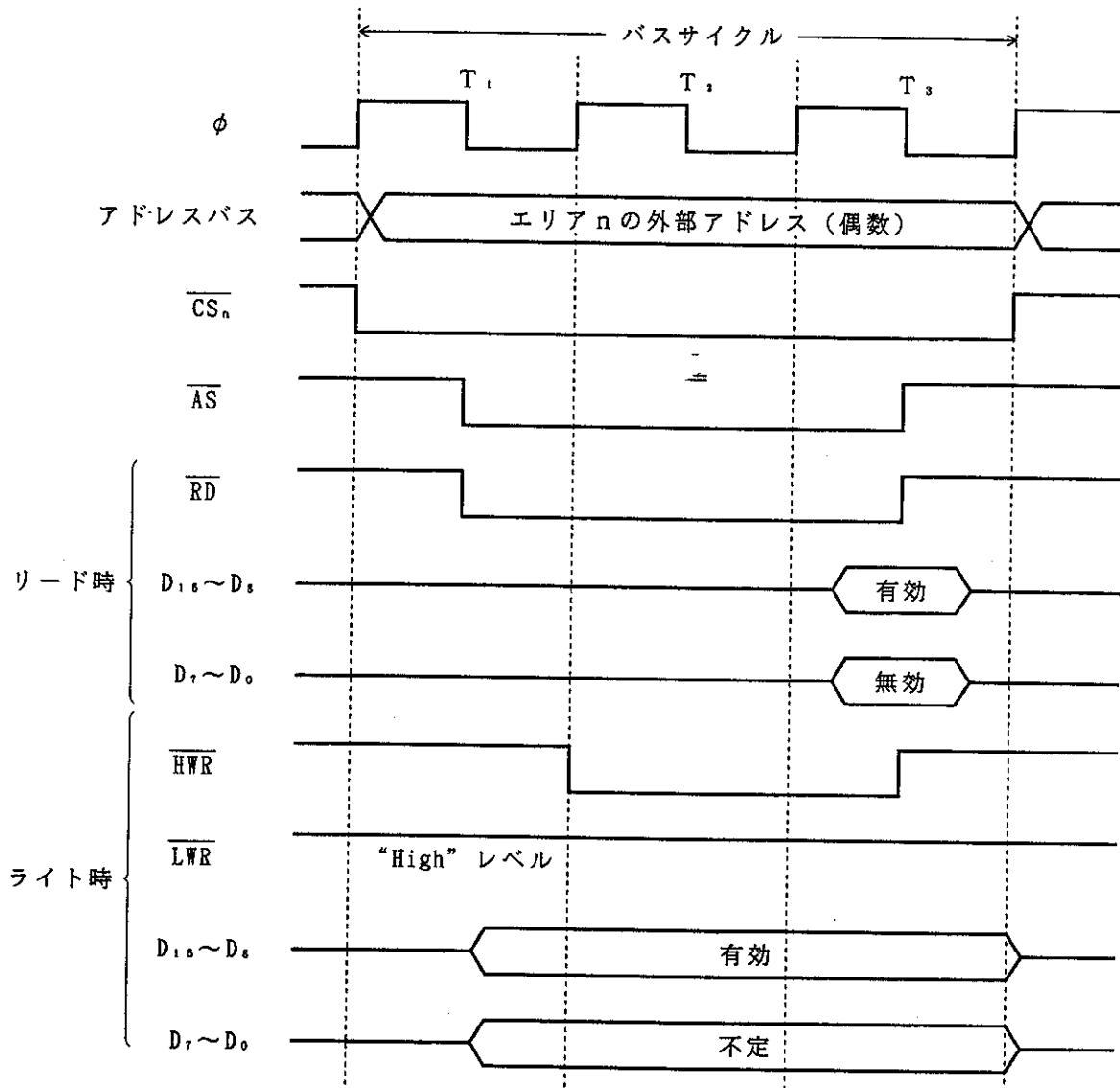

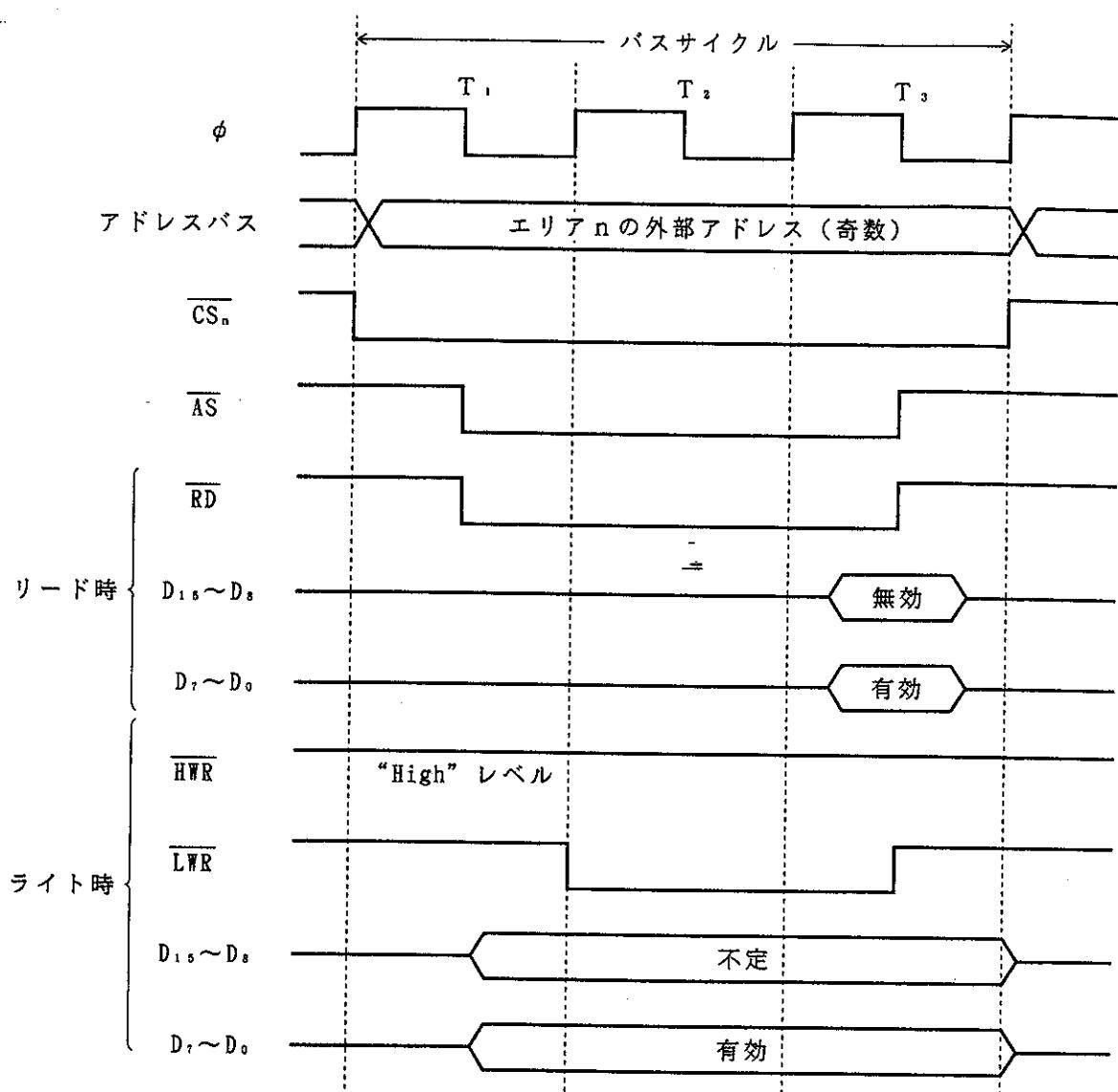

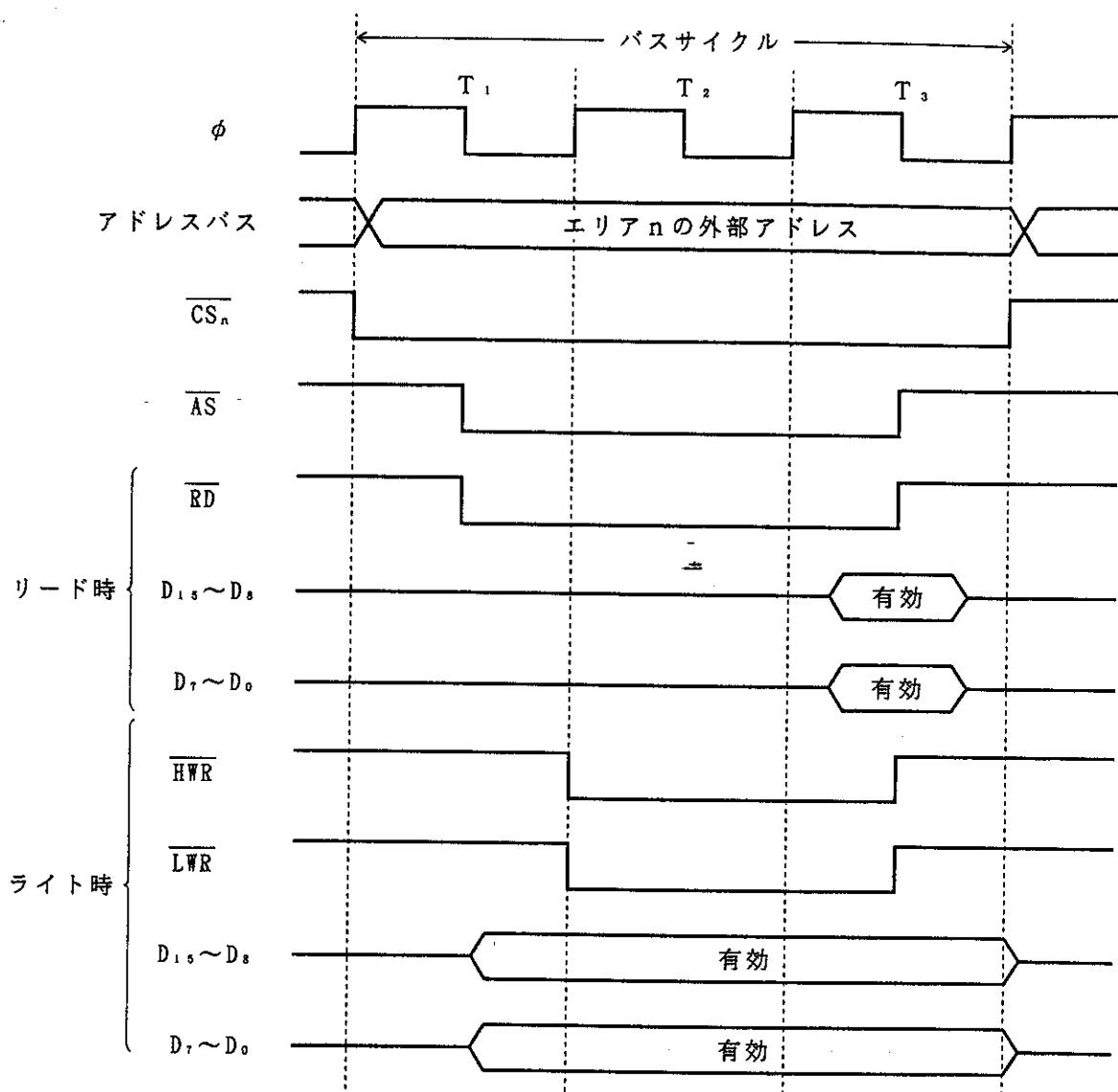

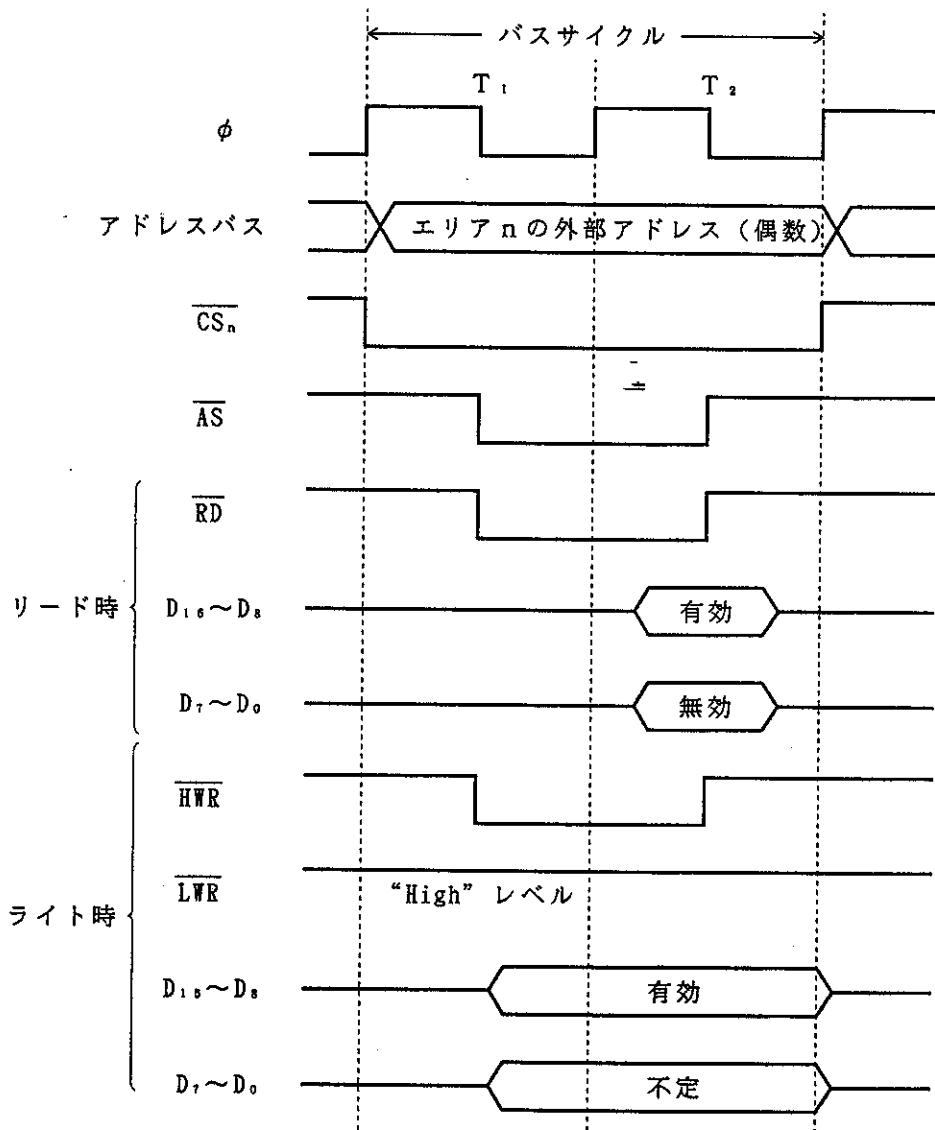

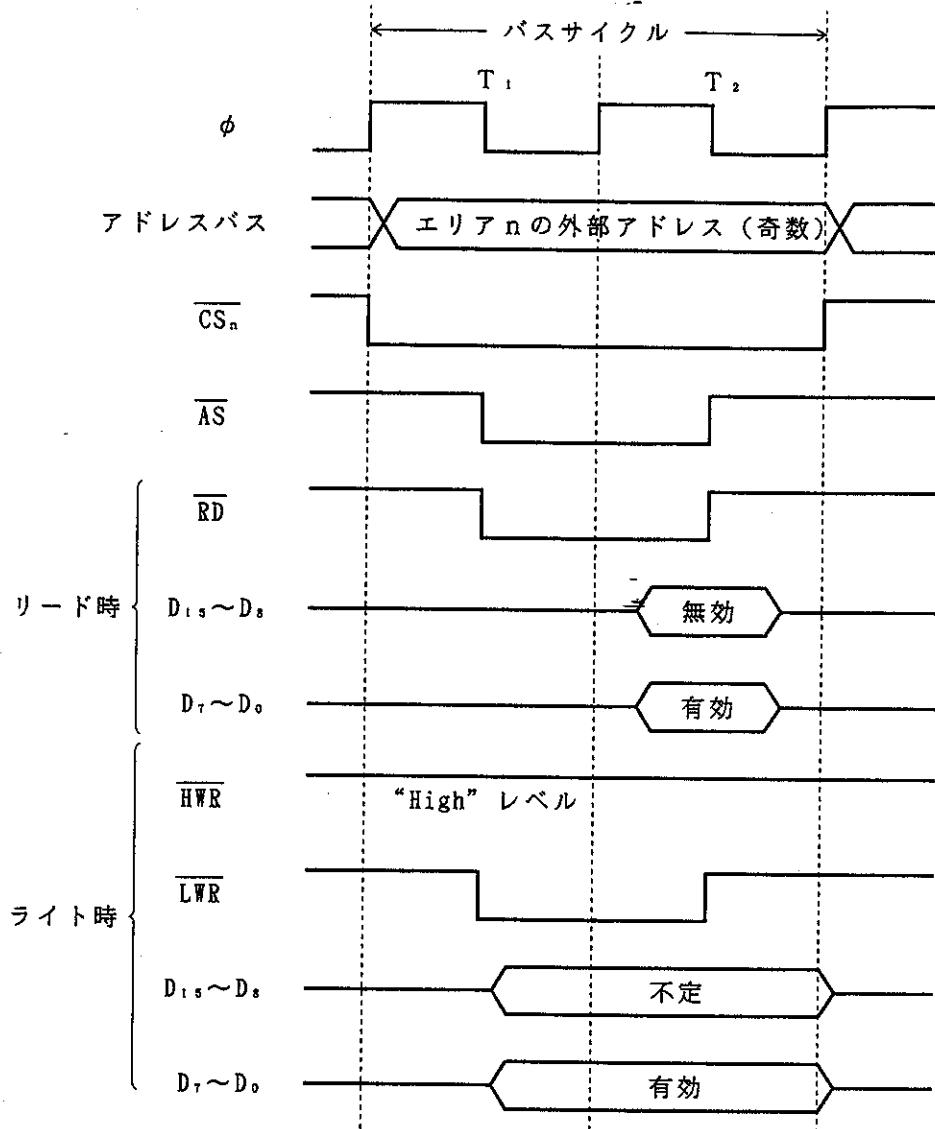

(3) 16ビット3ステートアクセス空間

図6.6～図6.8に16ビット3ステートアクセス空間のバス制御信号タイミングを示します。16ビットアクセス空間をアクセスする場合偶数アドレスに対しては、データバスの上位側 ( $D_{15} \sim D_8$ ) を使用し、奇数アドレスに対してはデータバスの下位側 ( $D_7 \sim D_0$ ) を使用します。ウェイトステートを挿入することができます。

【注】  $n = 7 \sim 0$

図6.6 16ビット3ステートアクセス空間のバス制御信号タイミング(1)

(偶数アドレスバイトアクセス)

【注】  $n = 7 \sim 0$

図 6.7 16ビット 3ステートアクセス空間のバス制御信号タイミング(2)

(奇数アドレスバイトアクセス)

【注】  $n = 7 \sim 0$

図 6.8 16ビット3ステートアクセス空間のバス制御信号タイミング(3)

(ワードアクセス)

(4) 16ビット2ステートアクセス空間

図6.9～図6.11に16ビット2ステートアクセス空間のバス制御信号タイミングを示します。16ビットアクセス空間をアクセスする場合、偶数アドレスに対してはデータバスの上位側 ( $D_{15} \sim D_8$ ) を使用し、奇数アドレスに対してはデータバスの下位側 ( $D_7 \sim D_0$ ) を使用します。ウェイトステートを挿入することはできません。

【注】  $n = 7 \sim 0$

図6.9 16ビット2ステートアクセス空間のバス制御信号タイミング(1)

(偶数アドレスバイトアクセス)

【注】  $n = 7 \sim 0$

図 6.10 16ビット 2ステートアクセス空間のバス制御信号タイミング(2)

(奇数アドレスバイトアクセス)

【注】  $n = 7 \sim 0$

図 6.11 16ビット 2ステートアクセス空間のバス制御信号タイミング(3)

(ワードアクセス)

### 6.3.5 ウェイトモード

ウェイトモードには、4種類のモードがあります。ウェイトモードの選択方法を表6.5に示します。

表6.5 ウェイトモードの選択

| ASTCR | WCER | W C R   |         | WSC動作 | ウェイトモード        |

|-------|------|---------|---------|-------|----------------|

|       |      | WCEnビット | WMS1ビット |       |                |

| 0     | —    | —       | —       | 禁止    | ウェイト禁止         |

| 1     | 0    | —       | —       | 禁止    | 端子ウェイトモード0     |

| 1     | 1    | 0       | 0       | 許可    | プログラマブルウェイトモード |

|       |      | 0       | 1       | 許可    | ウェイト禁止         |

|       |      | 1       | 0       | 許可    | 端子ウェイトモード1     |

|       |      | 1       | 1       | 許可    | 端子オートウェイトモード   |

【注】 n = 7 ~ 0

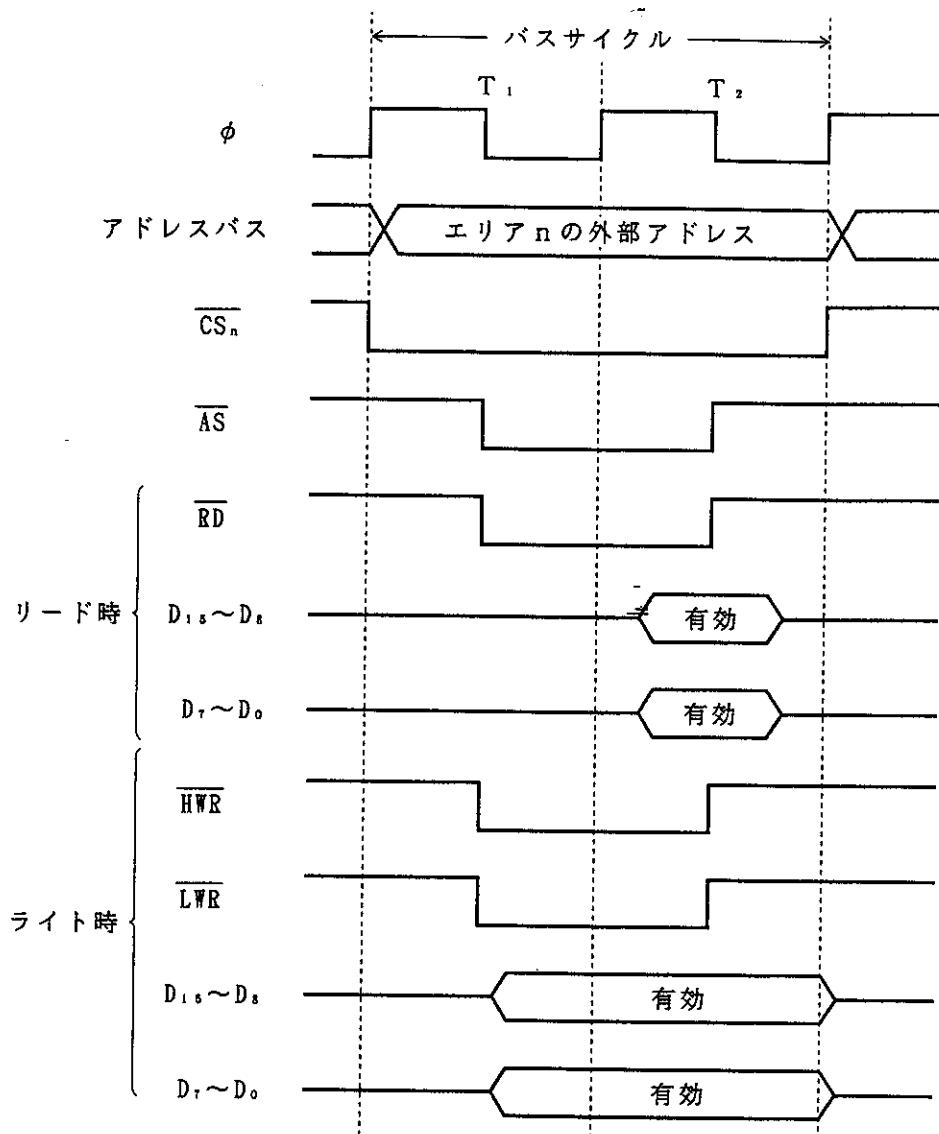

(1) WSC動作を禁止したエリアのウェイトモード

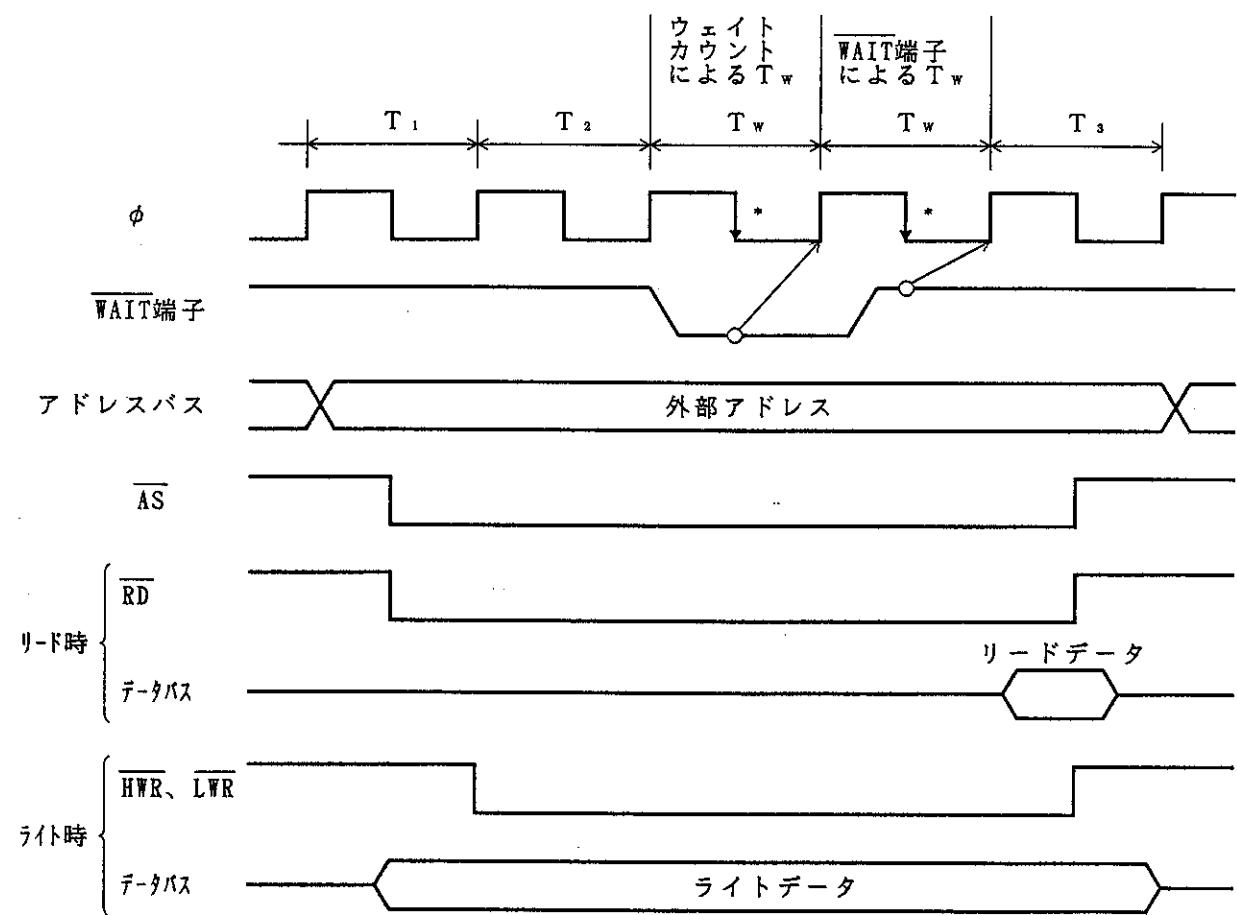

WSCの動作を禁止した外部3ステートアクセス空間 ( $AST_n = 1, WCE_n = 0$ ) では端子ウェイトモード0によるウェイトステートの挿入が可能です。他のウェイトモードは使用できません。また、WMS1、0ビットの設定はWSCの動作を禁止したエリアでは意味がありません。

・ 端子ウェイトモード0

端子ウェイトモード0では、WAIT端子によるウェイトステートのみが挿入されます。外部3ステートアクセス空間をアクセスするとき、 $T_2$ ステートの $\phi$ の立下がりのタイミングでWAIT端子が“Low”レベルであると、 $T_w$ ステートが挿入されます。WAIT端子が“Low”レベルに保持されるとWAIT端子が“High”レベルに立上がるまで $T_w$ が挿入されます。

このタイミングを図6.12に示します。

【注】\* 矢印はWAIT端子のサンプリングタイミングを示します。

図6.12 端子ウェイトモード0

## (2) W S C 動作を許可したエリアのウェイトモード

W S C の動作を許可した外部 3 ステートアクセス空間 ( $A S T n = 1$ ,  $W C E n = 1$ ) では WMS1、0 ビットにより端子ウェイトモード1、端子オートウェイトモード、プログラマブルウェイトモードの中からウェイトモードを選択できます。ただし WMS1、0 ビットは各エリアに共通ですので、W S C の動作を許可したエリアのウェイトモードは同一になります。

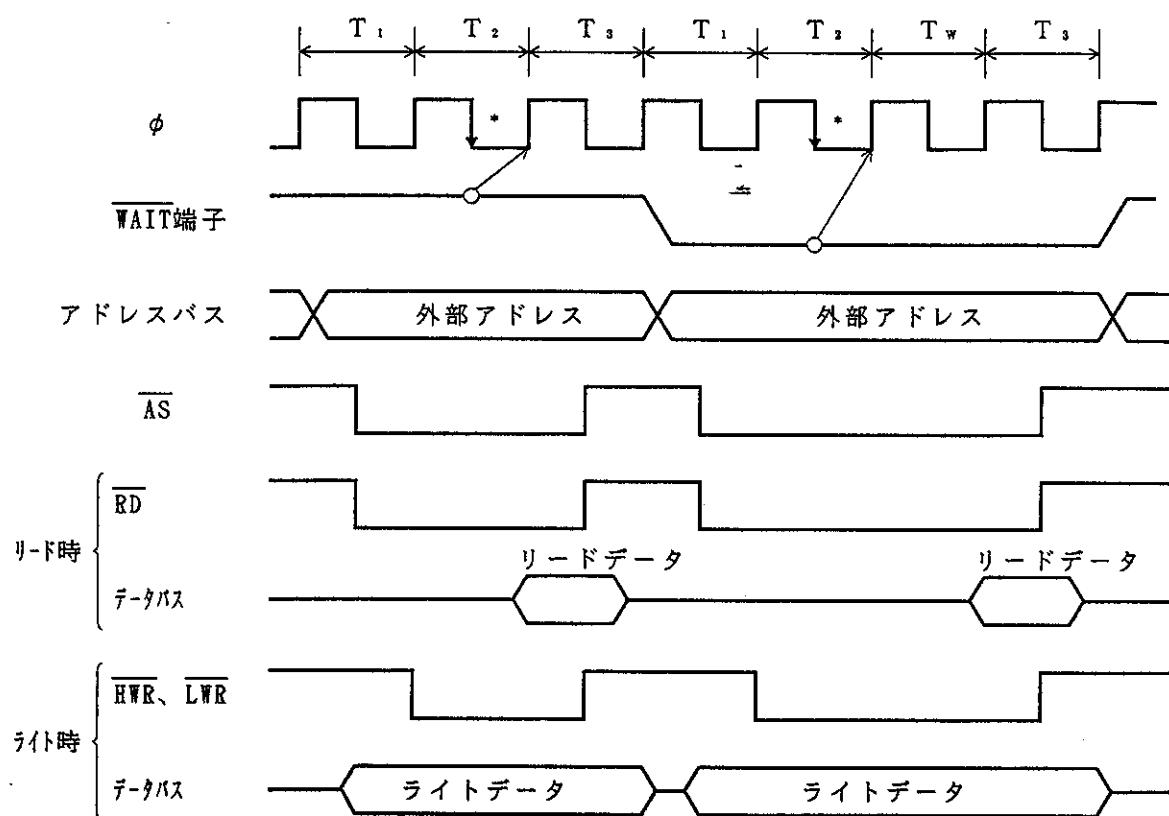

### (a) 端子ウェイトモード1

端子ウェイトモード1では、外部 3 ステートアクセス空間をアクセスすると、常に  $W C 1$ 、0 ビットにより設定されたステート数だけ  $T_w$  が挿入されます。この最後の  $T_w$  の立下がりのタイミングで WAIT 端子を “Low” レベルにすることで、さらに  $T_w$  を挿入することができます。WAIT 端子が “Low” レベルに保持されると、WAIT 端子が “High” レベルに立上がるまで  $T_w$  が挿入されます。

端子ウェイトモード1は、4ステート以上の場合や、外部デバイスごとに挿入する  $T_w$  数を変える場合などに有効です。

ウェイトカウントが “0” の場合は、端子ウェイトモード0と同様の動作になります。

ウェイトカウントが 1 ( $W C 1 = “0”$ 、 $W C 0 = “1”$ ) で、かつ WAIT 端子入力による  $T_w$  が 1 ステートの場合のタイミングを図 6.13 に示します。

【注】\* 矢印は WAIT 端子のサンプリングタイミングを示します。

図 6.13 端子ウェイトモード1

(b) 端子オートウェイトモード

端子オートウェイトモードでは、WAIT端子が“Low”レベルのとき、WC1、0ビットで設定されたT<sub>w</sub>数が挿入されます。

端子オートウェイトモードでは、T<sub>2</sub>ステートの中の立下がりのタイミングでWAIT端子が“Low”レベルであればWC1、0ビットによって設定された数だけT<sub>w</sub>を挿入します。

WAIT端子を“Low”レベルに保持しても、設定された数を超えるT<sub>w</sub>は挿入されません。端子オートウェイトモードを用いるとチップセレクト信号をWAIT端子に入力するだけで、低速メモリと容易にインターフェースすることができます。

このタイミングを図6.14に示します。図6.14は、ウェイトカウントが1の場合です。

【注】\* 矢印はWAIT端子のサンプリングタイミングを示します。

図6.14 端子オートウェイトモード

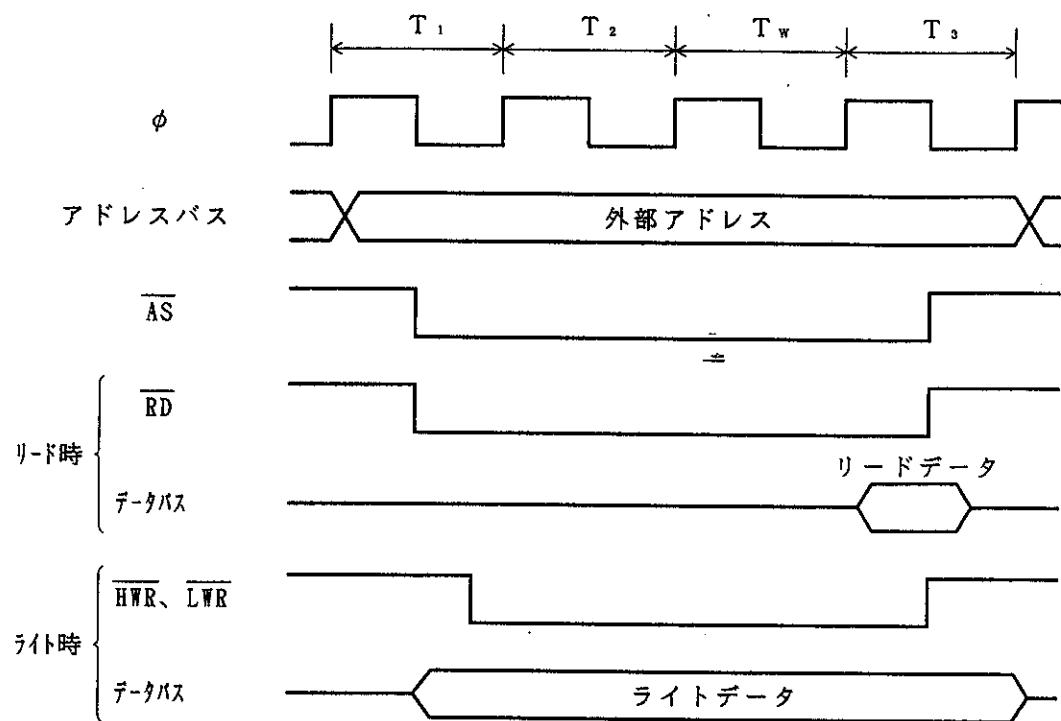

(c) プログラマブルウェイトモード

プログラマブルウェイトモードでは、外部 3 ステートアクセス空間をアクセスすると、常に WC1、0 ビットにより設定されたステート数だけ  $T_w$  が挿入されます。

このタイミングを図 6.15 に示します。図 6.15 は、ウェイトカウントが 1 の場合 (WC1 = "0"、WC0 = "1") です。

図 6.15 プログラマブルウェイトモード

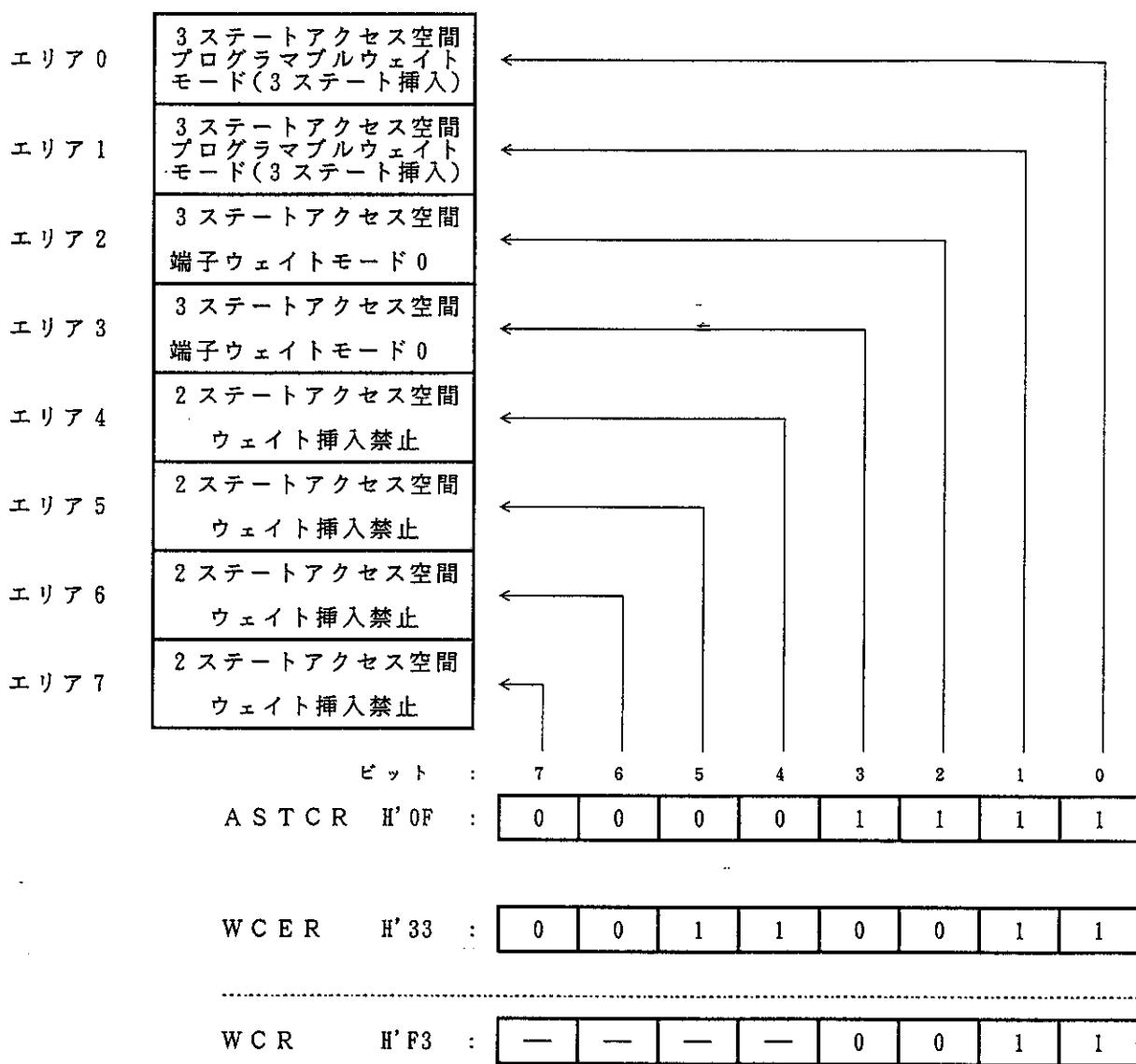

### (3) W S C の設定例

リセット後のW C E R、A S T C Rは、いずれもH'FF、W C RはH'F3となっています。このため全エリアともプログラマブルウェイトモードの3ステート挿入となります。

その後、ソフトウェアにより、A S T C R、W C E R、W C Rを設定し、エリアごとのウェイトモードを選択してください。

ウェイトモードの設定例を図6.16に示します。

【注】 A S T C R によって 2 ステートアクセスに設定されたエリアでは、ウェイトステートは挿入できません。

図6.16 ウェイトモードの設定例

### 6.3.6 メモリとの接続例

バスコントローラは、各エリアごとに、データバス幅を8ビットアクセス空間または16ビット空間に、またアクセスステート数を2ステートアクセス空間または3ステートアクセス空間のいずれかに設定することができます。3ステートアクセス空間に対しては多種のウェイト挿入が可能ですので高速性が要求されるデバイスと低速デバイスを容易に接続することが可能です。

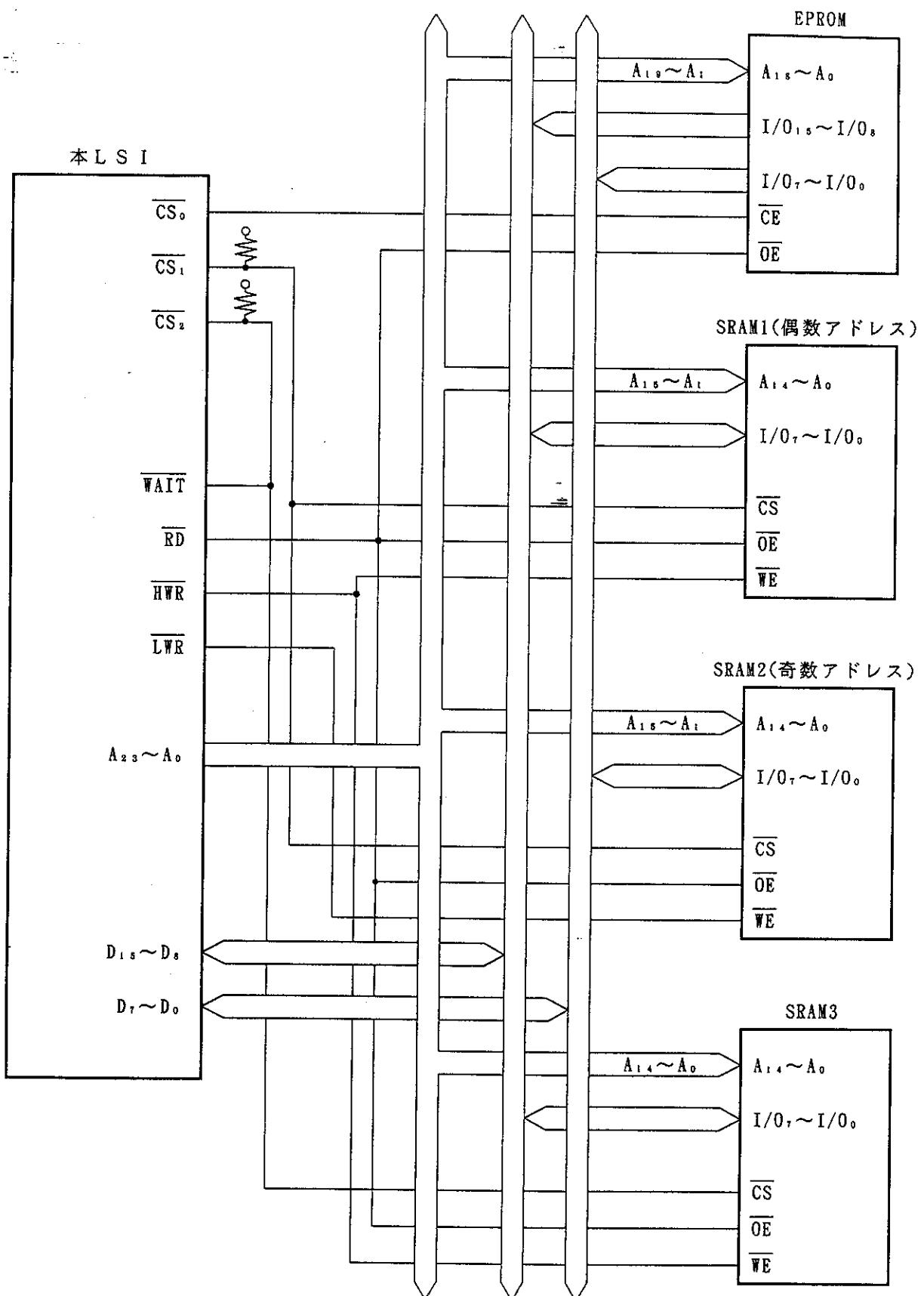

本LSIとメモリとの接続例を図6.18に、また、このときのメモリマップを図6.17に示します。

エリア0に256kワード×16ビットのEEPROMを接続し、16ビット3ステートアクセスを行います。

エリア1に32kワード×8ビットのSRAMを2個(SRAM1、2)接続し、16ビット2ステートアクセスを行います。

エリア2に32kワード×8ビットのSRAMを(SRAM3)を1個接続し、8ビット3ステートアクセス・端子オートウェイトステートを行います。

図6.17 メモリマップ例

図 6.18 メモリとの接続例

### 6.3.7 バスアービタの動作

バスコントローラは、バスマスターの動作を調停（バスアービトレーション）するバスアービタを内蔵しています。

バスマスターは、C P U、D M A C、リフレッシュコントローラ、外部バスマスターの4つがあり、バス権を占有した状態でリード／ライトやリフレッシュ動作を行います。各バスマスターはバス権要求信号によりバス権を要求します。バスアービタは所定のタイミングで優先順位を判定し、バス権要求アクノリッジ信号によりバスの使用を許可して、バスマスターはバス権を獲得して動作します。

バスアービタは、バスマスターのバス権要求信号がアクティブになっているかどうかを調べ、アクティブになっていれば、そのバスマスターにバス権要求アクノリッジ信号を返します。複数のバスマスターからバス権要求があれば、最も優先順位の高いものにバス権要求アクノリッジを返します。バス権要求アクノリッジ信号を受け取ったバスマスターは、以後この信号が取り消されるまでバスを使用します。

バスマスターの優先順位は、

（高） 外部バスマスター > リフレッシュコントローラ > D M A C > C P U （低）

の順となっています。バスアービタは常にバス権要求信号をサンプリングし、優先順位を判定していますが、現在のバスマスターよりも優先順位の高いバスマスターからバス権要求があったとしても、すぐにバス権を放棄するとは限りません。

各バスマスターには、それぞれ自分より優先順位の高いバスマスターにバス権を譲ることができるタイミングがあります。

#### ① C P U

C P Uは最も優先順位の低いバスマスターです。C P Uがバスマスターの場合にD M A C、リフレッシュコントローラ、または外部バスマスターからのバス権要求が発生するとバスアービタはバス権を要求があったバスマスターに移行します。バス権が移行するタイミングは次のとおりです。

- ① バスサイクルの切れ目でバス権を移行します。ワードデータアクセスを2回のバイトアクセスに分割して行う場合には、これら2つのバイトアクセスの間ではバス権は移行しません

- ② C P Uが乗除算命令などの内部動作を行っている場合、他のバスマスターからバス権要求が発生するとただちに、バス権が移行します。C P Uの内部動作は継続されます。

- ③ C P Uがスリープモードの場合、他のバスマスターからバス権要求が発生するとただちにバス権が移行します。

## (2) D M A C

D M A C は、起動要求が発生するとバスアービタに対してバス権を要求します。

D M A C がバスマスターの場合にリフレッシュコントローラ、または外部バスマスターからのバス権要求が発生すると、バスアービタはバス権の要求があったバスマスターに移行します。バス権が移行するタイミングは次のとおりです。

D M A C の 1 バイトまたは 1 ワードの転送が終了したとき、バス権を移行します。D M A C の転送サイクルはリードサイクルとライトサイクルで構成され、これらのリードサイクルと次のライトサイクルの間ではバス権は移行しません。

なお、D M A C の各チャネルには優先順位が設けられています。詳細については、「8.4.9 D M A C 複数チャネルの動作」を参照してください。

## (3) リフレッシュコントローラ

リフレッシュコントローラは、リフレッシュサイクル要求が発生するとバスマスターに対してバス権を要求します。リフレッシュサイクルが終了すると、バス権を放棄します。詳細は、「第 7 章 リフレッシュコントローラ」を参照してください。

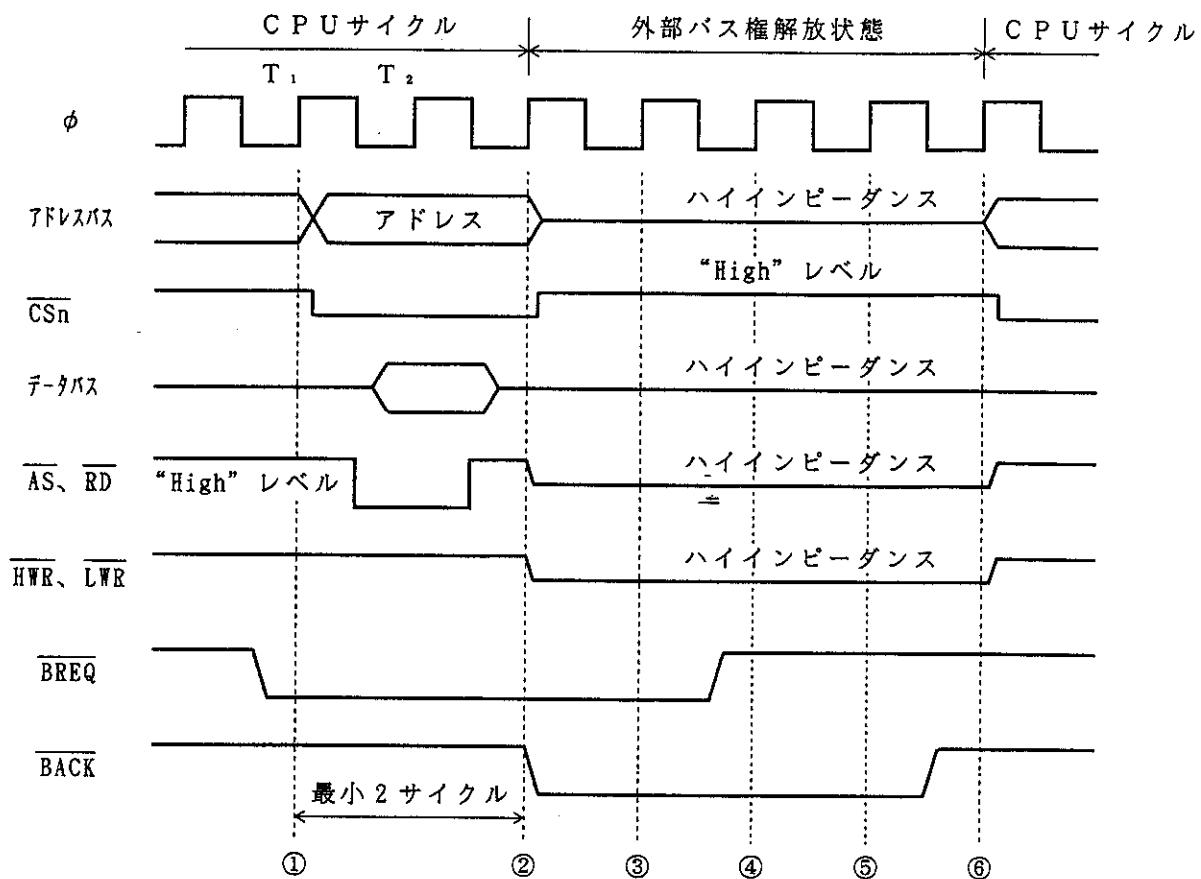

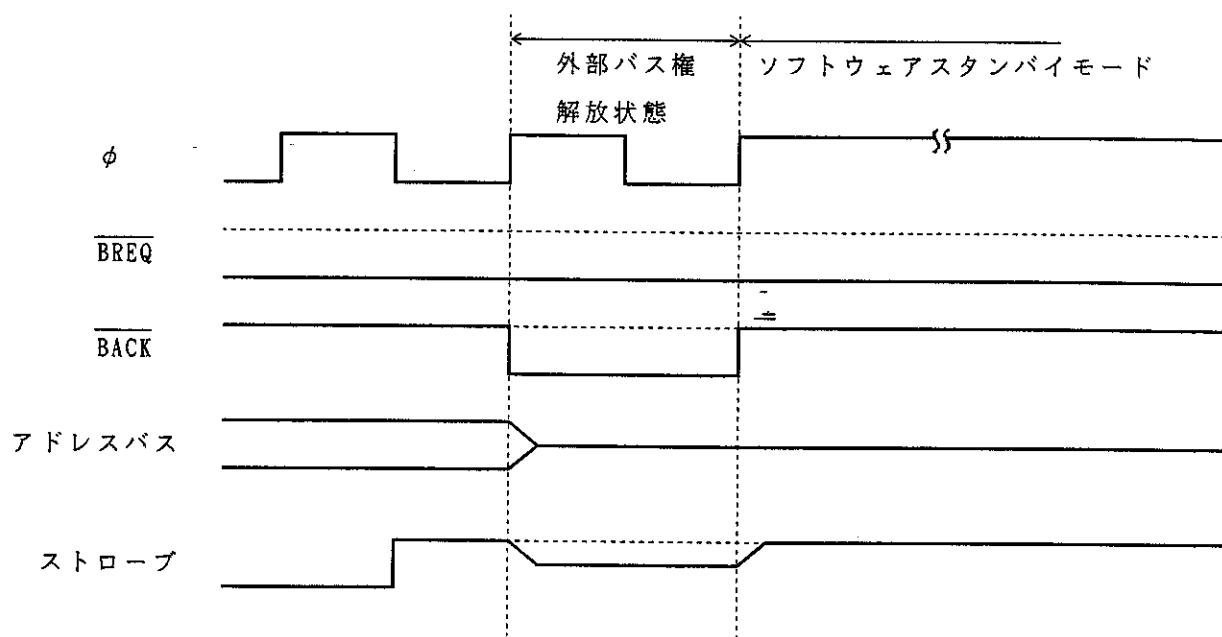

## (4) 外部バスマスター

B R C R の B R L E ビットを “1” にセットすると外部バスマスターにバス権を解放することができます。外部バスマスターは最も優先順位の高いバスマスターであり、BREQ端子を “Low” レベルにすることにより、バスアービタに対してバス権を要求します。外部バスマスターが一旦バス権を獲得するとBREQを “Low” レベルにしている間、バス権を保持し続けます。本 L S I は、外部バス権解放状態になると、アドレスバス、データバス、バス制御信号 (AS, RD, HWR, LWR) がハイインピーダンスとなり、チップセレクト信号 (C S n : n = 7 ~ 0) は “High” レベルとなります。また外部バス権解放状態では、BACK端子が “Low” レベル出力となります。

バスアービタは、ゆの立上がりでBREQ端子をサンプリングします。BREQ端子の “Low” レベルをサンプルすると所定のタイミングで外部バス権解放状態となります。BACK端子が “Low” レベルになるまでBREQ端子を “Low” レベルに保持してください。

外部バス権解放で、BREQ端子の “High” レベルを 2 回連続してサンプリングすると、BACK端子を “High” レベルにしてバス権解放サイクルを終了します。

図 6.19 に 2 ステートアクセス空間のリードサイクル中に外部バスマスターからバス権を要求された場合の動作タイミングを示します。BREQ 端子を “Low” レベルとしてから外部バス権解放状態となるまで最小 2 サイクルかかります。

$n = 7 \sim 0$

- ①  $T_1$  ステートの立上がりで BREQ 端子の “Low” レベルをサンプリングします。

- ② CPU リードサイクルの終了時点で BACK 端子を “Low” レベルにしてバス権を外部バスマスターに解放します。

- ③ 外部バス権解放状態でも BREQ 端子の状態をサンプリングします。

- ④ ⑤ BREQ 端子の “High” レベルを 2 回連続してサンプリングします。

- ⑥ BACK 端子を “High” レベルにして、バス権解放サイクルを終了します。

図 6.19 外部バス権解放状態 (2 ステートアクセス空間リードサイクル中)

## 6.4 使用上の注意

### 6.4.1 DRAMおよびPSRAMの接続

エリア3にDRAMまたはPSRAMを直接接続する場合、バス制御信号タイミングが異なります。詳細は「第7章 リフレッシュコントローラ」を参照してください。

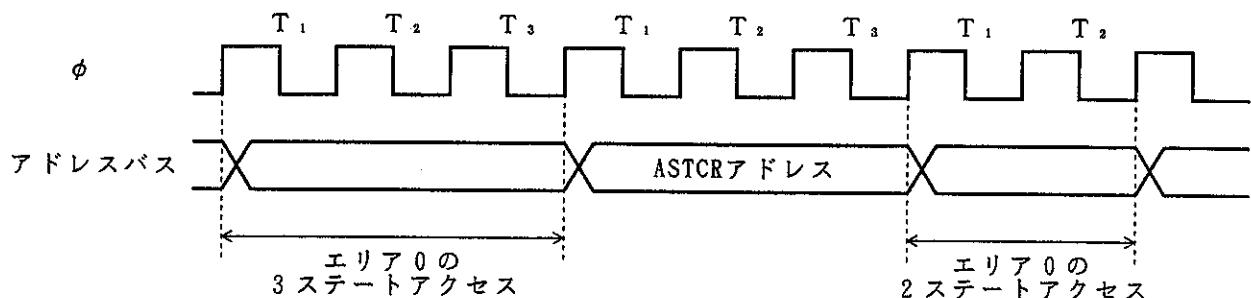

### 6.4.2 レジスタライトタイミング

#### (1) ABWCR、ASTCRおよびWCERのライトタイミング

ABWCR、ASTCRおよびWCERをライトした場合、ライトデータは次のバスサイクルから有効になります。

このタイミングを図6.20に示します。

エリア0上の命令でエリア0を3ステートアクセス空間から2ステートアクセス空間へ変更した場合の例です。

図6.20 ASTCRライトタイミング

#### (2) DDRライトタイミング

$CS_0$ 端子に対応するポートのDDRをライトし、 $CS_0$ 出力と入力ポートを切り換える場合、ライトデータはDDRライトサイクルの $T_3$ から有効になります。このタイミングを図6.21に示します。 $CS_1$ 端子を出力とする場合の例です。

図6.21 DDRライトタイミング

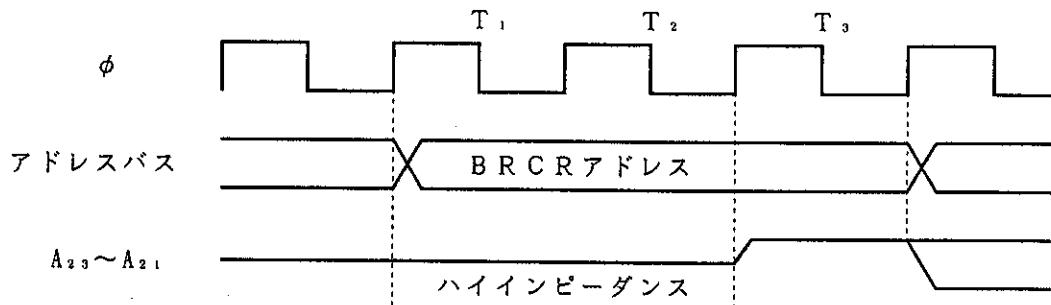

### (3) B R C R ライトタイミング

B R C R にライトし、 $A_{23} \sim A_{21}$  出力と入出力ポートを切り換える場合、ライトデータは B R C R ライトサイクルの  $T_3$  から有効になります。このタイミングを図 6.22 に示します。

入力ポートを  $A_{23} \sim A_{21}$  出力とする場合の例です。

図 6.22 B R C R ライトタイミング

### 6.4.3 BREQ 端子の入力タイミング

BREQ 端子を "Low" レベルにした後、BACK 端子が "Low" レベルになるまで "Low" レベルを保持してください。BACK 端子が "Low" レベルになる前に BREQ 端子を "High" レベルに戻すと、バスアービタの動作が不確定となりますので注意してください。

また、外部バス権解放状態を終了するときには BREQ 端子を 3 ステート以上 "High" レベルにしてください。BREQ 端子の "High" レベルの期間が短いとバスアービタの動作が不確定となりますので注意してください。

#### 6.4.4 ソフトウェアスタンバイモードへの遷移

ソフトウェアスタンバイモードへ遷移するとき、外部バスマスターからのバス権要求が競合すると、ソフトウェアスタンバイモードへの遷移の直前に「ステートバス解放状態」が発生することがあります（図 6.23 参照）。

ソフトウェアスタンバイモードを使用するときは、SLEEP 命令を実行する前に、BRCCR の BRL\_E ビットを“0”にクリアしてください。

図 6.23 バス解放状態とソフトウェアスタンバイモードの競合