# 7. リフレッシュコントローラ

## 第7章 目次

|       |                                   |     |

|-------|-----------------------------------|-----|

| 7.1   | 概要                                | 173 |

| 7.1.1 | 特長                                | 173 |

| 7.1.2 | ブロック図                             | 174 |

| 7.1.3 | 端子構成                              | 175 |

| 7.1.4 | レジスタ構成                            | 175 |

| 7.2   | 各レジスタの説明                          | 176 |

| 7.2.1 | リフレッシュコントロールレジスタ (RFSHCR)         | 176 |

| 7.2.2 | リフレッシュタイマコントロールステータスレジスタ (RTMCSR) | 179 |

| 7.2.3 | リフレッシュタイマカウンタ (RTCNT)             | 182 |

| 7.2.4 | リフレッシュタイムコンスタントレジスタ (RTCOR)       | 182 |

| 7.3   | 動作説明                              | 183 |

| 7.3.1 | 概要                                | 183 |

| 7.3.2 | DRAMリフレッシュ制御                      | 185 |

| 7.3.3 | PSRAMリフレッシュ制御                     | 200 |

| 7.3.4 | インターバルタイマ                         | 203 |

| 7.4   | 割込み要因                             | 208 |

| 7.5   | 使用上の注意                            | 209 |

## 7.1 概要

H8/3048シリーズは、リフレッシュコントローラを内蔵しており、 $\times 16$ ビット構成のDRAMを直接接続できます。また、DRAMの代りにPSRAMを直接接続することも可能です。

DRAMまたはPSRAMを直接接続できる外部アドレス空間はエリア3です。モード1、2、5（1Mバイトモード）は最大128kバイト、モード3、4、6（16Mバイトモード）は最大2Mバイトを使用できます。

DRAM、PSRAMのリフレッシュが不要なシステムでは、8ビットインターバルタイマとして使用できます。

消費電流低減のため、リフレッシュコントローラを使用しない場合には、リフレッシュコントローラを単独に停止することができます。詳細は「20.6 モジュールスタンバイ機能」を参照してください。

### 7.1.1 特長

リフレッシュコントローラは、DRAMリフレッシュ制御、PSRAMリフレッシュ制御、またはインターバルタイマのうち、いずれか一つの機能を使用できます。リフレッシュコントローラの特長を以下に示します。

#### (1) DRAMリフレッシュコントローラとしての特長

- $\times 16$ ビット構成のDRAMを直接接続可能

- 2CAS方式、または2WE方式のいずれか一方を選択可能

- DRAMのアドレス入力のマルチプレクスは、8ビットカラムアドレスまたは9ビットカラムアドレスのいずれか一つを選択可能

（例）

- 1MビットDRAM 8ビットロウアドレス $\times$ 8ビットカラムアドレス

- 4MビットDRAM 9ビットロウアドレス $\times$ 9ビットカラムアドレス

- 4MビットDRAM 10ビットロウアドレス $\times$ 8ビットカラムアドレス

- リフレッシュ制御はCASビフォRASリフレッシュを採用

- プログラムによりリフレッシュ間隔を選択可能

- プログラムによりセルフリフレッシュモードを設定可能

- ウェイットステート挿入可能

#### (2) PSRAMリフレッシュコントローラとしての特長

- リフレッシュ制御のためRFSH信号を出力

- プログラムによりリフレッシュ間隔を選択可能

- プログラムによりセルフリフレッシュモードを設定可能

- ウェイットステート挿入可能

### (3) インターパルタイマとしての特長

- リフレッシュタイマカウンタ (RTCNT) を 8 ビットアップカウンタとして使用可能

- カウントクロックは 7 種類 ( $\phi/2$ 、 $\phi/8$ 、 $\phi/32$ 、 $\phi/128$ 、 $\phi/512$ 、 $\phi/2048$ 、 $\phi/4096$ ) から選択可能

- RTCNT とリフレッシュタイムコンスタントレジスタ (RCTOR) のコンペアマッチにより割込み発生可能

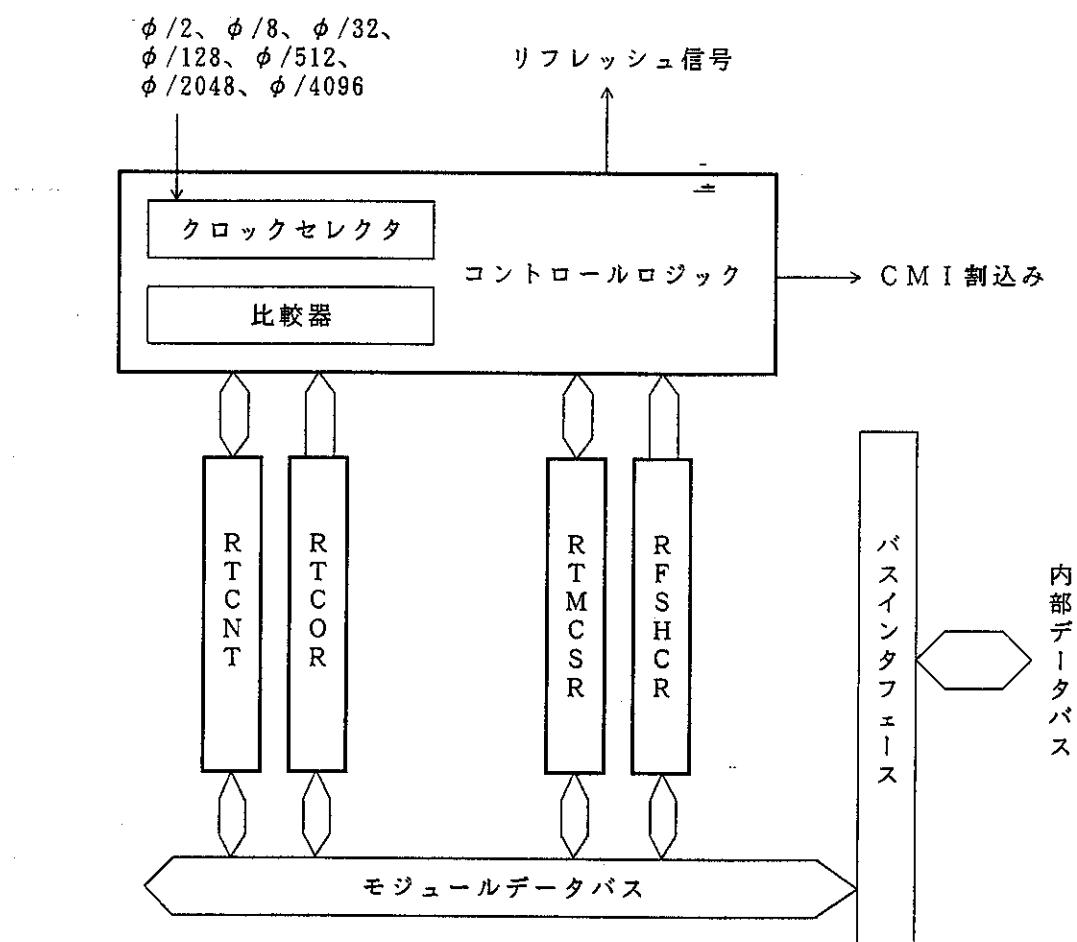

#### 7.1.2 ブロック図

リフレッシュコントローラのブロック図を図 7.1 に示します。

#### 《記号説明》

- RTCNT : リフレッシュタイマカウンタ

- RCTOR : リフレッシュタイムコンスタントレジスタ

- RTMCSR : リフレッシュタイマコントロール／ステータスレジスタ

- RFSHCR : リフレッシュコントロールレジスタ

図 7.1 リフレッシュコントローラのブロック図

### 7.1.3 端子構成

リフレッシュコントローラの端子構成を表7.1に示します。

表7.1 端子構成

| 端子                    | 信号                       |                | 入出力 | 機能                                                                                        |

|-----------------------|--------------------------|----------------|-----|-------------------------------------------------------------------------------------------|

|                       | 名称                       | 略称             |     |                                                                                           |

| <u>RFSH</u>           | リフレッシュ                   | <u>RFSH</u>    | 出力  | リフレッシュサイクル時“Low”レベルとなります。<br>D R A M および P S R A M のリフレッシュに使用します。                         |

| <u>HWR</u>            | アッパーライト／アッパーカラムアドレスストローブ | <u>UW/UCAS</u> | 出力  | 2 <u>WE</u> 方式 D R A M の <u>UW</u> 端子／<br>2 <u>CAS</u> 方式 D R A M の <u>UCAS</u> 端子と接続します。 |

| <u>LWR</u>            | ロウアーライト／ロウアーカラムアドレスストローブ | <u>LW/LCAS</u> | 出力  | 2 <u>WE</u> 方式 D R A M の <u>LW</u> 端子／<br>2 <u>CAS</u> 方式 D R A M の <u>LCAS</u> 端子と接続します。 |

| <u>RD</u>             | カラムアドレスストローブ／ライトイネーブル    | <u>CAS/WE</u>  | 出力  | 2 <u>WE</u> 方式 D R A M の <u>CAS</u> 端子／<br>2 <u>CAS</u> 方式 D R A M の <u>WE</u> 端子と接続します。  |

| <u>CS<sub>3</sub></u> | ロウアドレスストローブ              | <u>RAS</u>     | 出力  | D R A M の <u>RAS</u> 端子と接続します。                                                            |

### 7.1.4 レジスタ構成

リフレッシュコントローラのレジスタ構成を表7.2に示します。

表7.2 レジスタ構成

| アドレス*  | 名 称                       | 略 称         | R/W | 初期値  |

|--------|---------------------------|-------------|-----|------|

| H'FFAC | リフレッシュコントロールレジスタ          | R F S H C R | R/W | H'02 |

| H'FFAD | リフレッシュタイマコントロール／ステータスレジスタ | R T M C S R | R/W | H'07 |

| H'FFAE | リフレッシュタイマカウンタ             | R T C N T   | R/W | H'00 |

| H'FFAF | リフレッシュタイムコンスタントレジスタ       | R T C O R   | R/W | H'FF |

【注】\* アドレスの下位16ビットを示しています。

## 7.2 各レジスタの説明

#### 7.2.1 リフレッシュコントロールレジスタ (RFSHCR)

RFSHCRは、8ビットのリード／ライト可能なレジスタで、リフレッシュコントローラの動作モードを選択します。

RFSHCRは、リセット、またはハードウェアスンタバイモード時にH'02にイニシャライズされます。

### ビット7：セルフリフレッシュモード（SRFMD）

ソフトウェアスタンバイモード時、DRAMまたはPSRAMのセルフリフレッシュを指定します。

PSRAME = “1”、DRAME = “0”的とき、SRFMDビットを“1”にセットした後に、ソフトウェアスタンバイモードに遷移すると、PSRAMのセルフリフレッシュが可能となります。

また、PSRAME = “0”、DRAME = “1”的とき、SRFMDビットを“1”にセットした後に、ソフトウェアスタンバイモードに遷移すると、DRAMのセルフリフレッシュが可能となります。

いずれの場合もソフトウェアスタンバイモードの解除により、通常のアクセス状態に戻ります。

| ビット7<br>SRFMD | 説明                                                  |

|---------------|-----------------------------------------------------|

| 0             | ソフトウェアスタンバイモード時に、DRAMまたはPSRAMのセルフリフレッシュを禁止<br>(初期値) |

| 1             | ソフトウェアスタンバイモード時に、DRAMまたはPSRAMのセルフリフレッシュが可能          |

### ビット6：PSRAMイネーブル（PSRAME）

### ビット5：DRAMイネーブル（DRAME）

外部アドレス空間のエリア3に対して、DRAMまたはPSRAMの接続を許可／禁止をします。

DRAMまたはPSRAMを接続する場合、エリア3のバスサイクルおよびリフレッシュサイクルはASTCRの設定にかかわらず、3ステートアクセスとなります。ただし、ウェイトステートは、ASTCRのAST3 = “0”的場合、挿入することはできません。

PSRAMEビットまたはDRAMEビットが“1”にセットされていると、RFSHCRのビット0、2、3、4、およびRTMCSR、RTCNT、RTCORへのライトはできません。ただし、RTMCSRのCMFフラグについては、フラグをクリアするための“0”ライトのみ可能です。

| ビット6<br>PSRAME | ビット5<br>DRAME | 説明                                       |

|----------------|---------------|------------------------------------------|

| 0              | 0             | インターバルタイマとして使用可能<br>(DRAM、PSRAMの直接接続不可能) |

|                | 1             | DRAMの直接接続が可能                             |

| 1              | 0             | PSRAMの直接接続が可能                            |

|                | 1             | 使用禁止                                     |

#### ビット4：ストローブモードセレクト (C A S / W E)

2 C A S 方式か2 W E 方式のいずれかを選択します。

本ビットの設定はP S R A M E = “0”、D R A M E = “1”的とき有効となります。本ビットは、P S R A M E ビットまたはD R A M E ビットが“1”にセットされているとライトすることはできません。

| ビット4        | 説明                |

|-------------|-------------------|

| C A S / W E |                   |

| 0           | 2 W E 方式を選択 (初期値) |

| 1           | 2 C A S 方式を選択     |

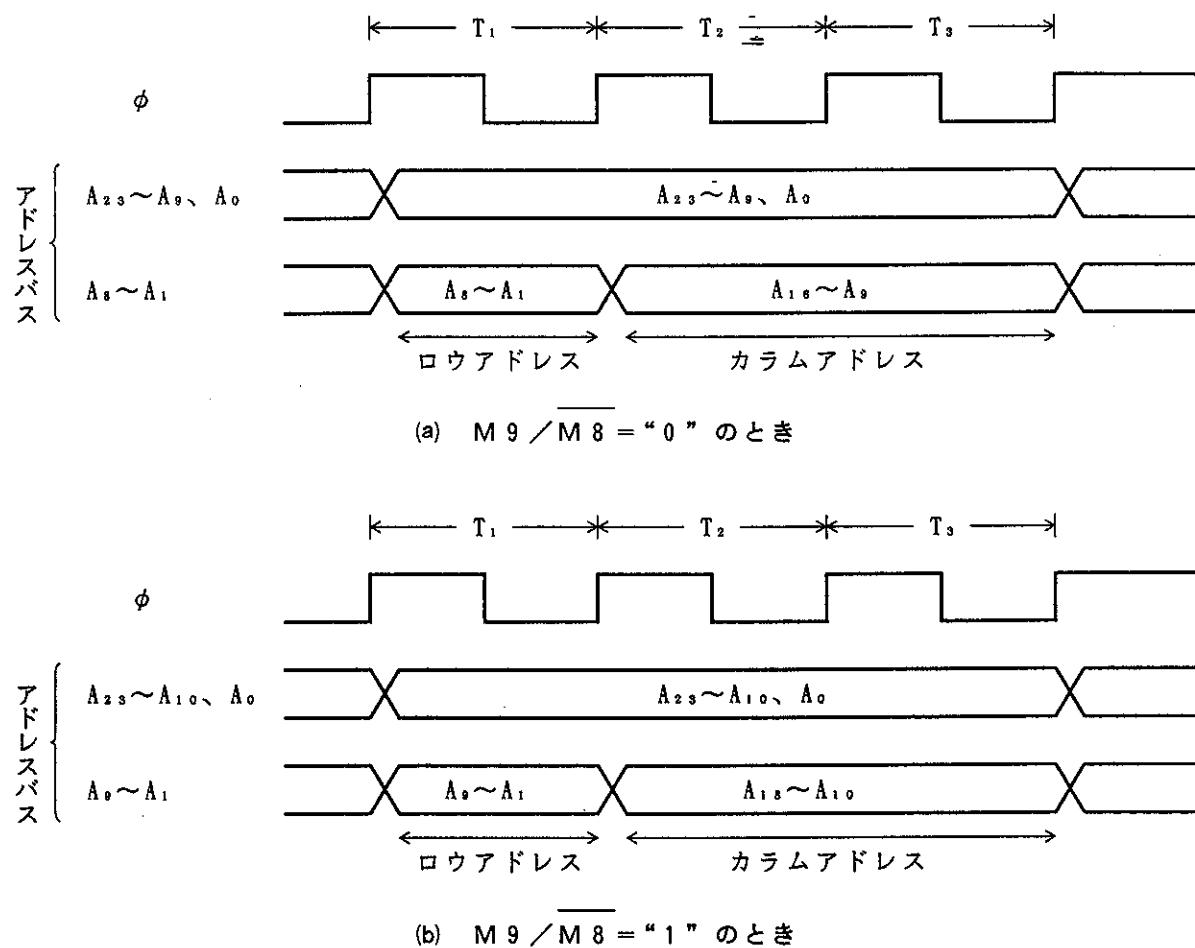

#### ビット3：アドレスマルチプレクスモードセレクト (M 9 / M 8)

8ビットカラムアドレスまたは9ビットカラムアドレスのいずれかを選択します。

本ビットの設定はP S R A M E = “0”、D R A M E = “1”的とき有効となります。本ビットは、P S R A M E ビットまたはD R A M E ビットが“1”にセットされているとライトすることはできません。

| ビット3      | 説明                  |

|-----------|---------------------|

| M 9 / M 8 |                     |

| 0         | 8ビットカラムモードを選択 (初期値) |

| 1         | 9ビットカラムモードを選択       |

#### ビット2：リフレッシュ端子イネーブル (R F S H E)

R F S H 端子のリフレッシュ信号出力を許可／禁止します。

本ビットは、P S R A M E ビットまたはD R A M E ビットが“1”にセットされているとライトすることはできません。

| ビット2      | 説明                                                          |

|-----------|-------------------------------------------------------------|

| R F S H E |                                                             |

| 0         | R F S H 端子のリフレッシュ信号出力を禁止 (初期値)<br>(R F S H 端子は入出力ポートとして使用可) |

| 1         | R F S H 端子のリフレッシュ信号出力を許可                                    |

#### ビット1：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

### ビット0：リフレッシュサイクルイネーブル（R C Y C E）

リフレッシュサイクルの挿入を許可または禁止します。本ビットはP S R A M E = “1”、またはD R A M E = “1”的ときに有効となります。P S R A M E = “0”かつD R A M E ビット = “0”的ときは、本ビットの設定にかかわらずリフレッシュサイクルは挿入されません。

| ビット0      | 説明                    |       |

|-----------|-----------------------|-------|

| R C Y C E |                       |       |

| 0         | リフレッシュサイクルを禁止         | (初期値) |

| 1         | エリア3に対するリフレッシュサイクルを許可 |       |

### 7.2.2 リフレッシュタイマコントロールステータスレジスタ（R T M C S R）

R T M C S Rは、8ビットのリード／ライト可能なレジスタで、R T C N Tに入力するクロックの選択を行います。また、インターバルタイマとして使用する場合は、割込み要求の許可／禁止も行います。

| ビット： | 7      | 6    | 5    | 4    | 3    | 2 | 1 | 0 |

|------|--------|------|------|------|------|---|---|---|

|      | CMF    | CMIE | CKS2 | CKS1 | CKS0 | — | — | — |

| 初期値： | 0      | 0    | 0    | 0    | 0    | 1 | 1 | 1 |

| R/W: | R/(W)* | R/W  | R/W  | R/W  | R/W  | — | — | — |

|      |        |      |      |      |      |   |   |   |

リザーブビット

クロックセレクト2～0

RTCNTに入力するクロックを

内部クロックから選択するビットです。

コンペアマッチインタラプトイネーブル

CMFフラグによる割込み(CM1)要求を

許可／禁止するビットです。

コンペアマッチフラグ

RTCNTとRTCORの値が一致した

ことを示すステータスフラグです。

【注】\* フラグをクリアするための“0”ライトのみ可能です。

ビット7、6は、リセット、またはスタンバイモード時にイニシャライズされます。

ビット5～3は、リセット、またはハードウェアスタンバイモード時にイニシャライズされますが、ソフトウェアスタンバイモード時にはソフトウェアスタンバイモードに遷移する前の状態を保持しています。

#### ビット7：コンペアマッチフラグ (CMF)

R T C N TとR T C O Rの値が一致したことを示すステータスフラグです。

| ビット7  | 説明                                                                |

|-------|-------------------------------------------------------------------|

| C M F |                                                                   |

| 0     | [クリア条件]<br>C M F = “1”の状態で、C M F フラグをリードした後、C M F フラグに“0”をライトしたとき |

| 1     | [セット条件]<br>R T C N T = R T C O R になったとき                           |

#### ビット6：コンペアマッチインタラプトイネーブル (C M I E)

R T C S RのC M F フラグが“1”にセットされたとき、C M F フラグによる割込み (C M I) 要求を許可／禁止します。

P S R A M E = “1”、またはD R A M E = “1”的とき、C M I E ビットは常に“0”にクリアされています。

| ビット6    | 説明                                     |

|---------|----------------------------------------|

| C M I E |                                        |

| 0       | C M F フラグによる割込み (C M I) 要求を禁止<br>(初期値) |

| 1       | C M F フラグによる割込み (C M I) 要求を許可          |

### ビット5～3：クロックセレクト2～0（CKS2～CKS0）

RTCNTに入力するクロックを内部クロックから選択します。リフレッシュコントローラとして使用する場合は、RTCNTとRTCCRのコンペアマッチによりリフレッシュ要求を周期的に発生します。インターバルタイマとして使用する場合は、コンペアマッチによりCMI割込み要求を周期的に発生します。

本ビットは、PSRAMEビットまたはDRAMEビットが“1”にセットされているとライトすることはできません。

| ビット5<br>CKS2 | ビット4<br>CKS1 | ビット3<br>CKS0 | 説明                |

|--------------|--------------|--------------|-------------------|

| 0            | 0            | 0            | クロック入力禁止<br>(初期値) |

|              |              | 1            | φ/2でカウント          |

|              | 1            | 0            | φ/8でカウント          |

|              |              | 1            | φ/32でカウント         |

| 1            | 0            | 0            | φ/128でカウント        |

|              |              | 1            | φ/512でカウント        |

|              | 1            | 0            | φ/2048でカウント       |

|              |              | 1            | φ/4096でカウント       |

### ビット2～0：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

### 7.2.3 リフレッシュタイムカウンタ (RTCNT)

RTCNTは、リード／ライト可能な8ビットのアップカウンタです。

| ビット: | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

|      |   |   |   |   |   |   |   |   |

初期値: 0 0 0 0 0 0 0 0 0

R/W: R/W R/W R/W R/W R/W R/W R/W R/W

RTCNTは、RTMCSRのCKS2～CKS0ビットで選択された内部クロックにより、カウントアップします。

RTCNTがRTCORに一致（コンペアマッチ）すると、CMFフラグが“1”にセットされ RTCNTはH'00にイニシャライズされます。

RTCNTは、PSRAMEビットまたはDRAMEビットが“1”にセットされているとライトすることはできません。

RTCNTは、リセット、またはスタンバイモード時にH'00にイニシャライズされます。

### 7.2.4 リフレッシュタイムコンスタントレジスタ (RTCOR)

RTCORは、8ビットのリード／ライト可能なレジスタで、RTCNTとのコンペアマッチ周期を設定します。

| ビット: | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

|      |   |   |   |   |   |   |   |   |

初期値: 1 1 1 1 1 1 1 1

R/W: R/W R/W R/W R/W R/W R/W R/W R/W

RTCORとRTCNTの値は常に比較されており、両方の値が一致するとRTMCSRのCMFフラグが“1”にセットされ、同時にRTCNTがH'00にクリアされます。

RTCORは、PSRAMEビットまたはDRAMEビットが“1”にセットされているとライトすることはできません。

RTCORは、リセット、またはハードウェアスタンバイモード時にH'FFにイニシャライズされます。ソフトウェアスタンバイモード時にはソフトウェアスタンバイモードに遷移する前の値を保持しています。

## 7.3 動作説明

### 7.3.1 概要

リフレッシュコントローラは、エリア3に接続したDRAMのインターフェース、エリア3に接続したPSRAMのインターフェース、またはインターバルタイマのうち、いずれか一つを選択することができます。

上記の3種類の使用方法の概要を表7.3に示します。

表7.3 リフレッシュコントローラの設定方法

| 用途<br>レジスタ設定 |                  | DRAM<br>インターフェース             | PSRAM<br>インターフェース | インターバルタイマ           |

|--------------|------------------|------------------------------|-------------------|---------------------|

| RFSHCR       | S RFMD           | セルフリフレッシュモードの指定              |                   | “0”に設定              |

|              | P SRAME          | “0”に設定                       |                   | “0”に設定              |

|              | D RAME           | “1”に設定                       |                   | “0”に設定              |

|              | C AS / <u>WE</u> | 2CAS方式 /<br><u>WE</u> 方式選択   |                   | _____               |

|              | M 9 / <u>M</u> 8 | カラムモード選択                     |                   | _____               |

|              | R F S H E        | <u>RFSH</u> 端子出力選択           |                   | “0”に設定              |

|              | R C Y C E        | リフレッシュサイクル挿入選択               |                   | _____               |

| RTMCSR       | RTCOR            | リフレッシュ間隔を設定                  |                   | 割込み周期を設定            |

|              | C KS 2 ~ 0       |                              |                   |                     |

|              | CMF              | RTCNT = RTCORのとき、“1”にセット     |                   |                     |

| P8DDR        | CMIE             | “0”に設定                       |                   | 割込み要求の許可 /<br>禁止を選択 |

|              | P 8 DDR          | “1”に設定(CS <sub>3</sub> 出力設定) |                   | “0”または“1”<br>に設定    |

| ABWCR        | ABW3             | “0”に設定                       | _____             |                     |

#### (1) DRAMインターフェース

RTCOR、RTMCSR、RFSHCRの順に初期設定を行い、PSRAMEビットを“0”、D RAMEビットを“1”に設定することにより、×16ビット構成のDRAMをエリア3に接続できます。このとき、ポート8データディレクションレジスタ(P8DDR)のP8DDRビットを“1”にセットしてCS<sub>3</sub>出力に設定してください。また、ABWCRにより、エリア3を16ビットアクセス空間に設定してください。

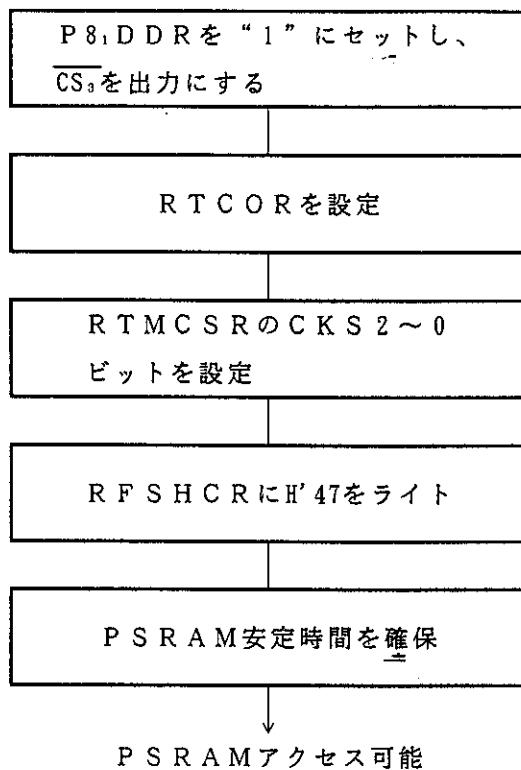

## (2) PSRAMインターフェース

RTCOR、RTMCSR、RFSHCRの順に初期設定を行い、PSRAMEビットを“1”、DRAMEビットを“0”に設定することにより、PSRAMをエリア3に接続できます。このとき、P8DDRのP8DDRビットを“1”にセットしてCS出力に設定してください。

## (3) インターバルタイマ

PSRAME = “0”かつDRAME = “0”的き、インターバルタイマとして動作します。RTCORを設定後、RTMCSRで入力クロックを選択して、CMIEビットを“1”にセットしてください。

上記設定により、RTCORとRTMCSRのCKS2～CKS0ビットで決まるコンペアマッチの周期ごとにCMII割込み要求を発生することができます。

RTCOR、RTMCSR、RFSHCRの設定は、必ずPSRAME = “0”かつDRAME = “0”的状態で行ってください。どちらかのビットが“1”的場合、ライトできません。

—

### 7.3.2 DRAMリフレッシュ制御

#### (1) リフレッシュ要求の周期とリフレッシュサイクルの実行

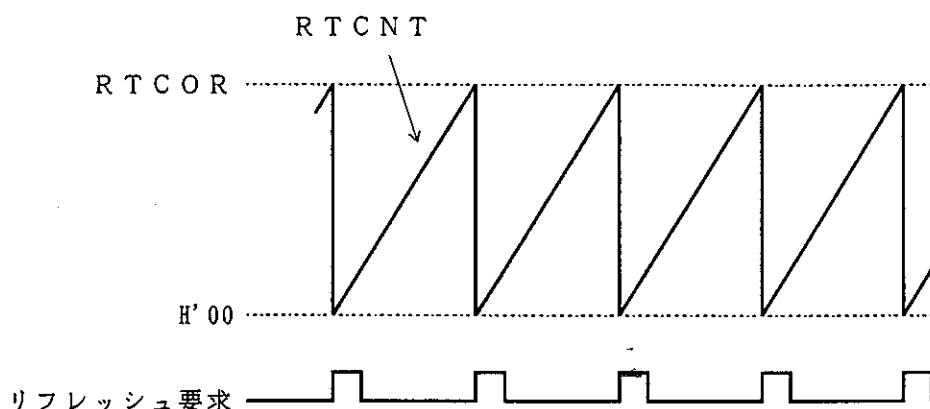

リフレッシュ要求の周期は、RTCORとRTMCSRのCKS2～CKS0ビットにより設定します。

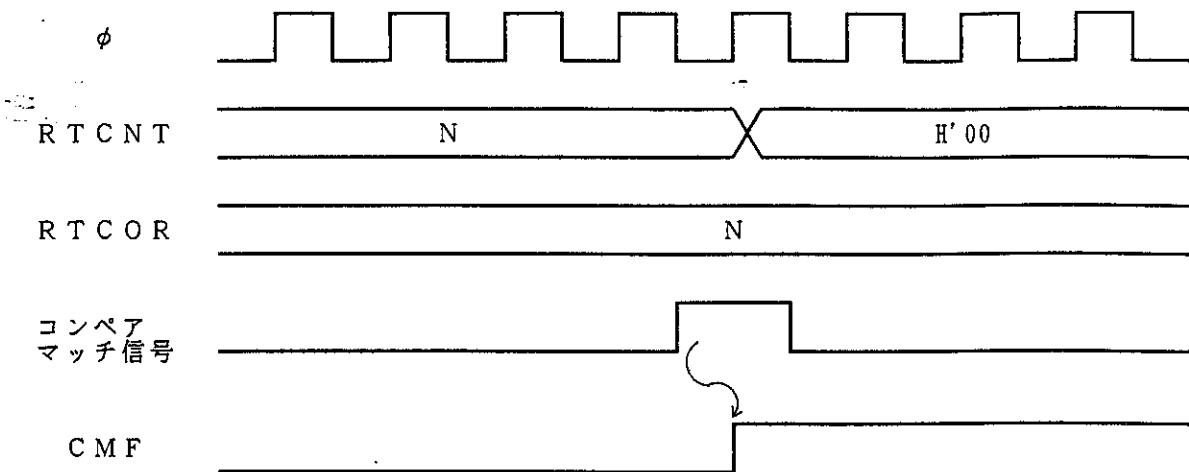

リフレッシュ要求の周期を図7.2に示します。

図7.2 リフレッシュ要求の周期 (RCYCE = “1”)

リフレッシュ要求は図7.2に示す周期で発生しますが、実際のリフレッシュサイクルの実行は、フレッシュコントローラがバス権を獲得した後に行われます。

表7.4にエリア3の設定とDRAMのリード/ライトサイクルおよびリフレッシュサイクルの関係を示します。

表7.4 エリア3の設定とDRAMアクセスサイクルおよびリフレッシュサイクルの関係

| エリア3の設定                     | CPUまたはDMAコントローラによるリード/ライトサイクル | リフレッシュサイクル          |

|-----------------------------|-------------------------------|---------------------|

| 2ステートアクセス空間<br>(AST3 = “0”) | ・3ステート<br>・ウェイト挿入不可           | ・3ステート<br>・ウェイト挿入不可 |

| 3ステートアクセス空間<br>(AST3 = “1”) | ・3ステート<br>・ウェイト挿入可能           | ・3ステート<br>・ウェイト挿入可能 |

リフレッシュサイクルを挿入するために、RFSHCRのRCYCEビットを“1”にセットしてください。

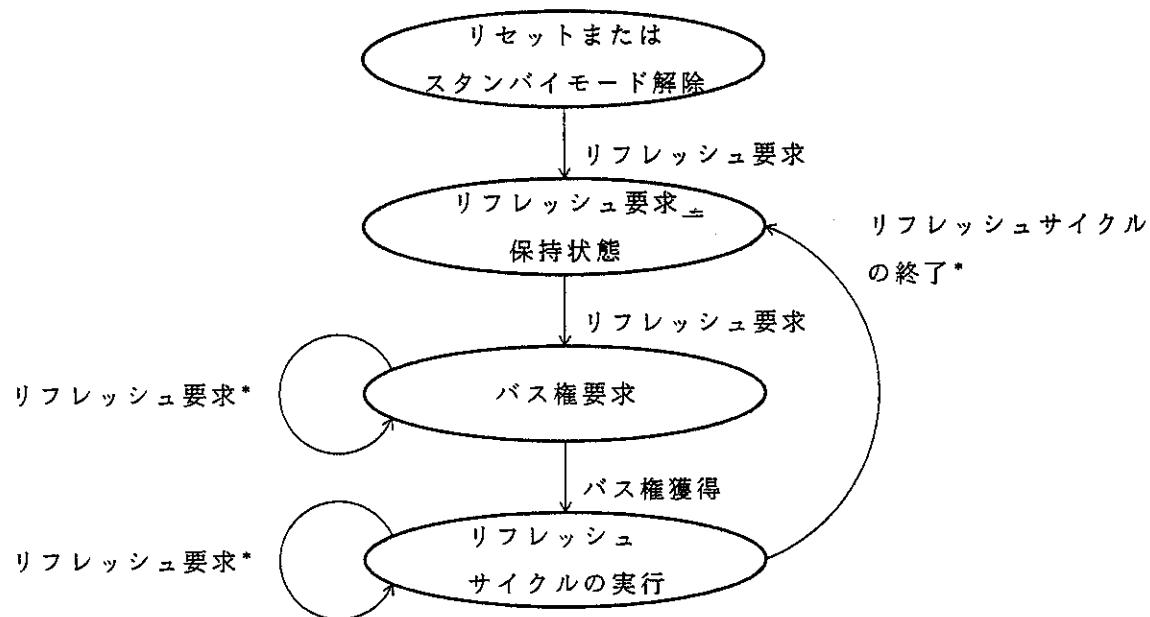

リフレッシュサイクル実行の状態遷移を図7.3に示します。

リセット直後、またはスタンバイモード解除直後にリフレッシュ要求が発生すると、リフレッシュ要求保持状態に遷移します。このときには、リフレッシュサイクルは実行されません。イニシャライズのためにリフレッシュサイクルを必要とするDRAMを使用する場合は注意してください。

リフレッシュ要求保持状態でリフレッシュ要求が発生すると、リフレッシュコントローラはバス権を獲得してリフレッシュサイクルを実行します。また、リフレッシュサイクル実行中に発生したリフレッシュ要求は無視されます。

【注】\* バス権要求中に発生したリフレッシュの再要求、あるいはリフレッシュサイクル実行中のリフレッシュ要求は無視されます。

図7.3 リフレッシュサイクルサイクル実行の状態遷移図

## (2) アドレスマルチプレクス

R F S H C R の M<sub>9</sub> / M<sub>8</sub> ビットにより、カラムアドレスのビット数を指定すると、アドレスのマルチプレクスは表 7.5 に示すようになります。また、そのときのアドレス出力タイミングを図 7.4 に示します。アドレスのマルチプレクス出力は、エリア 3 に対してのみ行われます。

表 7.5 アドレスマルチプレクス

| アドレス端子            | A <sub>23</sub> ～A <sub>10</sub>     | A <sub>9</sub>                   | A <sub>8</sub>  | A <sub>7</sub>  | A <sub>6</sub>  | A <sub>5</sub>  | A <sub>4</sub>  | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  |

|-------------------|--------------------------------------|----------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| ロウアドレス出力時のアドレス出力  | A <sub>23</sub> ～A <sub>10</sub>     | A <sub>9</sub>                   | A <sub>8</sub>  | A <sub>7</sub>  | A <sub>6</sub>  | A <sub>5</sub>  | A <sub>4</sub>  | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  |

| カラムアドレス出力時のアドレス出力 | M <sub>9</sub> /M <sub>8</sub> = "0" | A <sub>23</sub> ～A <sub>10</sub> | A <sub>9</sub>  | A <sub>8</sub>  | A <sub>16</sub> | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> |

|                   | M <sub>9</sub> /M <sub>8</sub> = "1" | A <sub>23</sub> ～A <sub>10</sub> | A <sub>18</sub> | A <sub>17</sub> | A <sub>16</sub> | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> |

図 7.4 マルチプレクスされたアドレス出力の例（ウェイト挿入なし）

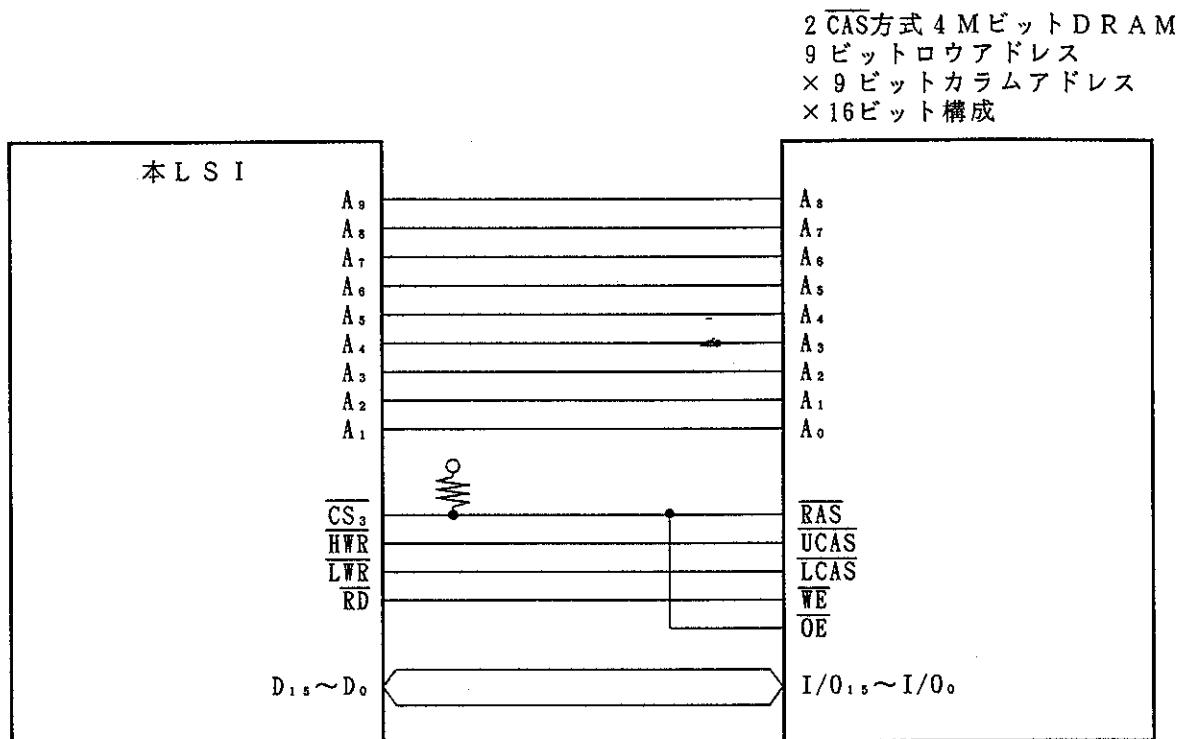

### (3) 2CAS方式と2WE方式

X16ビット構成のDRAMのうち、UCAS、LCASを使用する方式とUW、LWを使用する方式のいずれかをRFSCHRのCAS/WEビットにより、選択することができます。

2 CAS方式および2 WE方式の各々の場合について、DRAMと本LSIの端子対応を表7.6に示します。

表7.6 DRAMと本LSIの端子対応

| 本LSIの端子               | DRAMの端子                         |                                  |

|-----------------------|---------------------------------|----------------------------------|

|                       | CAS/ <u>WE</u> = "0"<br>(2WE方式) | CAS/ <u>WE</u> = "1"<br>(2CAS方式) |

| <u>HWR</u>            | <u>UW</u>                       | <u>UCAS</u>                      |

| <u>LWR</u>            | <u>LW</u>                       | <u>LCAS</u>                      |

| <u>RD</u>             | <u>CAS</u>                      | <u>WE</u>                        |

| <u>CS<sub>3</sub></u> | <u>RAS</u>                      | <u>RAS</u>                       |

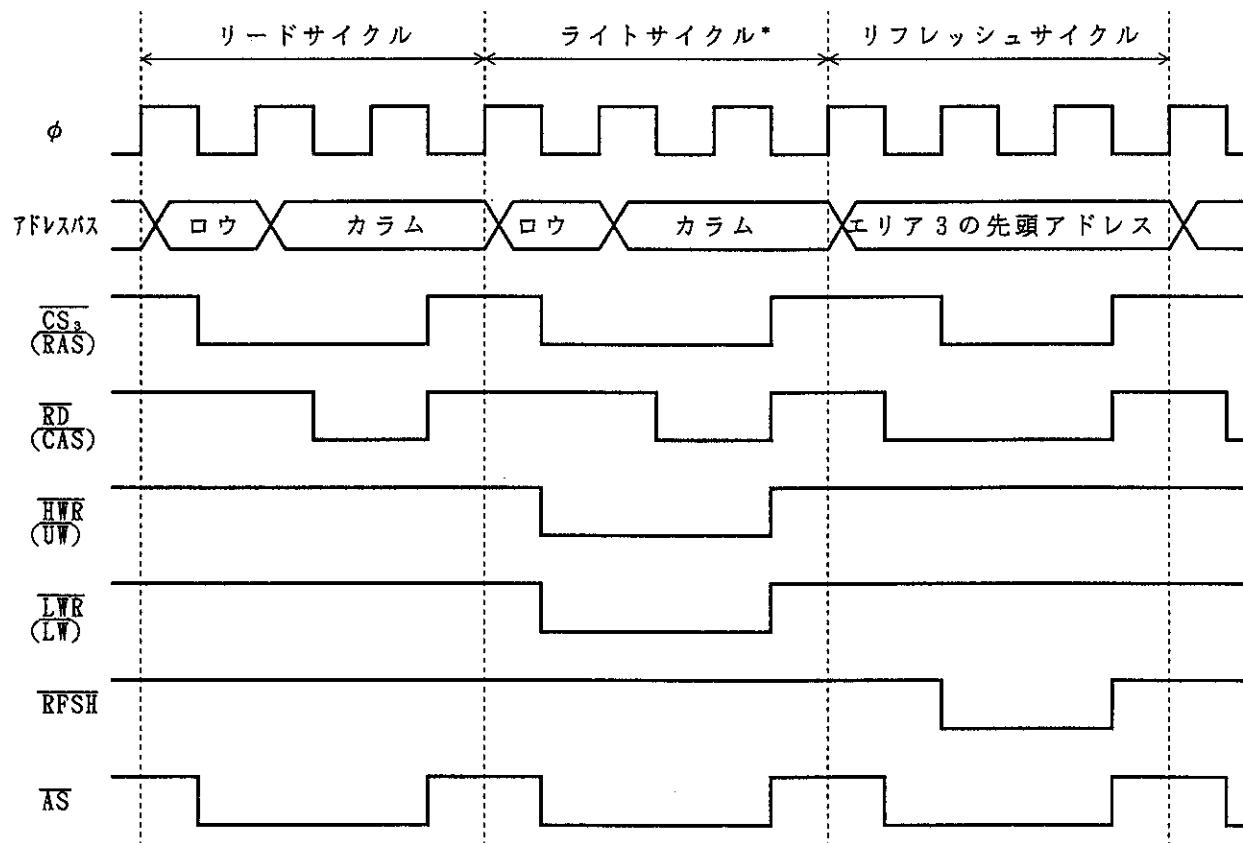

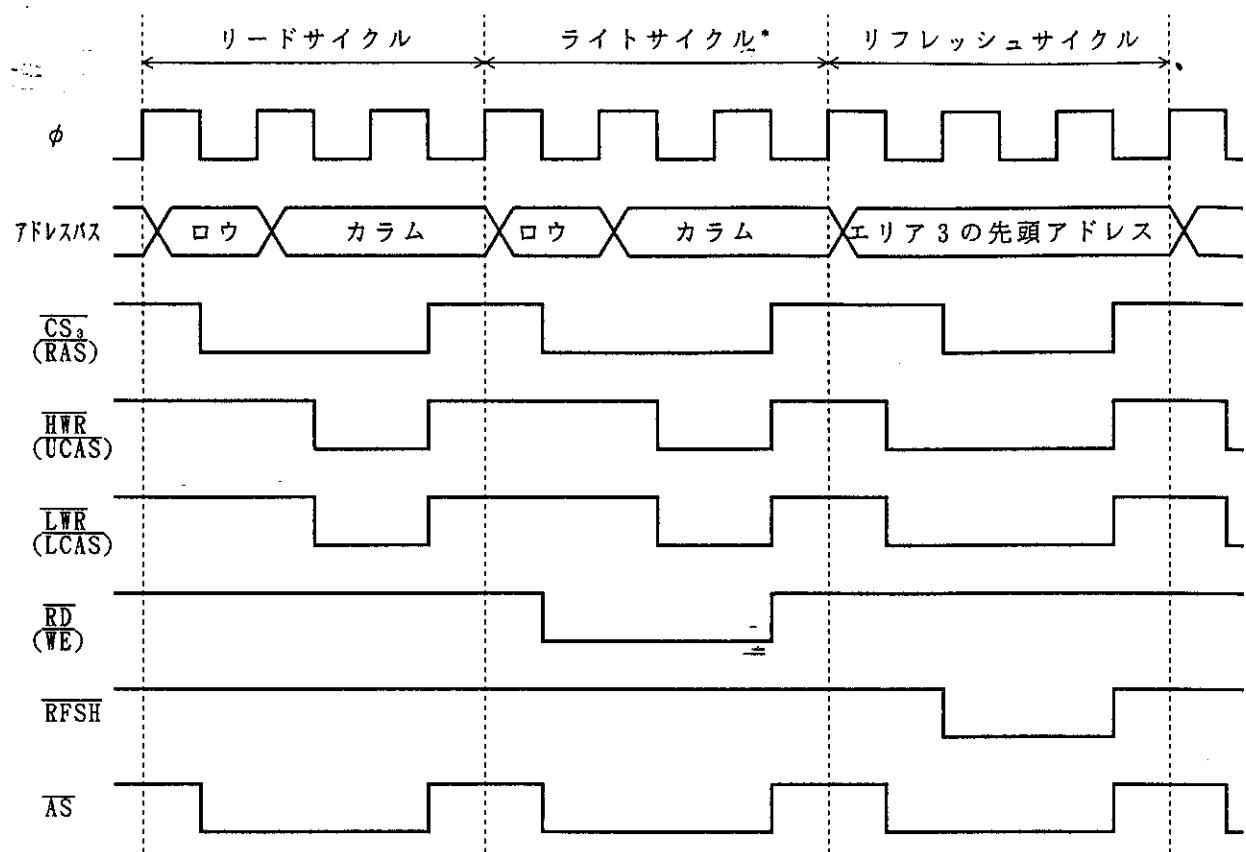

2 WE方式によるDRAMインターフェースを図7.5(1)に、また2 CAS方式によるDRAMインターフェースを図7.5(2)に示します。

【注】\* 16ビットアクセス時

図7.5 DRAM制御信号出力タイミング(1) (2WE方式)

【注】\* 16ビットアクセス時

図7.5 D R A M 制御信号出力タイミング(2) (2 CAS方式)

#### (4) リフレッシュサイクルの優先順位

バス権が同時に要求された場合の優先順位は次のようにになります。

(高) 外部バスマスター > リフレッシュコントローラ > DMAコントローラ > CPU(低)

詳細は、「6.3.7 バスアービタの動作」を参照してください。

#### (5) ウェイトステートの挿入

ASTCRのAST3を“1”にセットした場合、バスコントローラの設定によりバスサイクルおよびリフレッシュサイクルに対して、ウェイトステートを挿入することができます。

詳細は、「6.3.5 ウェイトモード」を参照してください。

#### (6) セルフリフレッシュモード

DRAMには、セルフリフレッシュ機能を持つものがあります。

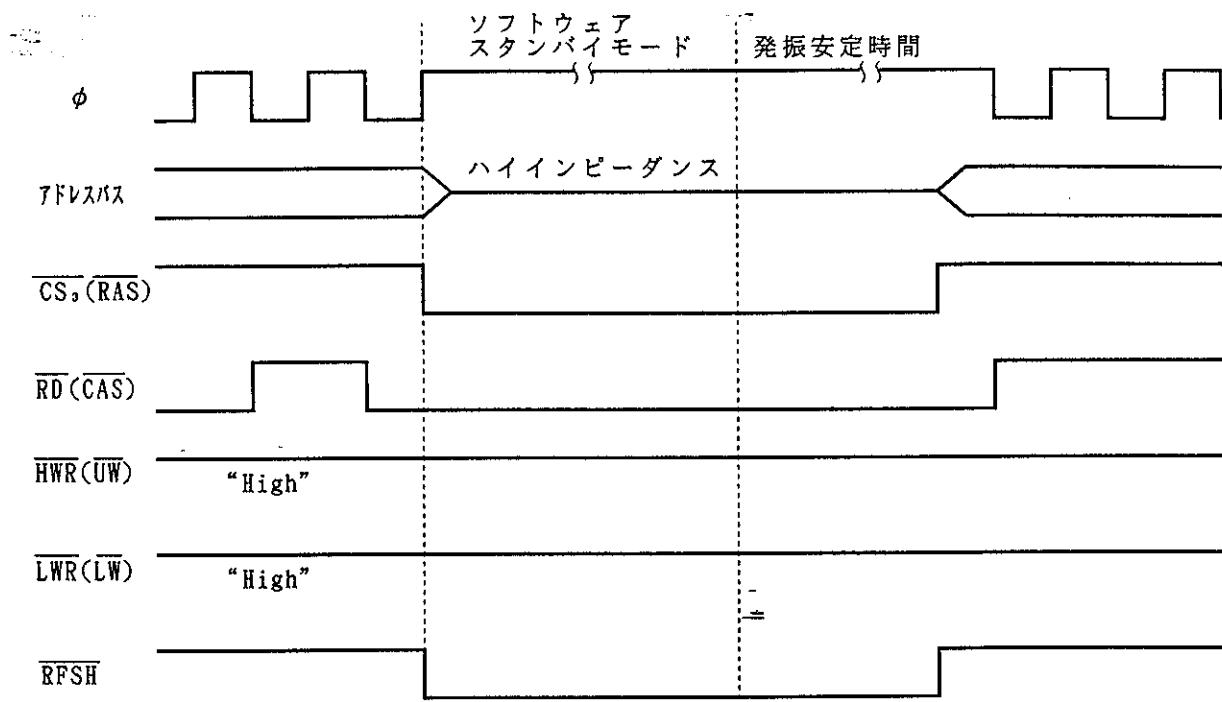

RFSHCRのSRFMDビットを“1”にセットした後、ソフトウェアスタンバイモードに遷移すると、CAS、RASの順に“Low”レベル出力となり、DRAMのセルフリフレッシュ機能を使用することができます。ソフトウェアスタンバイモードが解除されると、CAS、RASは“High”レベル出力となります。

表7.7にソフトウェアスタンバイモード時の端子状態を、また図7.6に信号出力タイミングを示します。

表7.7 ソフトウェアスタンバイモード時の端子状態(1)

(PSRAME = “0”、DRAME = “1”)

| 信号              | ソフトウェアスタンバイモード時            |                            |                               |                            |

|-----------------|----------------------------|----------------------------|-------------------------------|----------------------------|

|                 | SRFMD = “0”                |                            | SRFMD = “1”<br>(セルフリフレッシュモード) |                            |

|                 | CAS/ $\overline{WE}$ = “0” | CAS/ $\overline{WE}$ = “1” | CAS/ $\overline{WE}$ = “0”    | CAS/ $\overline{WE}$ = “1” |

| HWR             | ハイインピーダンス                  | ハイインピーダンス                  | “High”                        | “Low”                      |

| LWR             | ハイインピーダンス                  | ハイインピーダンス                  | “High”                        | “Low”                      |

| RD              | ハイインピーダンス                  | ハイインピーダンス                  | “Low”                         | “High”                     |

| CS <sub>3</sub> | “High”                     | “High”                     | “Low”                         | “Low”                      |

| RFSH            | “High”                     | “High”                     | “Low”                         | “Low”                      |

(a) 2 WE方式 (S R F M D = “1” の場合)

(b) 2 CAS 方式 (S R F M D = “1” の場合)

図 7.6 セルフリフレッシュモードの信号出力タイミング

(P S R A M E = “0”、D R A M E = “1” )

### (7) 低消費電力状態時の動作

リフレッシュコントローラは、スリープモードでも動作します。また、ハードウェアスタンバイモード時には動作を停止します。ソフトウェアスタンバイモード時には、RTCNTはイニシャライズされますが、RFSHCR、RTMCSRのビット5～3、RTCORはソフトウェアスタンバイモードに遷移する直前の状態を保持します。

### (8) 使用例

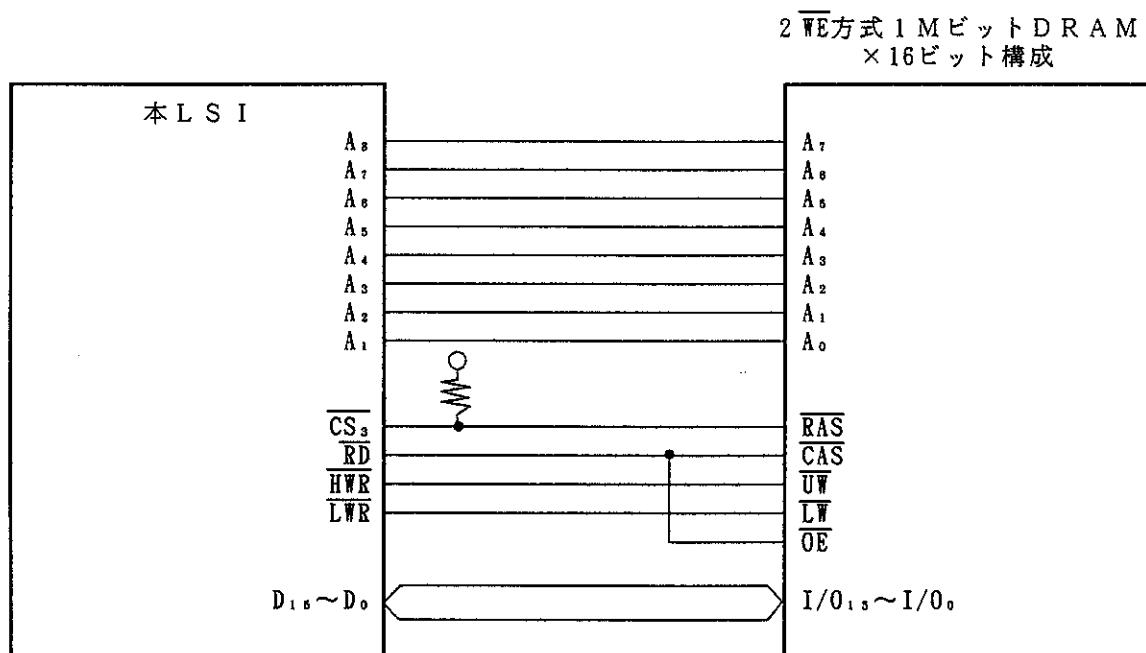

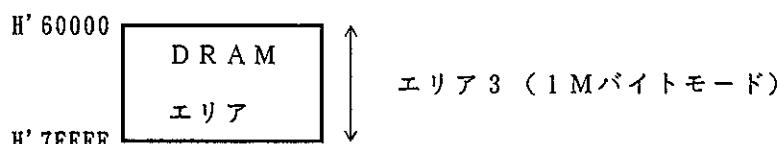

#### ① 2 WE方式 1 Mビット DRAMの接続例（1 Mバイトモード）

図7.7に2 WE方式の1 MビットDRAMの接続例とそのアドレスマップを示します。

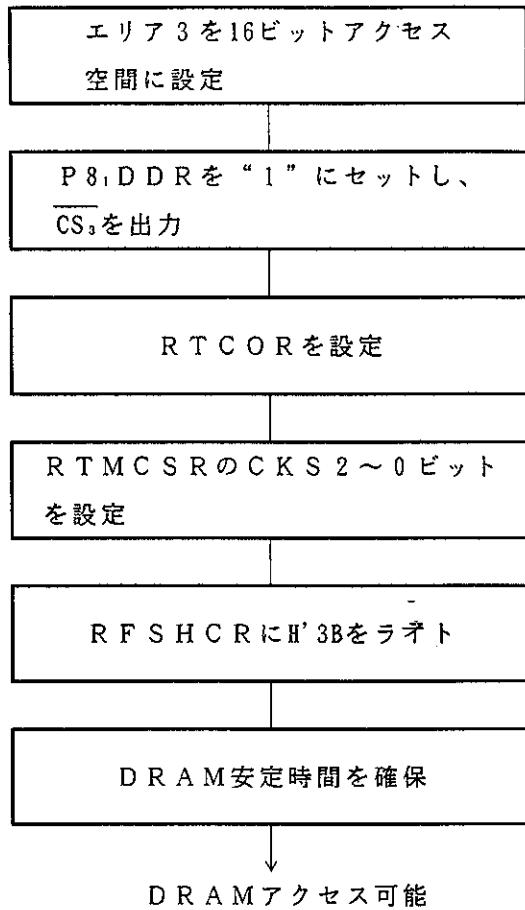

また、図7.8にそのときのプログラム設定順序を示します。DRAMは、電源投入直後、内部状態を安定させるためにリフレッシュサイクルを必要とします。したがって、他のタイマモジュールによる割込み、あるいはRTMCSRのビット7(CMF)がセットされる回数を数えるなどして、DRAMの安定期間を確保してください。リセット、またはスタンバイ直後の最初のリフレッシュ要求(CMFフラグのセット)は、リフレッシュサイクル実行に使用されませんので注意してください（図7.3参照）。

本機能を使用する場合は、DRAMデバイス特性をよくご確認の上、そのデバイスに適合する使い方をしてください。

(a) 接続例

(b) アドレスマップ

図7.7 2 WE方式 1 Mビット DRAMの接続例とアドレスマップ

図7.8 2WE方式1MビットDRAMの設定順序（1Mバイトモード）

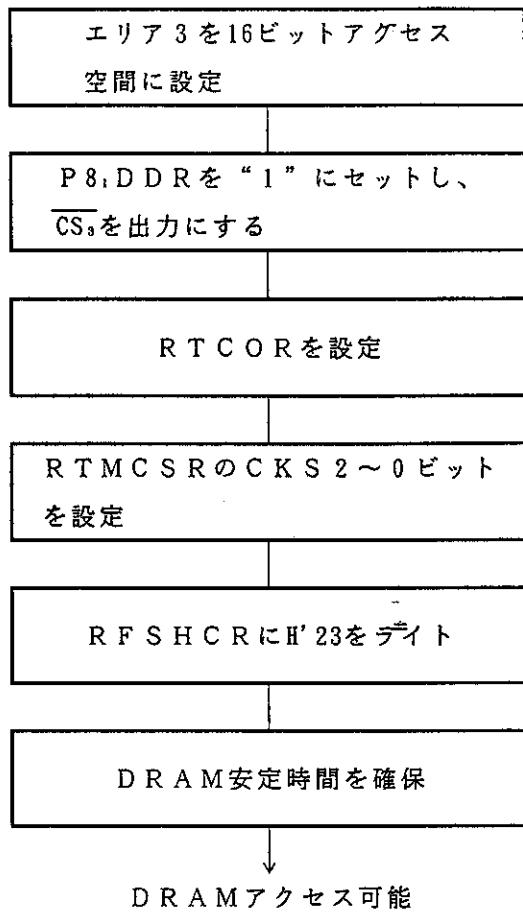

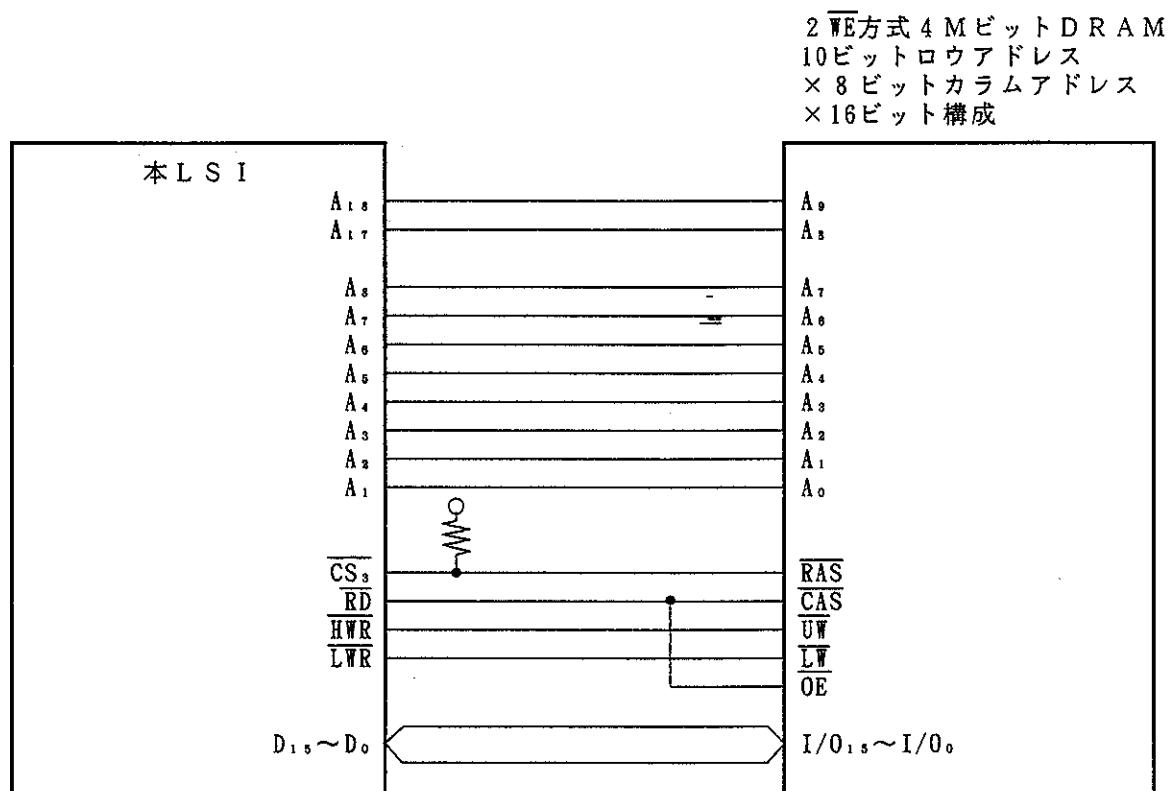

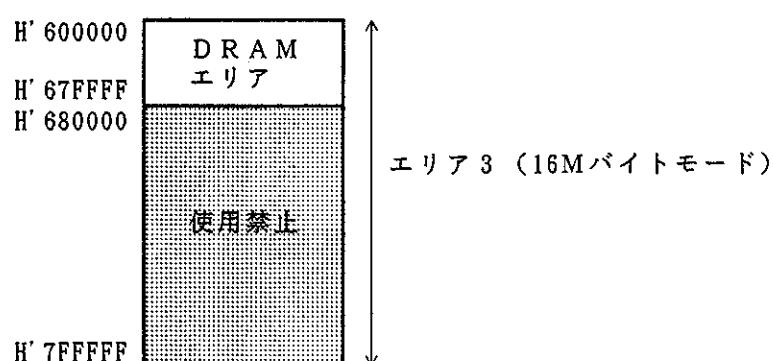

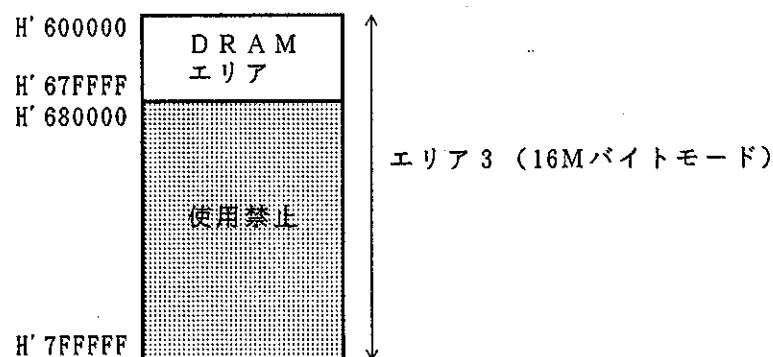

② 2 WE方式 4 Mビット D R A Mの接続例 (16Mバイトモード)

図7.9に、2 WE方式 4 Mビット D R A Mを1個使用する場合の接続例とそのアドレスマップを示します。また図7.10にそのときのプログラム設定手順を示します。

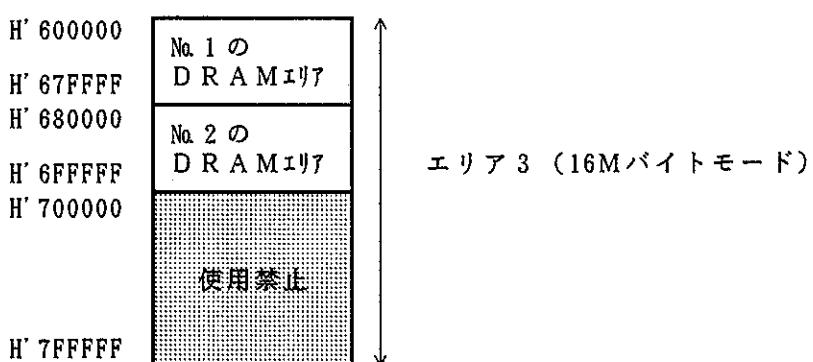

本例では、10ビットロウアドレ<sup>S</sup>ス×8ビットカラムアドレ<sup>S</sup>スのD R A Mを使用して、H'600000～H'67FFFFがD R A Mエリアに設定されています。

(a) 接続例

(b) アドレスマップ

図7.9 2 WE方式 4 Mビット D R A Mの接続例とアドレスマップ

図7.10 2WE方式 4Mビット DRAM (10ビットロウアドレス×8ビットカラムアドレスの場合)

の設定順序 (16Mバイトモード)

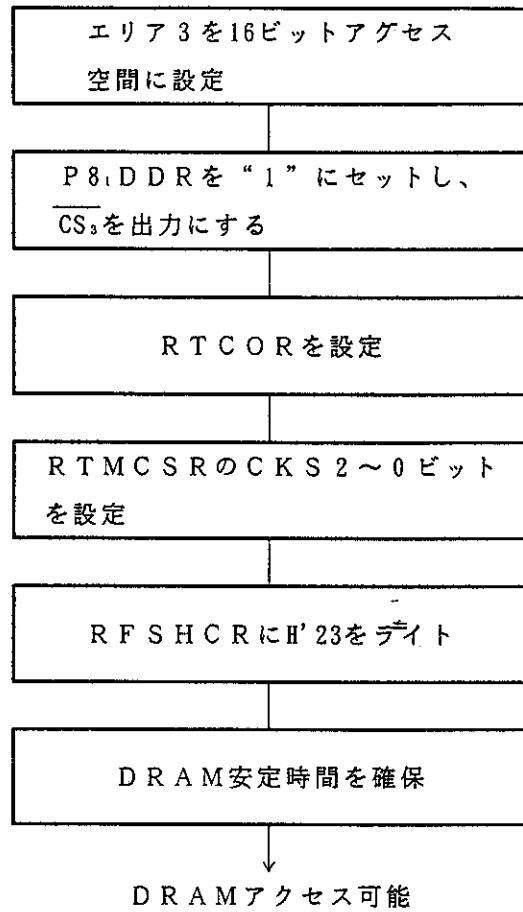

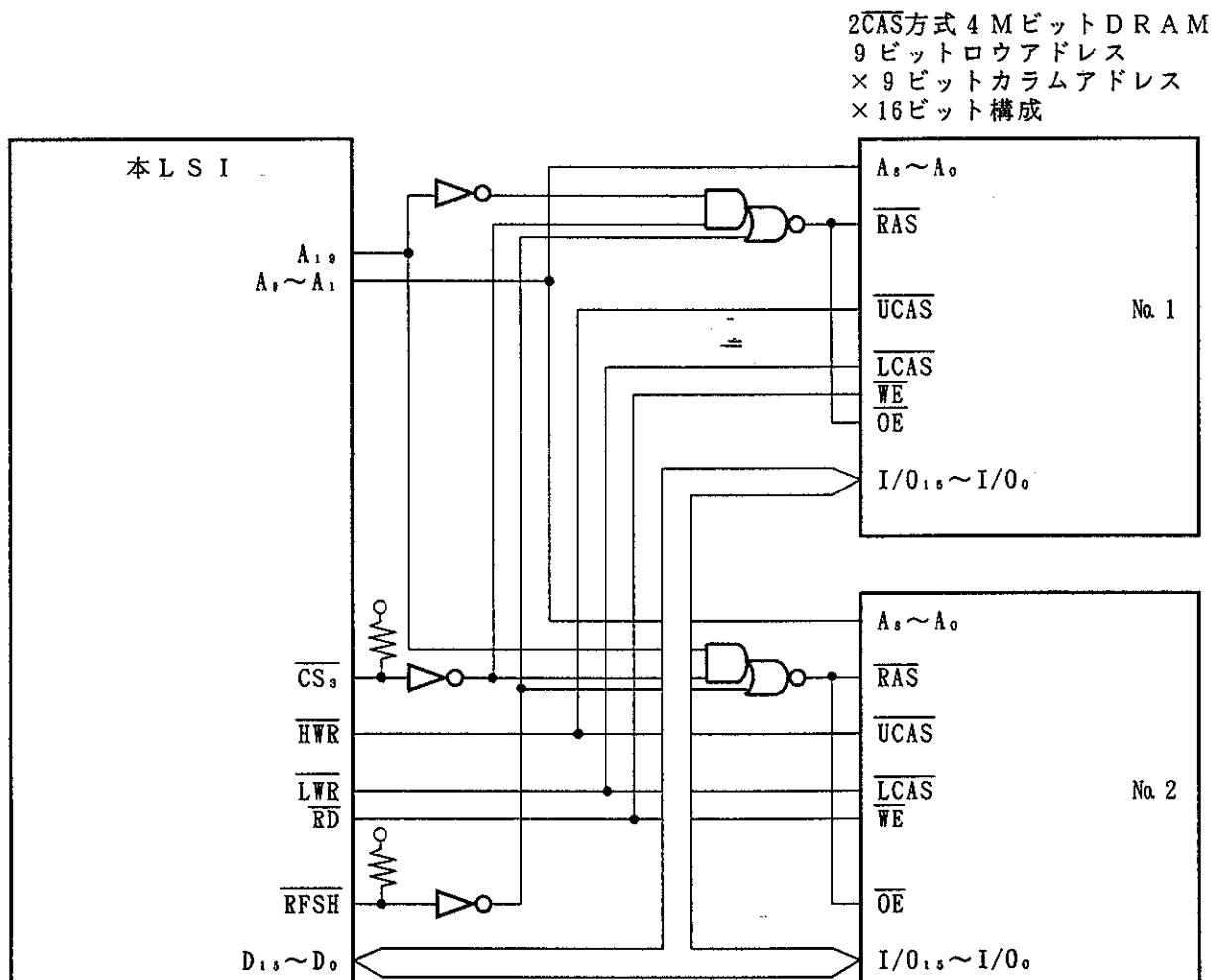

③ 2 CAS方式 4 Mビット D R A Mの使用例 (16Mバイトモード)

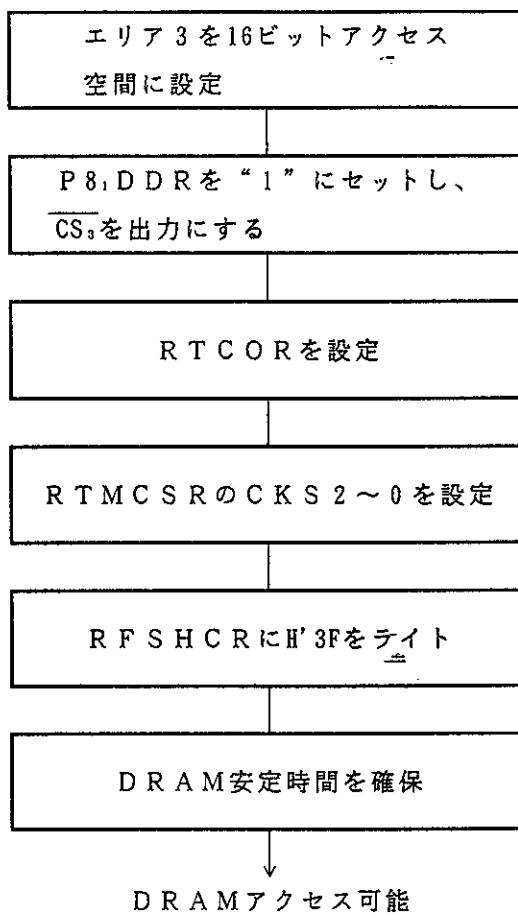

図7.11に2CAS方式の4 MビットD R A Mを1個使用する場合の接続例とそのアドレスマップを示します。また、図7.12にそのときのプログラム設定順序を示します。

本例では、9ビットロウアドレス×9ビットカラムアドレスのD R A Mを使用して、H'600000～H'67FFFFがD R A Mエリアに設定されています。

(a) 接続例

(b) アドレスマップ

図7.11 2 CAS方式 4 Mビット D R A Mの接続例とアドレスマップ

図 7.12 2 CAS方式 4 Mビット DRAM (9ビットロウアドレス×9ビットカラムアドレスの場合)

の設定順序 (16Mバイトモード)

④ 複数チップの4MビットDRAMの接続例（16Mバイトモード）

図7.13に2CAS方式4MビットDRAMを2個使用する場合の接続例とそのアドレスマップを示します。上位アドレス $A_{10}$ 、 $A_9$ をデコードすることにより、最大4個のDRAMをエリア3に接続できます。

また、図7.14にそのときのプログラム設定順序を示します。本例では、9ビットロウアドレス×9ビットカラムアドレスのタイプのものを使用しています。すべてのチップを同時にリフレッシュする必要があるため、RFSH端子を使用しなければなりません。

(a) 接続例

(b) アドレスマップ

図 7.14 複数チップの2 CAS方式4MビットDRAM(9ビットロウアドレス×9ビットカラムアドレスの場合)の設定順序(16Mバイトモード)

### 7.3.3 PSRAMリフレッシュ制御

#### (1) リフレッシュ要求の周期とリフレッシュサイクルの実行

DRAMインターフェースと同様に、RTCORとRTMCSRのCKS2～CKS0ビットで、リフレッシュ要求の周期を設定します。

PSRAMのリード／ライトサイクルおよびリフレッシュサイクルに要するステート数は、DRAMと同様です（表7.4）。また、状態遷移も図7.3に示すとおりです。

#### (2) PSRAM制御信号

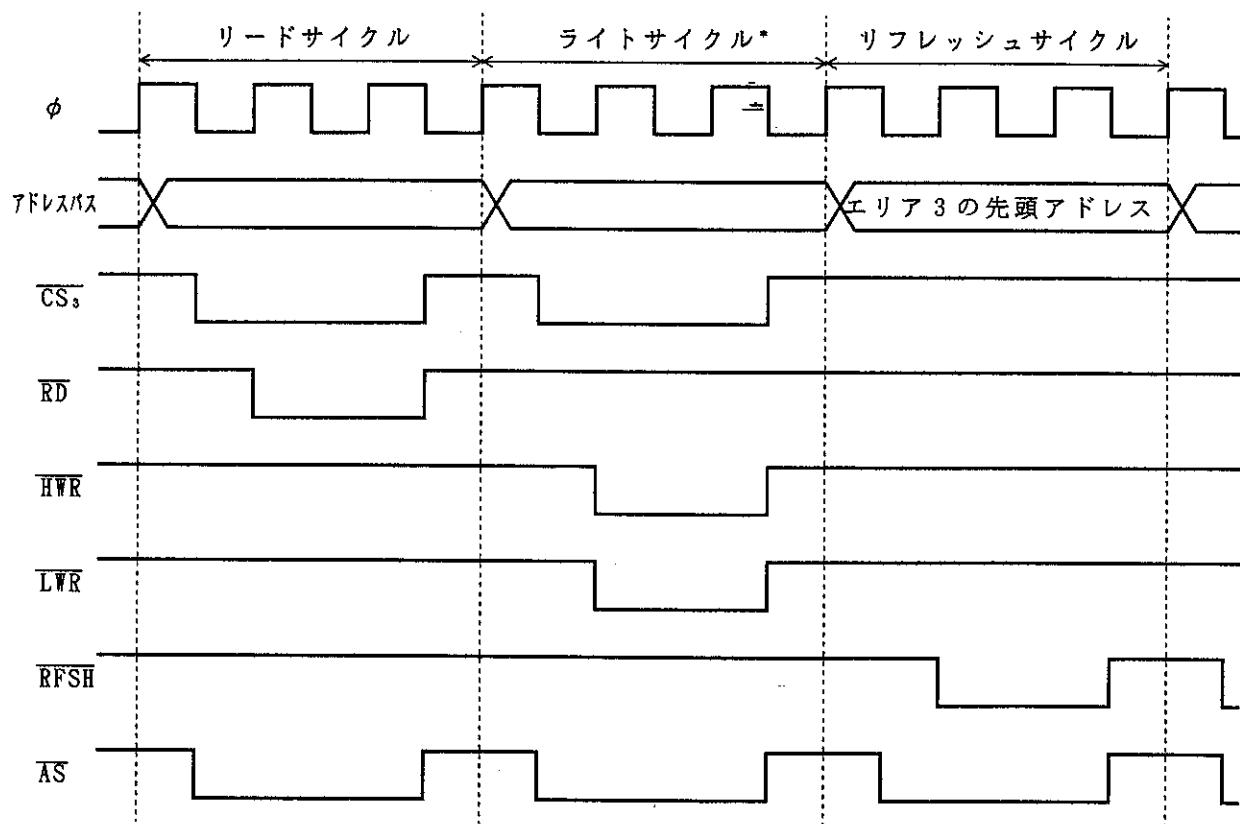

PSRAMに対するリードサイクル、ライトサイクル、およびリフレッシュサイクルを図7.15に示します。

【注】\* 16ビットアクセス時

図7.15 PSRAM制御信号出力タイミング

### (3) リフレッシュサイクルの優先順位

バス権が同時に要求された場合の優先順位は次のようにになります。

(高) 外部バスマスター > リフレッシュコントローラ > DMAコントローラ > CPU (低)

詳細は、「6.3.7 バスアービタの動作」を参照してください。

### (4) ウェイットステートの挿入

ASTCRのAST3を“1”にセットした場合、ウェイットステートコントローラ(WSC)によりバスサイクルおよびリフレッシュサイクルに対して、ウェイットステートを挿入することができます。

設定の詳細は、「6.3.5 ウェイットモード」を参照してください。

### (5) セルフリフレッシュモード

PSRAMはセルフリフレッシュ機能をもつものがあります。

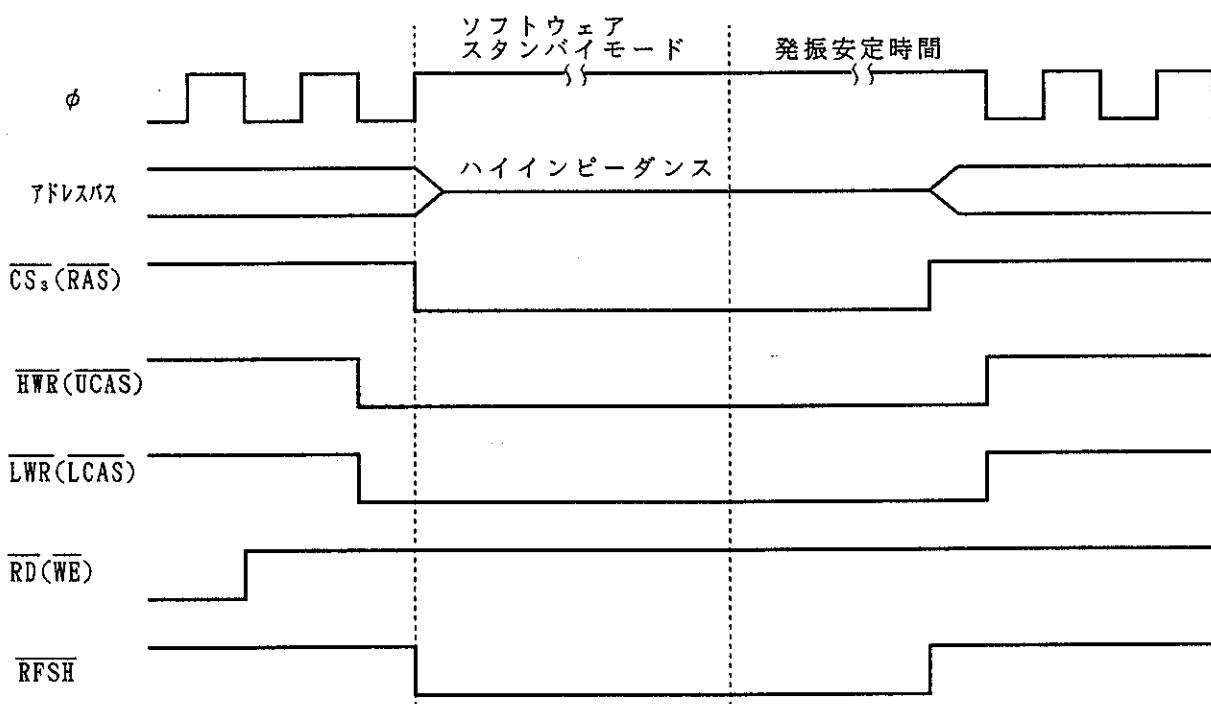

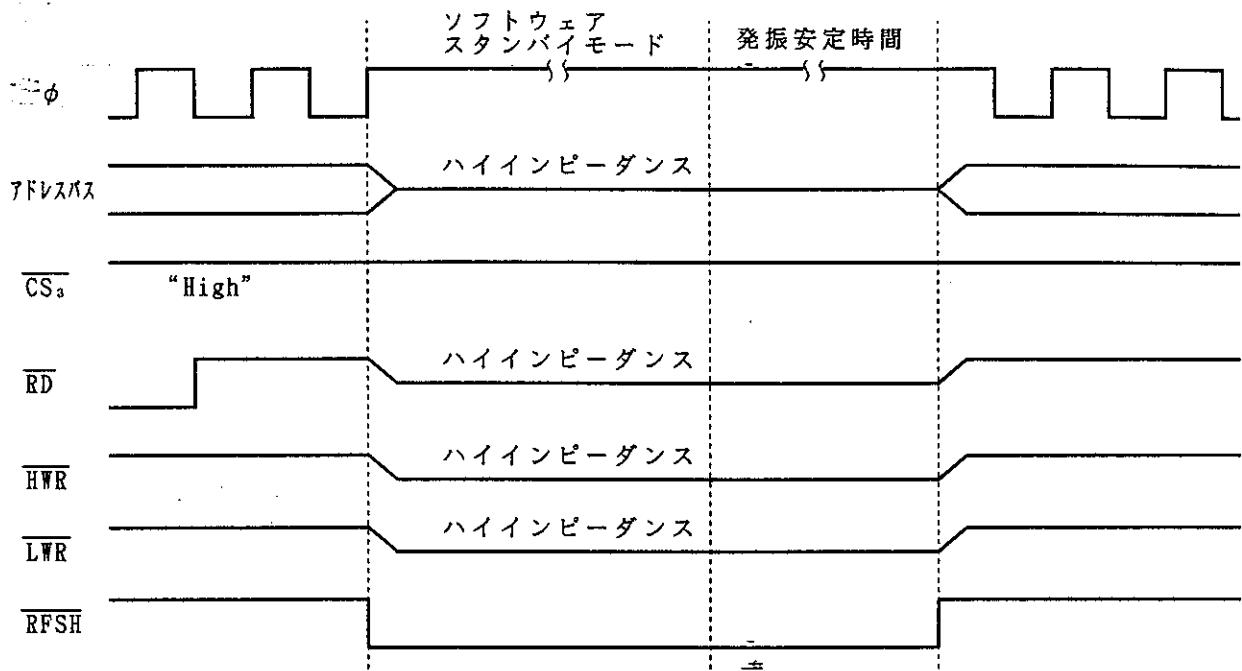

本LSIでは、RFSHCRのSRFMDビットを“1”にセットした後、ソフトウェアスタンバイモードに遷移すると、CS<sub>3</sub>が“High”レベル出力、RFSHが“Low”レベル出力となり、PSRAMのセルフリフレッシュ機能を利用できます。ソフトウェアスタンバイモードが解除されると、RFSHは“High”レベル出力となります。

表7.8にソフトウェアスタンバイモード時の端子状態を、また図7.16に信号出力タイミングを示します。

表7.8 ソフトウェアスタンバイモード時の端子状態(2)

(PSRAME = “1”、DRAME = “0”)

| 信号              | ソフトウェアスタンバイモード |                               |

|-----------------|----------------|-------------------------------|

|                 | SRFMD = “0”    | SRFMD = “1”<br>(セルフリフレッシュモード) |

| CS <sub>3</sub> | “High”         | “High”                        |

| RD              | ハイインピーダンス      | ハイインピーダンス                     |

| HWR             | ハイインピーダンス      | ハイインピーダンス                     |

| LWR             | ハイインピーダンス      | ハイインピーダンス                     |

| RFSH            | “High”         | “Low”                         |

図 7.16 セルフリフレッシュモードの信号出力タイミング

(PSRAME = "1"、DRAME = "0")

#### (6) 低消費電力状態時の動作

リフレッシュコントローラは、スリープモードでも動作します。また、ハードウェアスタンバイモード時には動作を停止します。ソフトウェアスタンバイモード時には、RTCNTはイニシャライズされますが、RFSHCR、RTMCSRのビット5～3、およびRTCORはソフトウェアスタンバイモードに遷移する直前の状態を保持します。

#### (7) 使用例

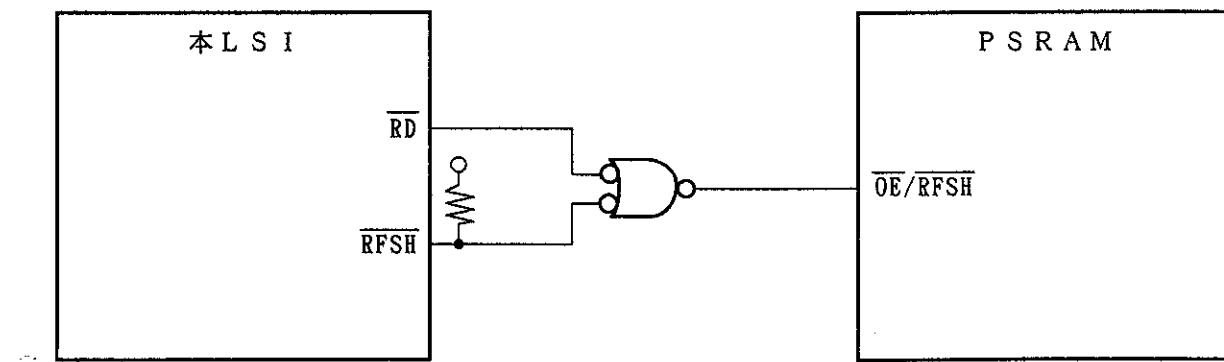

PSRAMには、OE端子とRFSH端子が個別に設けられているものと、OE/RFSH端子として1つになっているものがあります。

図7.17にOE/RFSH信号を発生する回路例を示します。デバイス特性をよくご確認の上、適合する回路を設計してください。

図7.18にプログラム設定順序を示します。

図 7.17 OE/RFSH信号の例

図7.18 PSRAMのプログラム設定順序

#### 7.3.4 インターバルタイマ

リフレッシュコントローラをインターバルタイマとして使用する場合、PSRAM\_Eを“0”、かつDRAAMEを“0”にクリアします。RTCORを設定後、RTMCSRのCKS2～CKS0ビットにより入力クロックを選択し、CMIEビットを“1”にセットします。

##### (1) コンペアマッチフラグのセットタイミングとコンペアマッチによるクリア

RTCSRのCMFフラグは、RTCORとRTCNTの値が一致したときに出力されるコンペアマッチ信号により“1”にセットされます。コンペアマッチ信号は一致した最後のステート（RTCNTが一致したカウント値を更新するタイミング）で発生します。

したがって、RTCNTとRTCORが一致した後、カウントアップクロックが発生するまでコンペアマッチ信号は発生しません。このタイミングを図7.19に示します。

図 7.19 CMF フラグセットタイミング

### (2) 低消費電力状態時の動作

インターバルタイマは、スリープモードでも動作します。また、ハードウェアスタンバイモード時は動作を停止します。ソフトウェアスタンバイモード時、RTCNTとRTMC SRのビット7、6がイニシャライズされますが、RTMC SRのビット5～3、およびRTCCRはソフトウェアスタンバイモードに遷移する直前の状態を保持します。

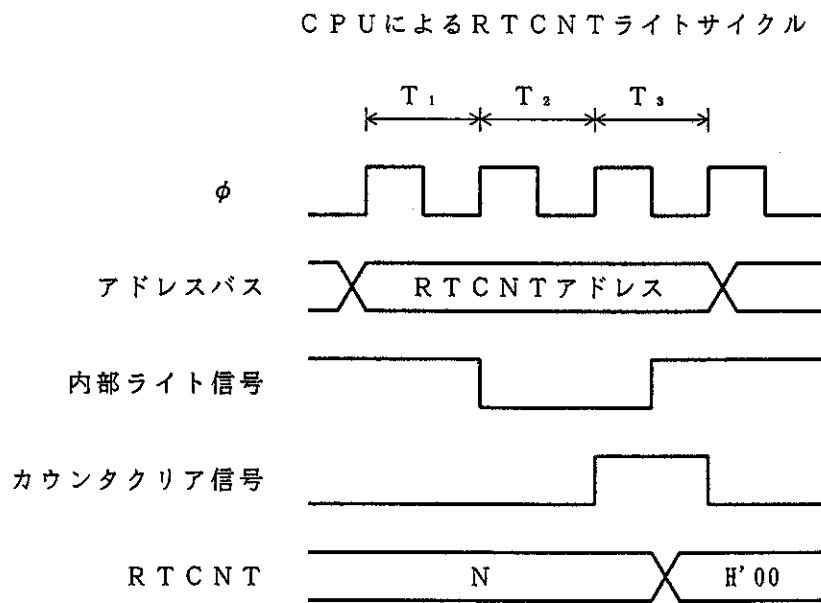

### (3) RTCNT のライトとカウンタクリアの競合

RTCNT のライトサイクル中の T<sub>3</sub> ステートで、カウンタクリアが発生するとカウンタへのライトは行われず、クリアが優先されます。

図 7.20 にこのタイミングを示します。

図 7.20 RTCNT のライトとクリアの競合

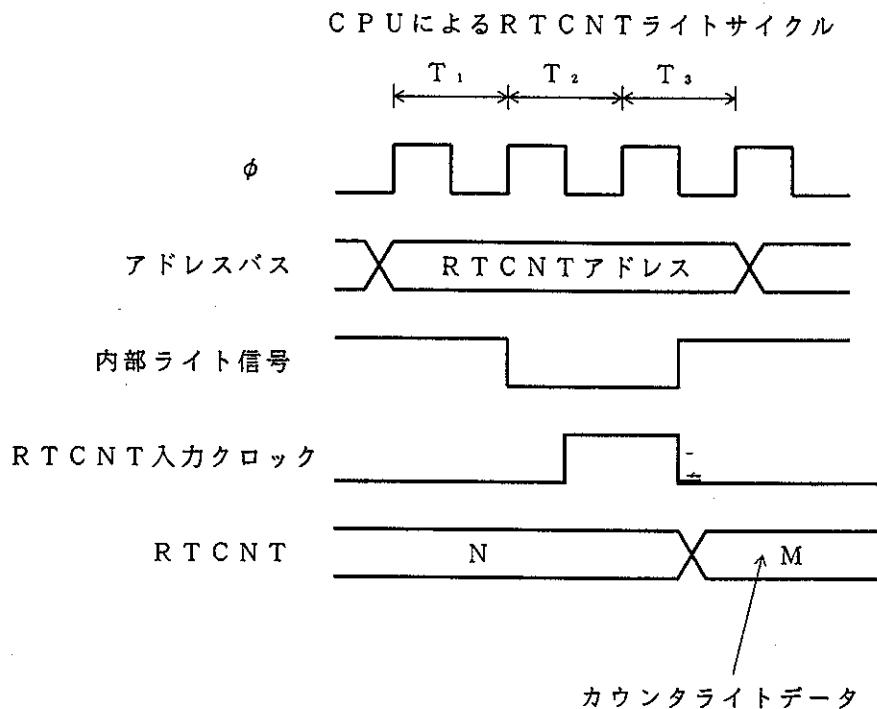

(4) RTCNTのライトとカウントアップの競合

RTCNTのライトサイクル中のT<sub>3</sub>ステートでカウントアップが発生しても、カウントアップされずに、カウンタライトが優先されます。

図7.21にこのタイミングを示します。

図7.21 RTCNTのライトとカウントアップの競合

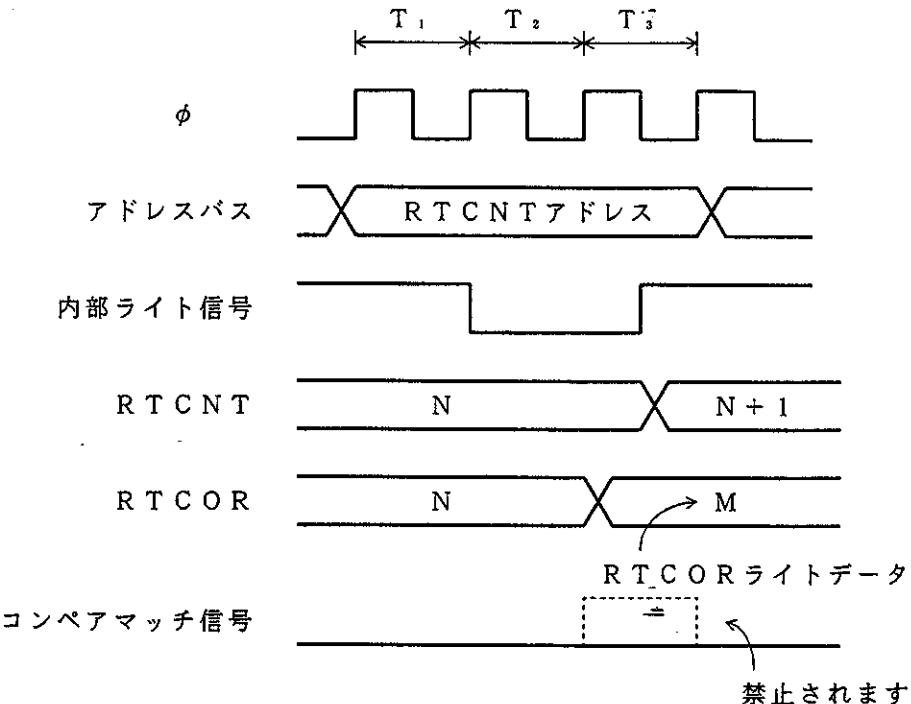

(5) RTCORのライトとコンペアマッチの競合

RTCORのライトサイクル中のT<sub>3</sub>ステートでコンペアマッチが発生しても、図7.22のようにRTCORのライトが優先され、コンペアマッチ信号は禁止されます。

### C P U による R T C O R ライトサイクル

図 7.22 RTCOR のライトとコンペアマッチの競合

#### (6) 内部クロックの切換えと RTCNT の動作

内部クロックを切換えるタイミングによっては、RTCNTがカウントアップされてしまう場合があります。内部クロックの切換えタイミング（CKS2～CKS0ビットの書換え）とRTCNT動作の関係を表7.9に示します。

内部クロックからRTCNTクロックを生成する場合、内部クロックの立下がりエッジで検出しています。そのため、表7.9のNo.3のように“High”→“Low”になるようなクロックの切換えを行うと、切換えタイミングを立下がりエッジとみなしてRTCNTクロックが発生し、RTCNTがカウントアップされてしまいます。

表 7.9 内部クロックの切換えとRTCNT動作(1)

| No. | CKS2～CKS0ビット<br>書換えタイミング              | RTCNT動作           |

|-----|---------------------------------------|-------------------|

| 1   | “Low”→“Low”<br>レベルの切換え <sup>*1</sup>  | <p>CKS ビット書換え</p> |

| 2   | “Low”→“High”<br>レベルの切換え <sup>*2</sup> | <p>CKS ビット書換え</p> |

【注】<sup>\*1</sup> “Low”レベル→停止、および停止→“Low”レベルの場合を含みます。

<sup>\*2</sup> 停止→“High”レベルの場合を含みます。

表7.9 内部クロックの切換えとRTCNT動作(2)

| No. | CKS2~CKS0ビット<br>書換えタイミング              | RTCNT動作          |

|-----|---------------------------------------|------------------|

| 3   | "High"→"Low"<br>レベルの切換え <sup>*3</sup> | <p>CKSビット書換え</p> |

| 4   | "High"→"High"<br>レベルの切換え              | <p>CKSビット書換え</p> |

【注】<sup>\*3</sup> "High" レベル→停止の場合を含みます。

<sup>\*4</sup> 切換えのタイミングを立下がりエッジとみなすために発生し、RTCNTはカウントアップしてしまいます。

#### 7.4 割込み要因

リフレッシュコントローラをインターバルタイマとして使用する場合、コンペアマッチ割込み(CM1)要求を発生します。コンペアマッチ割込み要求はRTMC SRのCMIEビットで許可または禁止することができます。

## 7.5 使用上の注意

DRAMリフレッシュ機能、あるいはPSRAMリフレッシュ機能の使用に際して、以下の点に注意してください。

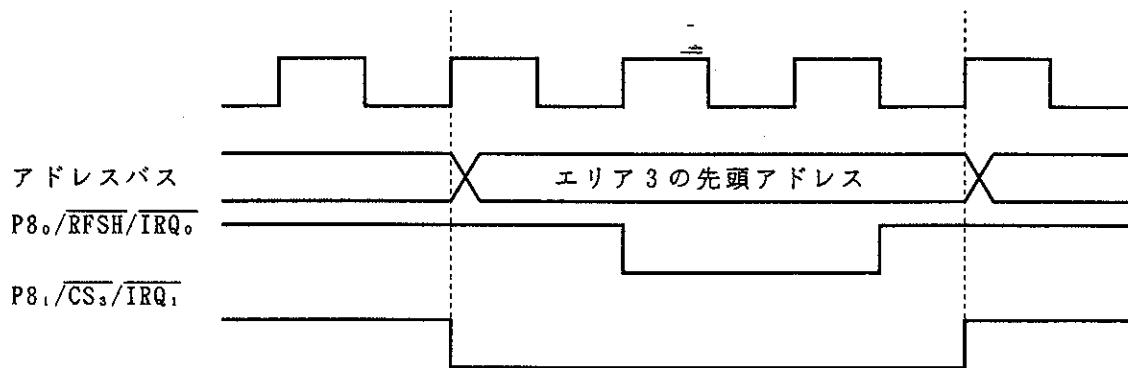

- (1) リフレッシュコントローラは、一度直接接続したDRAMまたはPSRAMの接続を切断した場合\*、P8<sub>0</sub>/RFSH/IRQ<sub>0</sub>端子とP8<sub>1</sub>/CS<sub>3</sub>/IRQ<sub>1</sub>端子が同時に“Low”レベル出力となる場合があります。

【注】\* リフレッシュコントロールレジスタ(RFSHCR)内のDRAMイネーブル(DRAM E)またはPSRAMイネーブル(PSRAME)を一度“1”にセットした後に、DRAMEまたはPSRAMEを“0”にクリアした場合。

図7.23 DRAM/PSRAM接続の切り離し時の動作

- (2) 外部バス権解放状態、ソフトウェアスタンバイモード、またはバスサイクルがウェイトステートの挿入により長く続く場合、リフレッシュサイクルは実行されません。したがって、これらの状態では、別の方でリフレッシュを行う必要があります。

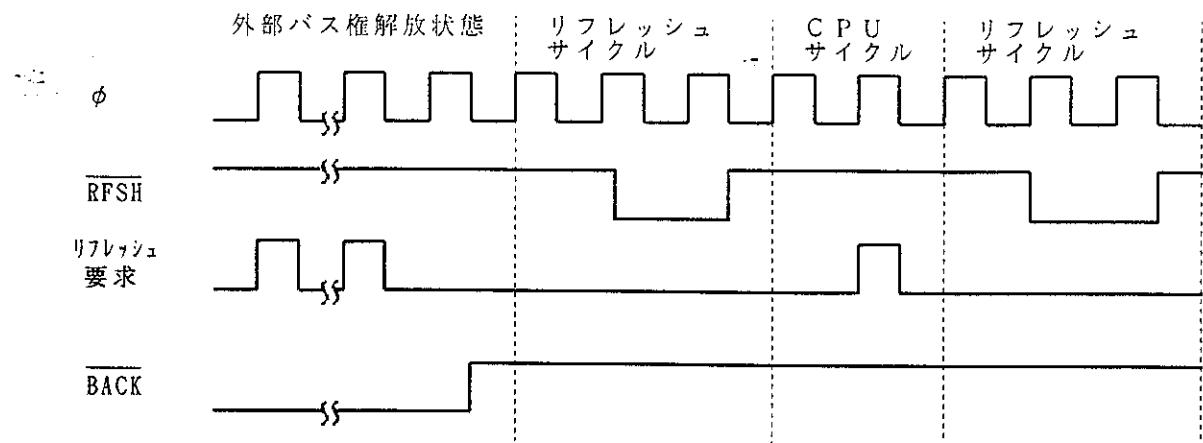

- (3) 外部バス権解放状態中に内部でリフレッシュ要求が発生した場合、最初の要求が保持され、バス権解放状態解除後、リフレッシュサイクルが1回だけ実行されます。図7.24にその場合のバスサイクルを示します。

図 7.24 バス解放状態時のリフレッシュサイクル

- (4) バスサイクルがウェイットステートの挿入により長く続く場合も、外部バス権解放状態と同様に、最初の要求が保持されます。

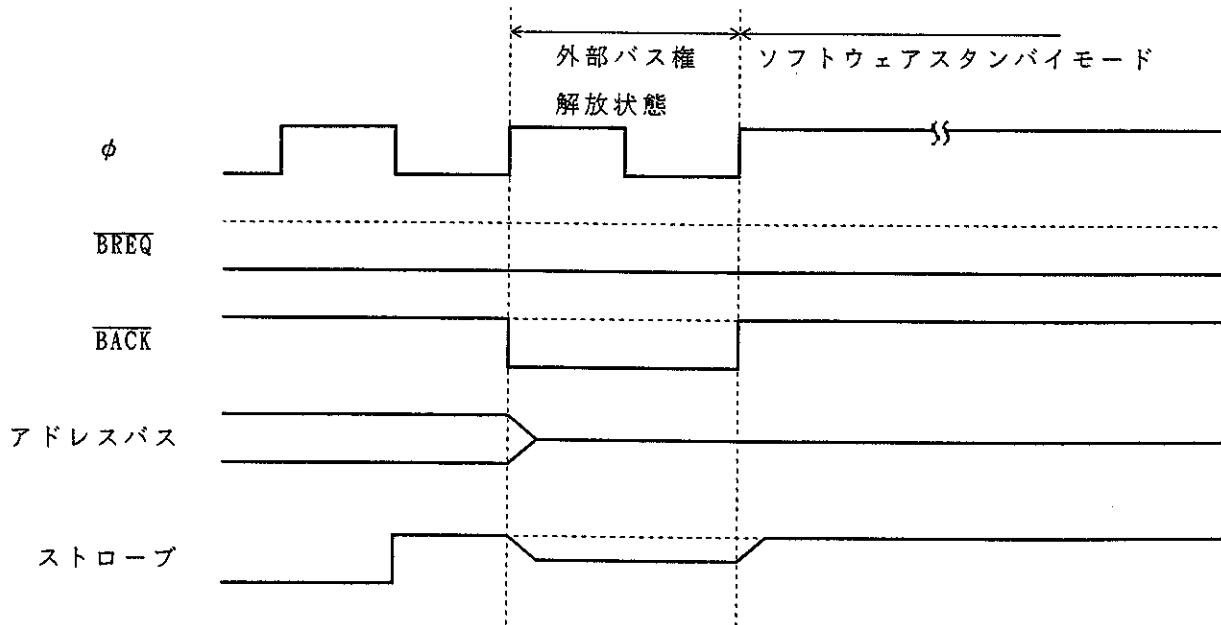

- (5) ソフトウェアスタンバイモードへ遷移するとき、外部バスマスターからのバス権要求が競合すると、ソフトウェアスタンバイモードへの遷移の直前に 1 ステートバス解放状態が発生することがあります（図7.25参照）。

ソフトウェアスタンバイモードを使用するときは、SLEEP 命令を実行する前に、BRCR の BRL\_E ビットを “0” にクリアしてください。

また、セルフリフレッシュモードへの遷移でも同様の競合により、ストローブ波形出力が保証されないことがあります。これも BRCR の BRL\_E ビットを “0” にクリアすることにより防止できます。

図 7.25 バス解放状態とソフトウェアスタンバイモードの競合