# 11. プログラムルタイミング パターンコントローラ (T P C)

## 第11章 目次

|         |                                |     |

|---------|--------------------------------|-----|

| 11.1    | 概要                             | 437 |

| 11.1.1  | 特長                             | 437 |

| 11.1.2  | ブロック図                          | 438 |

| 11.1.3  | 端子構成                           | 439 |

| 11.1.4  | レジスタ構成                         | 440 |

| 11.2    | 各レジスタの説明                       | 441 |

| 11.2.1  | ポートAデータディレクションレジスタ (P A D D R) | 441 |

| 11.2.2  | ポートAデータレジスタ (P A D R)          | 441 |

| 11.2.3  | ポートBデータディレクションレジスタ (P B D D R) | 442 |

| 11.2.4  | ポートBデータレジスタ (P B D R)          | 442 |

| 11.2.5  | ネクストデータレジスタA (N D R A)         | 443 |

| 11.2.6  | ネクストデータレジスタB (N D R B)         | 445 |

| 11.2.7  | ネクストデータイネーブルレジスタA (N D E R A)  | 447 |

| 11.2.8  | ネクストデータイネーブルレジスタB (N D E R B)  | 448 |

| 11.2.9  | T P C出力コントロールレジスタ (T P C R)    | 449 |

| 11.2.10 | T P C出力モードレジスタ (T P M R)       | 452 |

| 11.3    | 動作説明                           | 455 |

| 11.3.1  | 概要                             | 455 |

| 11.3.2  | 出力タイミング                        | 456 |

| 11.3.3  | T P C出力通常動作                    | 457 |

| 11.3.4  | T P C出力ノンオーバラップ動作              | 459 |

| 11.3.5  | インプットキャプチャによるT P C出力           | 461 |

| 11.4    | 使用上の注意                         | 462 |

| 11.4.1  | T P C出力端子の動作                   | 462 |

| 11.4.2  | ノンオーバラップ動作時の注意                 | 462 |

## 11.1 概要

H8/3048シリーズは、16ビットインテグレーテッドタイマユニット（ITU）をタイムベースとしてパルス出力を行うプログラマブルタイミングパターンコントローラ（TPC）を内蔵しています。TPCは4ビット単位のTPC出力グループ3～0から構成されており、これらは同時に動作させることも、独立に動作させることも可能です。

### 11.1.1 特長

TPCの特長を以下に示します。

#### ■出力データ16ビット

最大16ビットのデータ出力が可能で、TPC出力をビット単位に許可することができます。

#### ■4系統の出力可能

4ビット単位のグループで出力トリガ信号が選択可能で、最大4ビット×4系統の出力を行うことができます。

#### ■出力トリガ信号を選択可能

ITUの4チャネルのコンペアマッチ信号の中から、グループごとに出力トリガ信号を選択することができます。

#### ■ノンオーバラップ動作

複数のパルス出力の間のノンオーバラップ期間を設定することができます。

#### ■DMAコントローラ（DMAC）との連携動作可能

出力トリガ信号に選択したコンペアマッチ信号でDMACを起動することにより、CPUの介在なくデータを順次出力することができます。

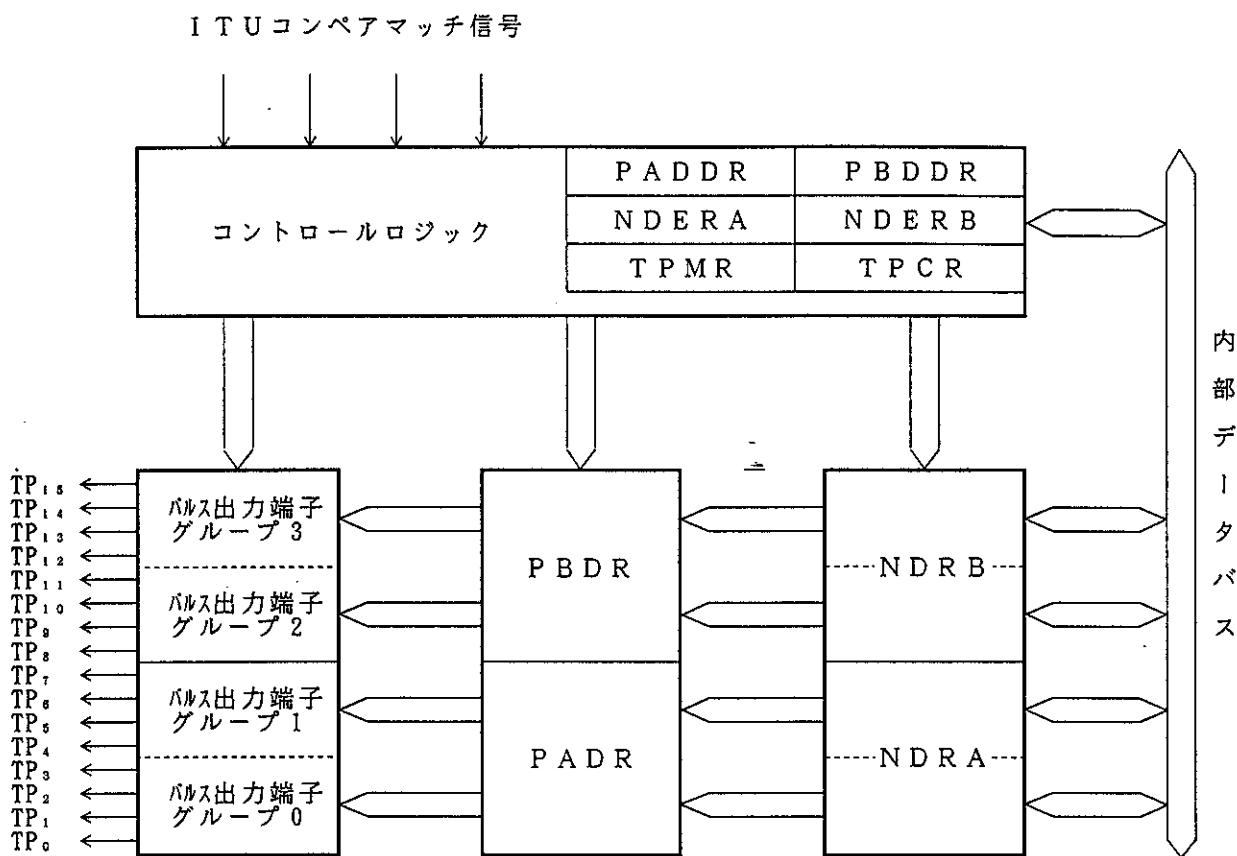

### 11.1.2 ブロック図

TPCのブロック図を図11.1に示します。

#### 《記号説明》

- TPMR : TPC出力モードレジスタ

- TPCR : TPC出力コントロールレジスタ

- N DER B : ネクストデータタイネーブルレジスタ B

- N DER A : ネクストデータタイネーブルレジスタ A

- P B DDR : ポート B データディレクションレジスタ

- P ADDR : ポート A データディレクションレジスタ

- N DRB : ネクストデータレジスタ B

- N DRA : ネクストデータレジスタ A

- P B DR : ポート B データレジスタ

- P A DR : ポート A データレジスタ

図11.1 TPCのブロック図

### 11.1.3 端子構成

TPCの端子構成を表11.1に示します。

表11.1 端子構成

| 名 称     | 略 称              | 入 出 力 | 機 能         |

|---------|------------------|-------|-------------|

| TPC出力0  | TP <sub>0</sub>  | 出 力   | グループ0のパルス出力 |

| TPC出力1  | TP <sub>1</sub>  | 出 力   |             |

| TPC出力2  | TP <sub>2</sub>  | 出 力   |             |

| TPC出力3  | TP <sub>3</sub>  | 出 力   |             |

| TPC出力4  | TP <sub>4</sub>  | 出 力   | グループ1のパルス出力 |

| TPC出力5  | TP <sub>5</sub>  | 出 力   |             |

| TPC出力6  | TP <sub>6</sub>  | 出 力   |             |

| TPC出力7  | TP <sub>7</sub>  | 出 力   |             |

| TPC出力8  | TP <sub>8</sub>  | 出 力   | グループ2のパルス出力 |

| TPC出力9  | TP <sub>9</sub>  | 出 力   |             |

| TPC出力10 | TP <sub>10</sub> | 出 力   |             |

| TPC出力11 | TP <sub>11</sub> | 出 力   |             |

| TPC出力12 | TP <sub>12</sub> | 出 力   | グループ3のパルス出力 |

| TPC出力13 | TP <sub>13</sub> | 出 力   |             |

| TPC出力14 | TP <sub>14</sub> | 出 力   |             |

| TPC出力15 | TP <sub>15</sub> | 出 力   |             |

#### 11.1.4 レジスタ構成

T P C のレジスタ構成を表11.2に示します。

表11.2 レジスタ構成

| アドレス <sup>*1</sup>              | 名 称                | 略 称       | R/W                 | 初期値  |

|---------------------------------|--------------------|-----------|---------------------|------|

| H'FFD1                          | ポートAデータディレクションレジスタ | P A D D R | W                   | H'00 |

| H'FFD3                          | ポートAデータレジスタ        | P A D R   | R/(W) <sup>*2</sup> | H'00 |

| H'FFD4                          | ポートBデータディレクションレジスタ | P B D D R | W                   | H'00 |

| H'FFD6                          | ポートBデータレジスタ        | P B D R   | R/(W) <sup>*2</sup> | H'00 |

| H'FFA0                          | T P C 出力モードレジスタ    | T P M R   | R/W                 | H'F0 |

| H'FFA1                          | T P C 出力コントロールレジスタ | T P C R   | R/W                 | H'FF |

| H'FFA2                          | ネクストデータイネーブルレジスタB  | N D E R B | R/W                 | H'00 |

| H'FFA3                          | ネクストデータイネーブルレジスタA  | N D E R A | R/W                 | H'00 |

| H'FFA5/<br>H'FFA7 <sup>*3</sup> | ネクストデータレジスタA       | N D R A   | R/W                 | H'00 |

| H'FFA4/<br>H'FFA6 <sup>*3</sup> | ネクストデータレジスタB       | N D R B   | R/W                 | H'00 |

【注】<sup>\*1</sup> アドレスの下位16ビットを示しています。

<sup>\*2</sup> T P C 出力として使用しているビットは、ライトできません。

<sup>\*3</sup> T P C R の設定により T P C 出力グループ0とT P C 出力グループ1の出力トリガが同一の場合はN D R A のアドレスはH'FFA5となり、出力トリガが異なる場合はグループ0に対応するN D R A のアドレスはH'FFA7、グループ1に対応するN D R A のアドレスはH'FFA5となります。

同様に、T P C R の設定により T P C 出力グループ2とT P C 出力グループ3の出力トリガが同一の場合はN D R B のアドレスはH'FFA4となり出力トリガが異なる場合はグループ2に対応するN D R B のアドレスはH'FFA6、グループ3に対応するN D R B のアドレスはH'FFA4となります。

## 11.2 各レジスタの説明

### 11.2.1 ポートAデータディレクションレジスタ (PADDR)

PADDRは8ビットのライト専用のレジスタで、ポートAの各端子の入出力方向をビット単位に設定します。

| ビット: | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|      | PA <sub>7</sub> DDR | PA <sub>6</sub> DDR | PA <sub>5</sub> DDR | PA <sub>4</sub> DDR | PA <sub>3</sub> DDR | PA <sub>2</sub> DDR | PA <sub>1</sub> DDR | PA <sub>0</sub> DDR |

| 初期値: | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

R/W: W W .W W W W W W

ポートAデータディレクション7～0

ポートAの各端子の入出力を選択するビットです。

ポートAはTP<sub>7</sub>～TP<sub>0</sub>端子との兼用端子となっています。TPC出力を行う端子に対応するビットは“1”にセットしてください。

PADDRの詳細は、「9.11 ポートA」を参照してください。

### 11.2.2 ポートAデータレジスタ (PADR)

PADRは8ビットのリード/ライト可能なレジスタで、TPC出力を使用する場合、グループ0、1の出力データを格納します。

| ビット: | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|      | PA <sub>7</sub> | PA <sub>6</sub> | PA <sub>5</sub> | PA <sub>4</sub> | PA <sub>3</sub> | PA <sub>2</sub> | PA <sub>1</sub> | PA <sub>0</sub> |

| 初期値: | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

R/W: R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\*

ポートAデータ7～0

TPC出力グループ0、1の出力データを格納するビットです。

【注】\* NDERAにより、TPC出力に設定されたビットはリード専用となります。

PADRの詳細は、「9.11 ポートA」を参照してください。

### 11.2.3 ポートBデータディレクションレジスタ (P B D D R)

P B D D R は 8 ビットのライト専用のレジスタで、ポートBの各端子の入出力方向をビット単位に設定します。

| ビット : | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|-------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|       | PB <sub>7</sub> DDR | PB <sub>6</sub> DDR | PB <sub>5</sub> DDR | PB <sub>4</sub> DDR | PB <sub>3</sub> DDR | PB <sub>2</sub> DDR | PB <sub>1</sub> DDR | PB <sub>0</sub> DDR |

| 初期値 : | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

R/W : W W W W W W W W

ポートBデータディレクション 7～0

ポートBの各端子の入出力を選択するビットです。

ポートBはTP<sub>15</sub>～TP<sub>8</sub>端子との兼用端子となっています。T P C出力を行う端子に対応するビットは“1”にセットしてください。

P B D D R の詳細は、「9.12 ポートB」を参照してください。

### 11.2.4 ポートBデータレジスタ (P B D R)

P B D R は 8 ビットのリード／ライト可能なレジスタで、T P C出力を使用する場合、P B D R はグループ2、3の出力データを格納します。

| ビット : | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|       | PB <sub>7</sub> | PB <sub>6</sub> | PB <sub>5</sub> | PB <sub>4</sub> | PB <sub>3</sub> | PB <sub>2</sub> | PB <sub>1</sub> | PB <sub>0</sub> |

| 初期値 : | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

R/W : R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\*

ポートBデータ 7～0

T P C出力グループ2、3の出力データを格納するビットです。

【注】\* N D E R Bにより、T P C出力に設定されたビットはリード専用となります。

P B D R の詳細は、「9.12 ポートB」を参照してください。

### 11.2.5 ネクストデータレジスタA (N D R A)

N D R Aは8ビットのリード／ライト可能なレジスタで、T P C出力グループ1、0 (T P<sub>7</sub>～T P<sub>0</sub>端子) の次の出力データを格納します。T P C出力を行う場合、T P C Rで指定したI T Uのコンペアマッチが発生したときに、N D R Aの内容がP A D Rの対応するビットに転送されます。

N D R Aのアドレスは、T P C出力グループ0、1の出力トリガを同一に設定した場合と異なるように設定した場合とで異なります。

N D R Aはリセット、またはハードウェアスタンバイモード時にH'00にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

#### (1) T P C出力グループ0、1の出力トリガが同一の場合

T P C出力グループ0、1の出力トリガとなるコンペアマッチを同一にすると、N D R AのアドレスはH'FFA5となります。グループ1、0はそれぞれ上位4ビット、下位4ビットになります。このとき、アドレスH'FFA7はすべてリザーブビットとなります。リザーブビットはリードすると常に“1”が読み出され、ライトは無効です。

##### ① アドレス : H'FFA5

| ビット :                               | 7    | 6    | 5    | 4                                   | 3    | 2    | 1    | 0    |

|-------------------------------------|------|------|------|-------------------------------------|------|------|------|------|

|                                     | NDR7 | NDR6 | NDR5 | NDR4                                | NDR3 | NDR2 | NDR1 | NDR0 |

| 初期値 :                               | 0    | 0    | 0    | 0                                   | 0    | 0    | 0    | 0    |

| R/W :                               | R/W  | R/W  | R/W  | R/W                                 | R/W  | R/W  | R/W  | R/W  |

| ネクストデータ7～4                          |      |      |      | ネクストデータ3～0                          |      |      |      |      |

| T P C出力グループ1の次の<br>出力データを格納するビットです。 |      |      |      | T P C出力グループ0の次の<br>出力データを格納するビットです。 |      |      |      |      |

##### ② アドレス : H'FFA7

| ビット :   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

|         | — | — | — | — | — | — | — | — |

| 初期値 :   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| R/W :   | — | — | — | — | — | — | — | — |

| リザーブビット |   |   |   |   |   |   |   |   |

(2) TPC出力グループ0、1の出力トリガが異なる場合

TPC出力グループ0、1の出力トリガとなるコンペアマッチを別にすると、NDRAの上位4ビット（グループ1）のアドレスはH'FFA5、NDRAの下位4ビット（グループ0）のアドレスはH'FFA7となります。このとき、アドレスH'FFA5のビット3～0、アドレスH'FFA7のビット7～4はリザーブビットとなります。リザーブビットはリードすると常に“1”が読み出され、ライトは無効です。

① アドレス：H'FFA5

| ビット: | 7    | 6    | 5    | 4    | 3 | 2 | 1 | 0 |

|------|------|------|------|------|---|---|---|---|

|      | NDR7 | NDR6 | NDR5 | NDR4 | — | — | — | — |

| 初期値: | 0    | 0    | 0    | 0    | 1 | 1 | 1 | 1 |

| R/W: | R/W  | R/W  | R/W  | R/W  | — | — | — | — |

## ② アドレス: H'FFA7

| ビット: | 7              | 6 | 5 | 4 | 3                 | 2    | 1    | 0    |

|------|----------------|---|---|---|-------------------|------|------|------|

| 初期値: | —              | — | — | — | NDR3              | NDR2 | NDR1 | NDR0 |

| R/W: | —              | — | — | — | R/W               | R/W  | R/W  | R/W  |

|      | <u>リザーブビット</u> |   |   |   | <u>ネクストデータ3~0</u> |      |      |      |

### 11.2.6 ネクストデータレジスタB (NDRB)

NDRBは8ビットのリード/ライト可能なレジスタで、TPC出力グループ3、2(TP<sub>15</sub>~TP<sub>8</sub>端子)の次の出力データを格納します。TPC出力を実行する場合、TPCRで指定したITUのコンペアマッチが発生したときに、NDRBの内容がPBDRの対応するビットに転送されます。NDRBのアドレスは、TPC出力グループ2、3の出力トリガを同一に設定した場合と異なるように設定した場合とで異なります。

NDRBはリセット、またはハードウェアスタンバイモード時にH'00にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

#### (1) TPC出力グループ2、3の出力トリガが同一の場合

TPC出力グループ2、3の出力トリガとなるコンペアマッチを同一にすると、NDRBのアドレスはH'FFA4となります。グループ3、2はそれぞれ下位4ビット、上位4ビットになります。このとき、アドレスH'FFA6はすべてリザーブビットとなります。リザーブビットはリードすると常に“1”が読み出され、ライトは無効です。

##### ① アドレス : H'FFA4

| ビット : | 7                             | 6     | 5     | 4     | 3                             | 2     | 1    | 0    |

|-------|-------------------------------|-------|-------|-------|-------------------------------|-------|------|------|

|       | NDR15                         | NDR14 | NDR13 | NDR12 | NDR11                         | NDR10 | NDR9 | NDR8 |

| 初期値 : | 0                             | 0     | 0     | 0     | 0                             | 0     | 0    | 0    |

| R/W : | R/W                           | R/W   | R/W   | R/W   | R/W                           | R/W   | R/W  | R/W  |

|       | ネクストデータ15~12                  |       |       |       | ネクストデータ11~8                   |       |      |      |

|       | TPC出力グループ3の次の<br>出力データを格納します。 |       |       |       | TPC出力グループ2の次の<br>出力データを格納します。 |       |      |      |

##### ② アドレス : H'FFA6

| ビット :   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

|         | — | — | — | — | — | — | — | — |

| 初期値 :   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| R/W :   | — | — | — | — | — | — | — | — |

| リザーブビット |   |   |   |   |   |   |   |   |

(2) TPC出力グループ2、3の出力トリガが異なる場合

TPC出力グループ2、3の出力トリガとなるコンペアマッチを別にすると、NDRBの上位4ビット（グループ3）のアドレスはH'FFA4、NDRBの下位4ビット（グループ2）のアドレスはH'FFA6となります。このとき、アドレスH'FFA4のビット3～0、アドレスH'FFA6のビット7～4はリザーブビットとなります。リザーブビットはリードすると常に“1”が読み出され、ライトは無効です。

① アドレス：H'FFA4

| ビット： | 7     | 6     | 5     | 4     | 3 | 2 | 1 | 0 |

|------|-------|-------|-------|-------|---|---|---|---|

|      | NDR15 | NDR14 | NDR13 | NDR12 | — | — | — | — |

| 初期値： | 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 |

| R/W： | R/W   | R/W   | R/W   | R/W   | — | — | — | — |

ネクストデータ15～12

リザーブビット

TPC出力グループ3の次の

出力データを格納するビットです。

② アドレス：H'FFA6

| ビット： | 7 | 6 | 5 | 4 | 3     | 2     | 1    | 0    |

|------|---|---|---|---|-------|-------|------|------|

|      | — | — | — | — | NDR11 | NDR10 | NDR9 | NDR8 |

| 初期値： | 1 | 1 | 1 | 1 | 0     | 0     | 0    | 0    |

| R/W： | — | — | — | — | R/W   | R/W   | R/W  | R/W  |

リザーブビット

ネクストデータ11～8

TPC出力グループ2の次の

出力データを格納するビットです。

### 11.2.7 ネクストデータイネーブルレジスタA (N D E R A)

N D E R Aは8ビットのリード／ライト可能なレジスタで、T P C出力グループ1、0 (T P, ~T P<sub>o</sub>端子)の許可／禁止をビット単位で選択します。

| ビット: | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|      | N D E R 7 | N D E R 6 | N D E R 5 | N D E R 4 | N D E R 3 | N D E R 2 | N D E R 1 | N D E R 0 |

| 初期値: | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

| R/W: | R/W |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

|------|-----|-----|-----|-----|-----|-----|-----|-----|

#### ネクストデータイネーブル7～0

T P C出力グループ1、0を許可／禁止を選択するビットです。

N D E R AによりT P C出力が許可されたビットは、T P C Rで選択されたI T Uのコンペアマッチが発生すると、N D R Aの値がP A D Rの当該ビットに自動転送され出力値が更新されます。T P C出力を禁止されているビットについては、N D R AからP A D Rへの転送は行われず出力値も変化しません。

N D E R Aはリセット、またはハードウェアスタンバイモード時にH'00にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

#### ビット7～0：ネクストデータイネーブル7～0 (N D E R 7～N D E R 0)

T P C出力グループ1、0 (T P, ~T P<sub>o</sub>端子)の許可／禁止をビット単位で選択します。

| ビット7～0              | 説明                                                                                          |

|---------------------|---------------------------------------------------------------------------------------------|

| N D E R 7～N D E R 0 |                                                                                             |

| 0                   | T P C出力T P, ~T P <sub>o</sub> を禁止 (N D R 7～N D R 0からP A, ~P A <sub>o</sub> への転送禁止)<br>(初期値) |

| 1                   | T P C出力T P, ~T P <sub>o</sub> を許可 (N D R 7～N D R 0からP A, ~P A <sub>o</sub> への転送許可)          |

### 11.2.8 ネクストデータイネーブルレジスタB (N D E R B)

N D E R B は 8 ビットのリード／ライト可能なレジスタで、T P C 出力グループ 3、2 (T P<sub>1</sub>～T P<sub>8</sub>端子) の許可／禁止をビット単位で選択します。

| ビット : | 7          | 6          | 5          | 4          | 3          | 2          | 1         | 0         |

|-------|------------|------------|------------|------------|------------|------------|-----------|-----------|

|       | N D E R 15 | N D E R 14 | N D E R 13 | N D E R 12 | N D E R 11 | N D E R 10 | N D E R 9 | N D E R 8 |

| 初期値 : | 0          | 0          | 0          | 0          | 0          | 0          | 0         | 0         |

R/W : R/W R/W R/W R/W R/W R/W R/W R/W R/W

#### ネクストデータイネーブル15～8

T P C 出力グループ 3、2 の許可／禁止を

選択するビットです。

N D E R B により T P C 出力が許可されたビットは、T P C R で選択された I T U のコンペアマッチが発生すると、N D R B の値が P B D R の当該ビットに自動転送され出力値が更新されます。T P C 出力を禁止されているビットについては、N D R B から P B D R への転送は行われず出力値も変化しません。

N D E R B はリセット、またはハードウェアスタンバイモード時にH'00にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

#### ビット7～0：ネクストデータイネーブル15～8 (N D E R 15～N D E R 8)

T P C 出力グループ 3、2 (T P<sub>1</sub>～T P<sub>8</sub>端子) の許可／禁止をビット単位で選択します。

| ビット7～0               | 説明                                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------|

| N D E R 15～N D E R 8 |                                                                                                                          |

| 0                    | T P C 出力 T P <sub>1</sub> ～T P <sub>8</sub> を禁止 (N D R 15～N D R 8 から P B <sub>1</sub> ～P B <sub>8</sub> への転送禁止)<br>(初期値) |

| 1                    | T P C 出力 T P <sub>1</sub> ～T P <sub>8</sub> を許可 (N D R 15～N D R 8 から P B <sub>1</sub> ～P B <sub>8</sub> への転送許可)          |

### 11.2.9 TPC出力コントロールレジスタ (TPCR)

TPCRは8ビットのリード／ライト可能なレジスタで、TPC出力の出力トリガ信号をグループ単位で選択します。

| ビット: | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 初期値: | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W: | R/W |

#### グループ0コンペアマッチセレクト1、0

TPC出力グループ0 (TP<sub>3</sub>～TP<sub>0</sub>) の出力トリガとなるコンペアマッチを選択するビットです。

#### グループ1コンペアマッチセレクト1、0

TPC出力グループ1 (TP<sub>7</sub>～TP<sub>4</sub>) の出力トリガとなるコンペアマッチを選択するビットです。

#### グループ2コンペアマッチセレクト1、0

TPC出力グループ2 (TP<sub>11</sub>～TP<sub>8</sub>) の出力トリガとなるコンペアマッチを選択するビットです。

#### グループ3コンペアマッチセレクト1、0

TPC出力グループ3 (TP<sub>15</sub>～TP<sub>12</sub>) の出力トリガとなるコンペアマッチを選択するビットです。

TPCRは、リセットまたはハードウェアスタンバイモード時にH'FFにイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

ビット7、6：グループ3コンペアマッチセレクト1、0 (G3CMS1、G3CMS0)

TPC出力グループ3 (TP<sub>15</sub>～TP<sub>12</sub>端子) の出力トリガとなるコンペアマッチを選択します。

| ビット7   | ビット6   | 説明                                                                                   |

|--------|--------|--------------------------------------------------------------------------------------|

| G3CMS1 | G3CMS0 |                                                                                      |

| 0      | 0      | TPC出力グループ3 (TP <sub>15</sub> ～TP <sub>12</sub> 端子) の出力トリガは、ITUチャネル0のコンペアマッチ          |

|        | 1      | TPC出力グループ3 (TP <sub>15</sub> ～TP <sub>12</sub> 端子) の出力トリガは、ITUチャネル1のコンペアマッチ          |

| 1      | 0      | TPC出力グループ3 (TP <sub>15</sub> ～TP <sub>12</sub> 端子) の出力トリガは、ITUチャネル2のコンペアマッチ          |

|        | 1      | TPC出力グループ3 (TP <sub>15</sub> ～TP <sub>12</sub> 端子) の出力トリガは、ITUチャネル3のコンペアマッチ<br>(初期値) |

ビット5、4：グループ2コンペアマッチセレクト1、0 (G2CMS1、G2CMS0)

TPC出力グループ2 (TP<sub>11</sub>～TP<sub>8</sub>端子) の出力トリガとなるコンペアマッチを選択します。

| ビット5   | ビット4   | 説明                                                                                  |

|--------|--------|-------------------------------------------------------------------------------------|

| G2CMS1 | G2CMS0 |                                                                                     |

| 0      | 0      | TPC出力グループ2 (TP <sub>11</sub> ～TP <sub>8</sub> 端子) の出力トリガは、ITUチャネル0のコンペアマッチ          |

|        | 1      | TPC出力グループ2 (TP <sub>11</sub> ～TP <sub>8</sub> 端子) の出力トリガは、ITUチャネル1のコンペアマッチ          |

| 1      | 0      | TPC出力グループ2 (TP <sub>11</sub> ～TP <sub>8</sub> 端子) の出力トリガは、ITUチャネル2のコンペアマッチ          |

|        | 1      | TPC出力グループ2 (TP <sub>11</sub> ～TP <sub>8</sub> 端子) の出力トリガは、ITUチャネル3のコンペアマッチ<br>(初期値) |

ビット3、2：グループ1コンペアマッチセレクト1、0 (G1 CMS 1、G1 CMS 0)

TPC出力グループ1 (TP<sub>3</sub>～TP<sub>4</sub>端子) の出力トリガとなるコンペアマッチを選択します。

| ビット3     | ビット2     | 説明                                                                                 |

|----------|----------|------------------------------------------------------------------------------------|

| G1 CMS 1 | G1 CMS 0 |                                                                                    |

| 0        | 0        | TPC出力グループ1 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル0のコンペアマッチ          |

|          | 1        | TPC出力グループ1 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル1のコンペアマッチ          |

| 1        | 0        | TPC出力グループ1 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル2のコンペアマッチ          |

|          | 1        | TPC出力グループ1 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル3のコンペアマッチ<br>(初期値) |

ビット1、0：グループ0コンペアマッチセレクト1、0 (G0 CMS 1、G0 CMS 0)

TPC出力グループ0 (TP<sub>3</sub>～TP<sub>4</sub>端子) の出力トリガとなるコンペアマッチを選択します。

| ビット1     | ビット0     | 説明                                                                                 |

|----------|----------|------------------------------------------------------------------------------------|

| G0 CMS 1 | G0 CMS 0 |                                                                                    |

| 0        | 0        | TPC出力グループ0 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル0のコンペアマッチ          |

|          | 1        | TPC出力グループ0 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル1のコンペアマッチ          |

| 1        | 0        | TPC出力グループ0 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル2のコンペアマッチ          |

|          | 1        | TPC出力グループ0 (TP <sub>3</sub> ～TP <sub>4</sub> 端子) の出力トリガは、ITUチャネル3のコンペアマッチ<br>(初期値) |

## 11.2.10 TPC出力モードレジスタ (TPMR)

TPMRは8ビットのリード／ライト可能なレジスタで、TPC出力を通常動作で行うか、ノンオーバラップ動作で行うかをグループ単位で指定します。

| ビット:                                                                    | 7       | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|-------------------------------------------------------------------------|---------|---|---|---|-------|-------|-------|-------|

|                                                                         | —       | — | — | — | G3NOV | G2NOV | G1NOV | G0NOV |

| 初期値:                                                                    | 1       | 1 | 1 | 1 | 0     | 0     | 0     | 0     |

| R/W:                                                                    | —       | — | — | — | R/W   | R/W   | R/W   | R/W   |

|                                                                         | リザーブビット |   |   |   |       |       |       |       |

| <u>グループ3 ノンオーバラップ</u>                                                   |         |   |   |   |       |       |       |       |

| TPC出力グループ3 (TP <sub>13</sub> ～TP <sub>12</sub> ) のノンオーバラップ動作を設定するビットです。 |         |   |   |   |       |       |       |       |

| <u>グループ2 ノンオーバラップ</u>                                                   |         |   |   |   |       |       |       |       |

| TPC出力グループ2 (TP <sub>11</sub> ～TP <sub>8</sub> ) のノンオーバラップ動作を設定するビットです。  |         |   |   |   |       |       |       |       |

| <u>グループ1 ノンオーバラップ</u>                                                   |         |   |   |   |       |       |       |       |

| TPC出力グループ1 (TP <sub>7</sub> ～TP <sub>4</sub> ) のノンオーバラップ動作を設定するビットです。   |         |   |   |   |       |       |       |       |

| <u>グループ0 ノンオーバラップ</u>                                                   |         |   |   |   |       |       |       |       |

| TPC出力グループ0 (TP <sub>3</sub> ～TP <sub>0</sub> ) のノンオーバラップ動作を設定するビットです。   |         |   |   |   |       |       |       |       |

ノンオーバラップ動作のTPC出力は、出力トリガとなるITUのGRBに出力波形の周期を、またGRAにノンオーバラップ期間を設定し、コンペアマッチA、Bで出力値を変化させます。

詳細は、「11.3.4 TPC出力ノンオーバラップ動作」を参照してください。

TPMRはリセット、またはハードウェアスタンバイモード時にH'F0にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

### ビット7～4：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

### ビット3：グループ3ノンオーバラップ (G3NOV)

TPC出力グループ3 (TP<sub>11</sub>～TP<sub>12</sub>端子) を通常動作させるか、ノンオーバラップ動作させるかを選択します。

| ビット3  | 説明                                                                   |

|-------|----------------------------------------------------------------------|

| G3NOV |                                                                      |

| 0     | TPC出力グループ3は、通常動作（選択されたITUのコンペアマッチAで出力値を更新します。）<br>(初期値)              |

| 1     | TPC出力グループ3は、ノンオーバラップ動作（選択されたITUのコンペアマッチA、Bにより、1出力、0出力を独立に行うことができます。） |

### ビット2：グループ2ノンオーバラップ (G2NOV)

TPC出力グループ2 (TP<sub>13</sub>～TP<sub>14</sub>端子) を通常動作させるか、ノンオーバラップ動作させるかを選択します。

| ビット2  | 説明                                                                   |

|-------|----------------------------------------------------------------------|

| G2NOV |                                                                      |

| 0     | TPC出力グループ2は、通常動作（選択されたITUのコンペアマッチAで出力値を更新します。）<br>(初期値)              |

| 1     | TPC出力グループ2は、ノンオーバラップ動作（選択されたITUのコンペアマッチA、Bにより、1出力、0出力を独立に行うことができます。） |

### ビット1：グループ1ノンオーバラップ (G1NOV)

TPC出力グループ1 (TP<sub>15</sub>～TP<sub>16</sub>端子) を通常動作させるか、ノンオーバラップ動作させるかを選択します。

| ビット1  | 説明                                                                   |

|-------|----------------------------------------------------------------------|

| G1NOV |                                                                      |

| 0     | TPC出力グループ1は、通常動作（選択されたITUのコンペアマッチAで出力値を更新します。）<br>(初期値)              |

| 1     | TPC出力グループ1は、ノンオーバラップ動作（選択されたITUのコンペアマッチA、Bにより、1出力、0出力を独立に行うことができます。） |

ビット0：グループ0ノンオーバラップ(G0NOV)

TPC出力グループ0(TP<sub>3</sub>～TP<sub>6</sub>端子)を通常動作させるか、ノンオーバラップ動作させるかを選択します。

| ビット0  | 説明                                                                   |

|-------|----------------------------------------------------------------------|

| G0NOV |                                                                      |

| 0     | TPC出力グループ0は、通常動作（選択されたITUのコンペアマッチAで出力値を更新します。）<br>(初期値)              |

| 1     | TPC出力グループ0は、ノンオーバラップ動作（選択されたITUのコンペアマッチA、Bにより、1出力、0出力を独立に行うことができます。） |

## 11.3 動作説明

### 11.3.1 概要

TPC出力は、PADDR、PBDDRとNDERA、NDRBの対応するビットをそれぞれ“1”にセットすることにより許可状態となります。この状態では、対応するPADR、PBDRの内容が出力されます。

その後、TPCRで指定したコンペアマッチが発生すると、ビットに対応するNDR AおよびNDR Bの内容がそれぞれPADRおよびPBDRに転送され、出力値が更新されます。

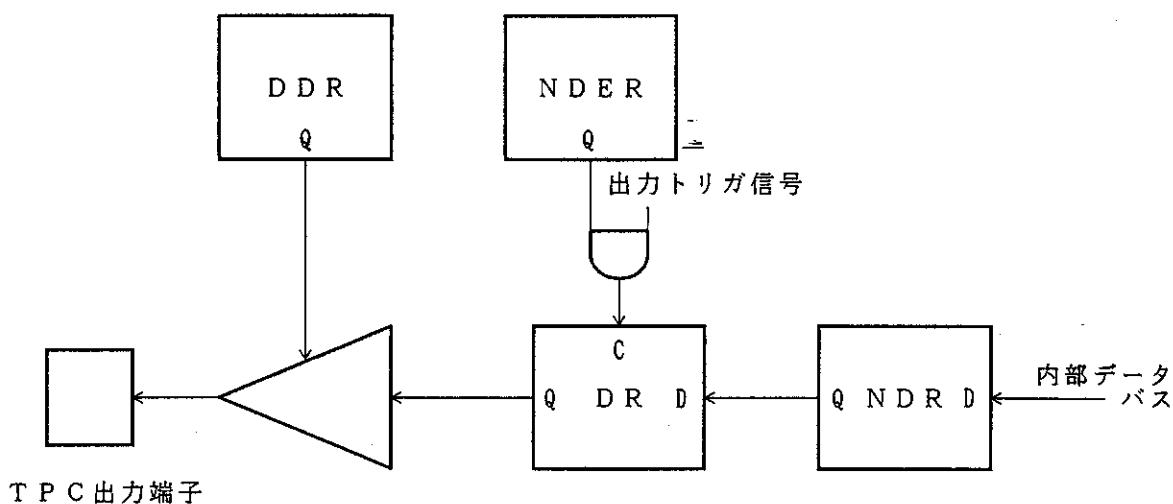

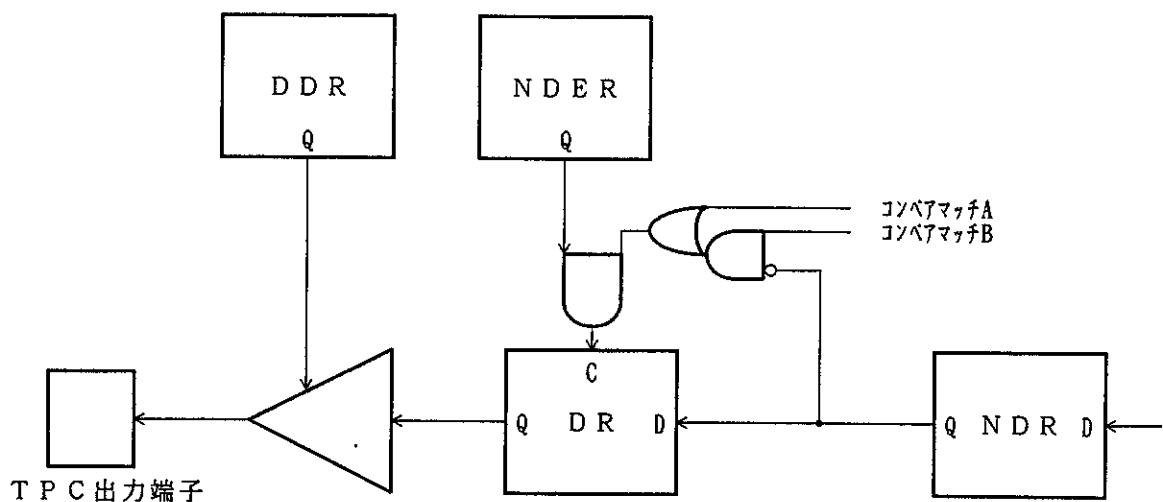

TPC出力動作を図11.2に示します。また、TPC動作条件を表11.3に示します。

図11.2 TPC出力動作

表11.3 TPC動作条件

| NDER | DDR | 端子機能                                            |

|------|-----|-------------------------------------------------|

| 0    | 0   | 入力ポート                                           |

|      | 1   | 出力ポート                                           |

| 1    | 0   | 入力ポート（ただし、コンペアマッチ時にNDRからDRの転送を行い、DRへのライトはできません） |

|      | 1   | TPCパルス出力                                        |

次のコンペアマッチが発生するまでにNDR AおよびNDR Bに出力データを書き込むことにより、コンペアマッチごとに最大16ビットのデータを順次出力することができます。

ノンオーバラップ動作については、「11.3.4 TPC出力ノンオーバラップ動作」を参照してください。

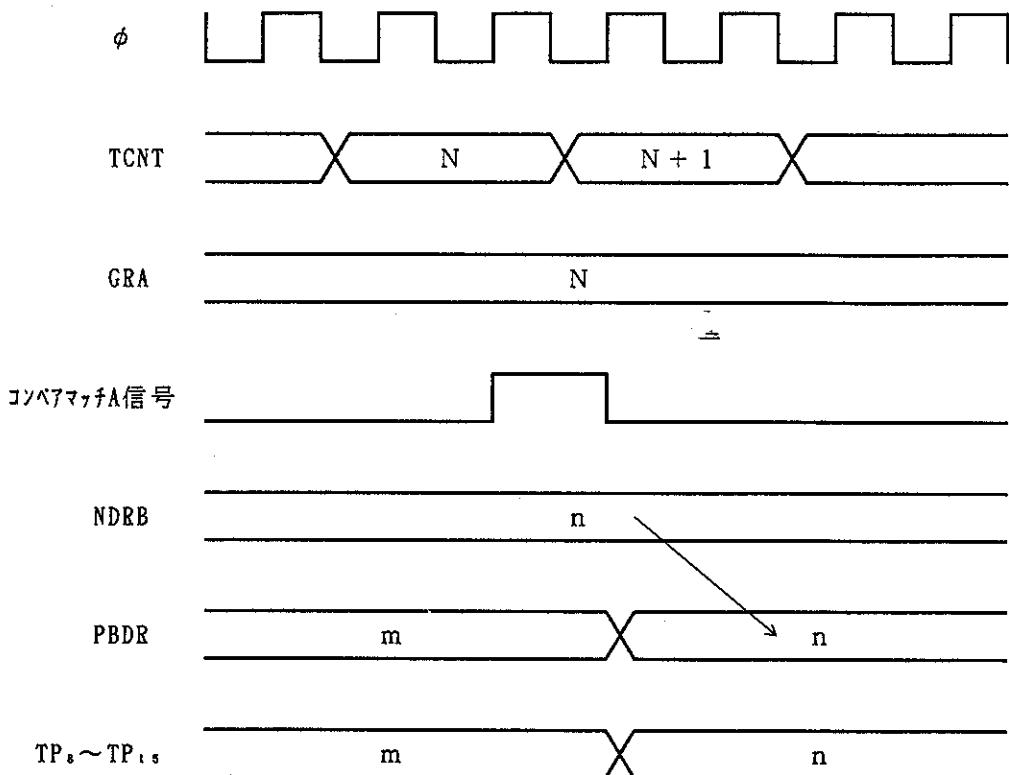

### 11.3.2 出力タイミング

TPC出力許可状態で指定されたコンペアマッチが発生すると、NDR A/NDR Bの内容がPADR/PBDRに転送され、出力されます。

このタイミングを図11.3に示します。

コンペアマッチAにより、グループ2、3で通常出力を行った場合の例です。

図11.3 NDRの内容が転送・出力されるタイミング（例）

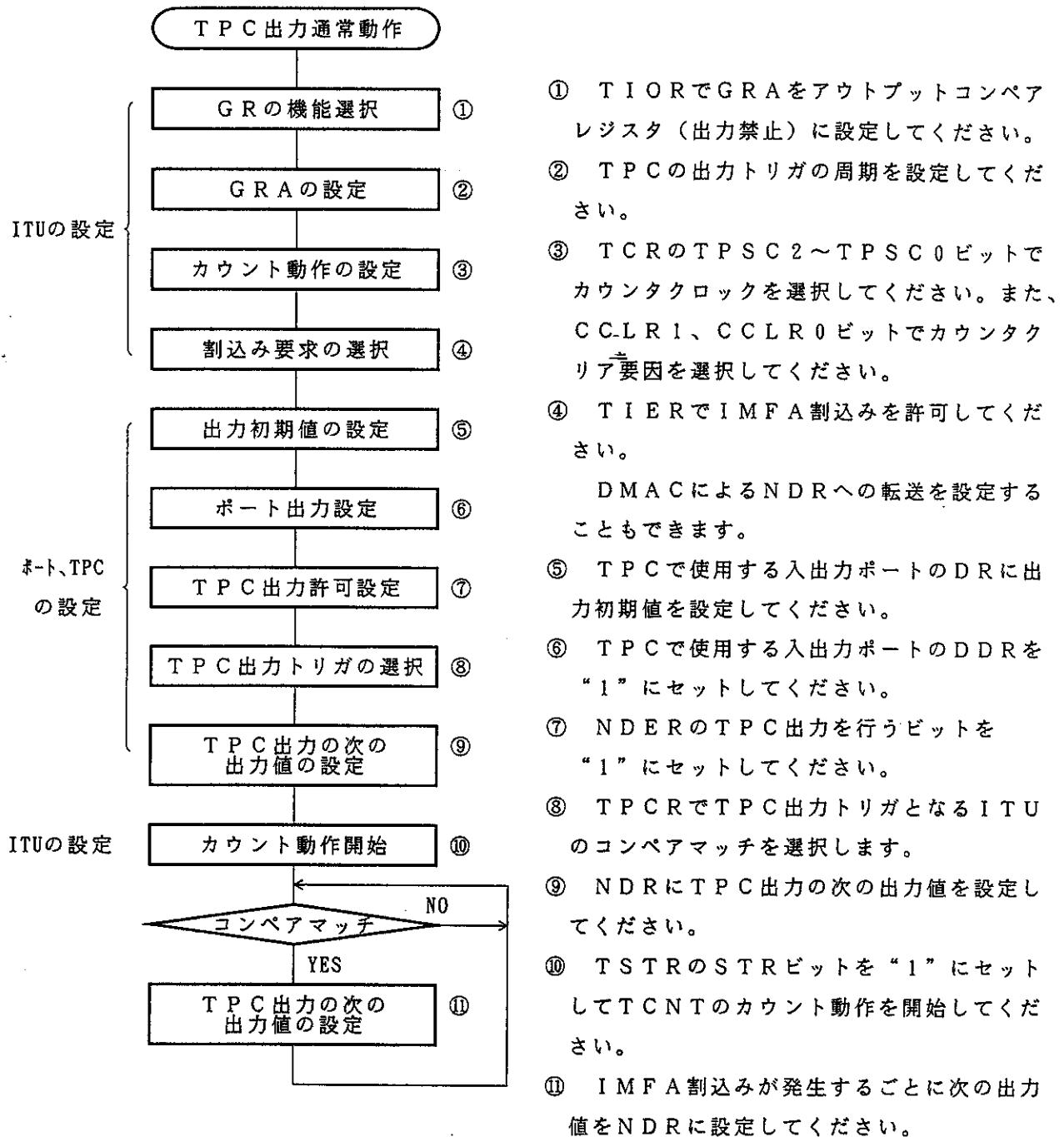

### 11.3.3 TPC 出力通常動作

#### (1) TPC 出力通常動作の設定手順例

TPC 出力通常動作の設定手順例を図11.4に示します。

図11.4 TPC 出力通常動作の設定手順例

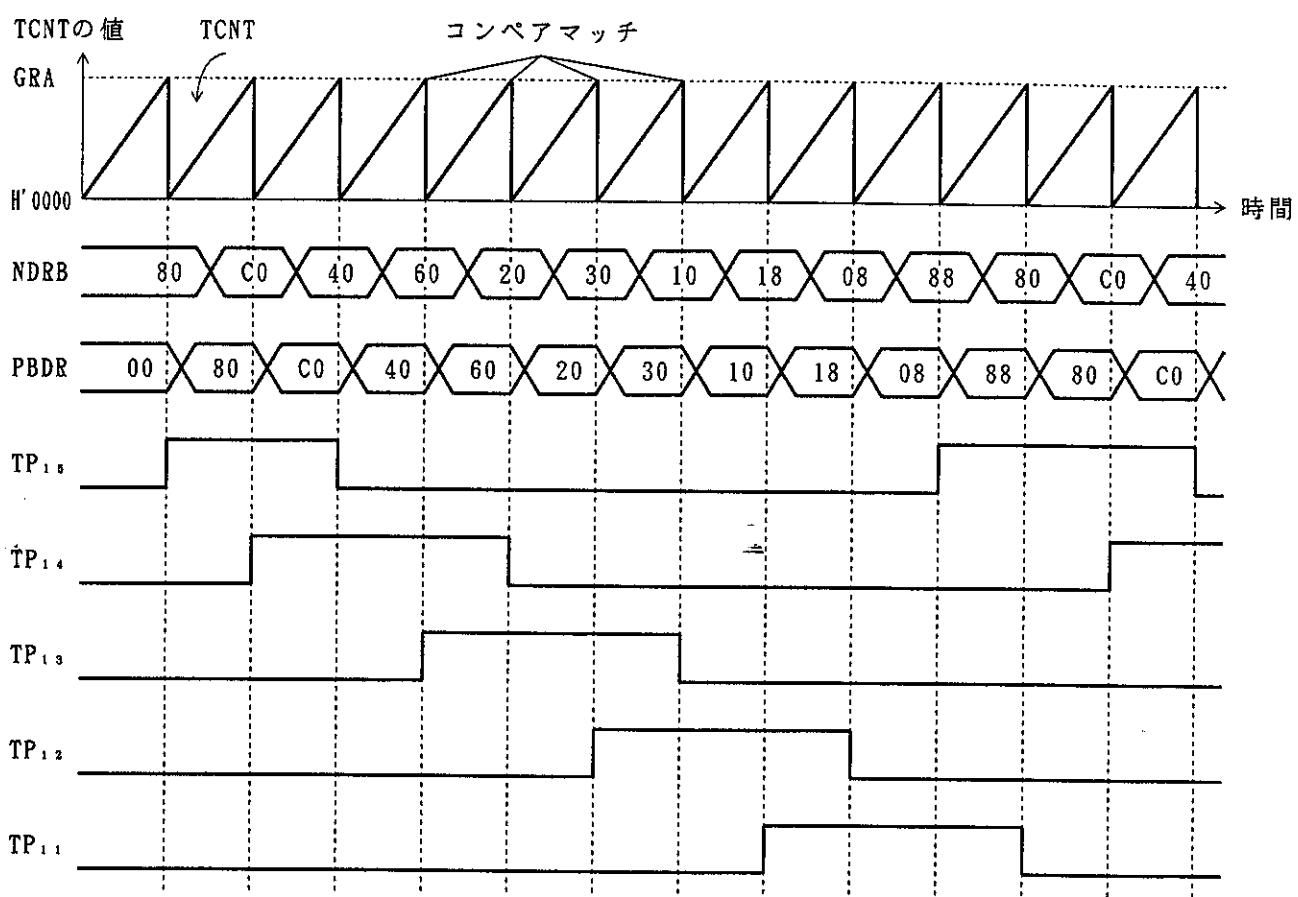

## (2) TPC 出力通常動作例 (5 相パルス出力例)

TPC 出力を使用して一定周期で 5 相パルスを出力させた例を図11.5に示します。

- ① 出力トリガとする ITU の GRA をアウトプットコンペアレジスタに設定します。

GRA には周期を設定し、コンペアマッチ A によるカウンタクリアを選択します。また、TIER の IMIEA ビットを “1” にセットして、コンペアマッチ A 割込みを許可します。

- ② PBDDR と NDRB に H'F8 をライトし、TPCR の G3CMS1、G3CMS0 ビットおよび G2CMS1、G2CMS0 ビットにより出力トリガを①で選択した ITU のコンペアマッチに設定します。NDRB に出力データ H'80 をライトします。

- ③ ITU 当該チャネルの動作を開始しコンペアマッチ A が発生すると、NDRB の内容が PBDR に転送され出力されます。

コンペアマッチ / インプットキャプチャ A (IMFA) 割込み処理で NDRB に次の出力データ H'C0 をライトします。

- ④ 以後、IMFA 割込みで順次 H'40、H'60、H'20、H'30、H'10、H'18、H'08、H'88…をライトすることで、5 相の 1 - 2 相パルス出力を行うことができます。

コンペアマッチで DMA C を起動するように設定すれば、CPU の負荷なくパルス出力を行うことができます。

図11.5 TPC 出力通常動作例 (5 相パルス出力例)

### 11.3.4 TPC出力ノンオーバラップ動作

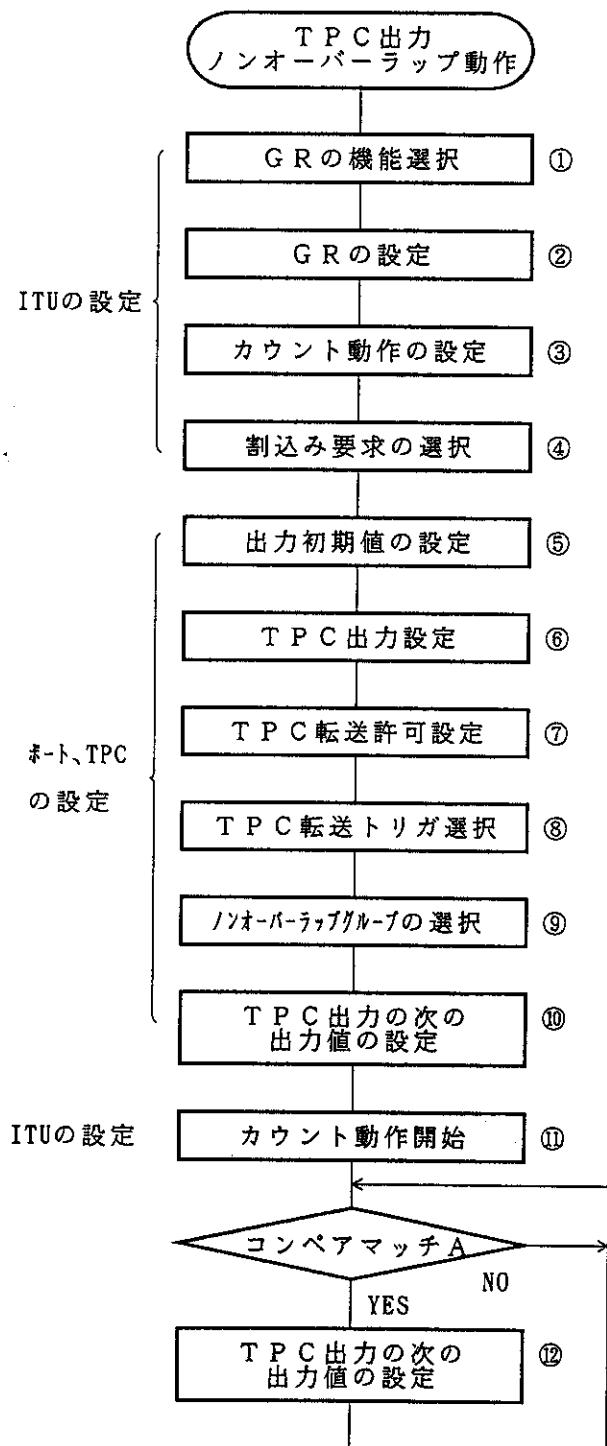

#### (1) TPC出力ノンオーバラップ動作の設定手順例

TPC出力ノンオーバラップ動作の設定手順例を図11.6に示します。

- ① T I O R で G R A 、 G R B をアウトプットコンペアレジスタ（出力禁止）に選択してください。

- ② G R B に T P C 出力トリガの周期を、 G R A にはノンオーバラップ期間をそれぞれ設定してください。

- ③ T C R の T P S C 2 ~ T P S C 0 ビットでカウンタロックを選択してください。また、 C C L R 1 、 C C L R 0 ビットでカウンタクリア要因を選択してください。

- ④ T I E R で I M F A 割込みを許可してください。

D M A C による N D R への転送を設定することもできます。

- ⑤ T P C で使用する入出力ポートの D R に出力初期値を設定してください。

- ⑥ T P C で使用する入出力ポートの D D R を“1”にセットしてください。

- ⑦ N D E R の T P C 出力を行うビットを“1”にセットしてください。

- ⑧ T P C R で T P C 出力トリガとなる I T U のコンペアマッチを選択します。

- ⑨ T P M R でノンオーバラップ動作を行うグループを選択します。

- ⑩ N D R に T P C 出力の次の出力値を設定してください。

- ⑪ T S T R の S T R ビットを“1”にセットして T C N T のカウント動作を開始してください。

- ⑫ I M F A 割込みが発生するごとに次の出力値を N D R に設定してください。

図11.6 TPC出力ノンオーバラップ動作の設定手順例

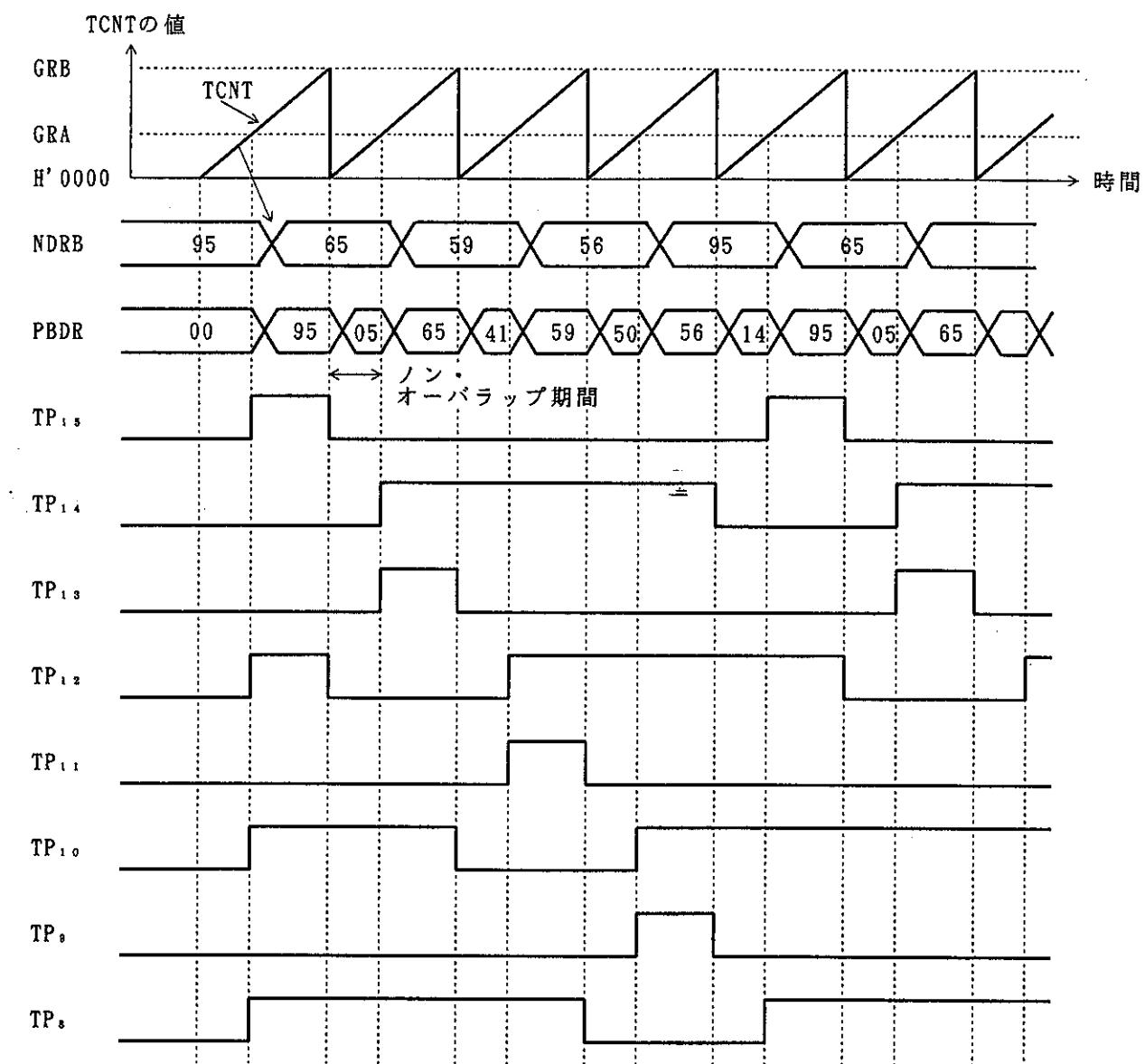

(2) TPC出力ノンオーバラップ動作例 (4相の相補ノンオーバラップ出力例)

TPC出力を使用して4相の相補ノンオーバラップのパルスを出力させた例を図11.7に示します。

図11.7 TPC出力ノンオーバラップ動作例 (4相の相補ノンオーバラップ出力例)

以下に動作例について説明します。

- ① 出力トリガとするITUのGRA、GRBをアウトプットコンペアレジスタに設定します。GRBには周期、GRAにはノンオーバラップ期間を設定し、コンペアマッチBによるカウンタクリアを選択します。また、TIERのIMIEAビットを”1”にセットして、IMFA割込みを許可します。

- ② PBDDRとNDRBにH'FFをライトし、TPCRのG3CMS1、G3CMS0ビットおよびG2CMS1、G2CMS0ビットにより出力トリガを①で選択したITUのコンペアマッチに設定します。

TPMRのG3NOV、G2NOVビットをそれぞれ“1”にセットして、ノンオーバラップ動作を設定します。NDRBに出力データH'95をライトします。

③ ITU当該チャネルの動作を開始すると、GRBのコンペアマッチで1出力→0出力の変化、GRAのコンペアマッチで0出力→1出力の変化を行います（0出力→1出力の変化はGRAの設定値分遅延することになります）。

IMFA割込み処理でNDRBに次回の出力データH'65をライトします。

④ 以後、IMFA割込みで順次H'59、H'56、H'95…をライトすることで、4相の相補ノンオーバラップ出力を発生することができます。

コンペアマッチでDMACを起動するように設定すれば、CPUの負荷なくパルス出力を行うことができます。

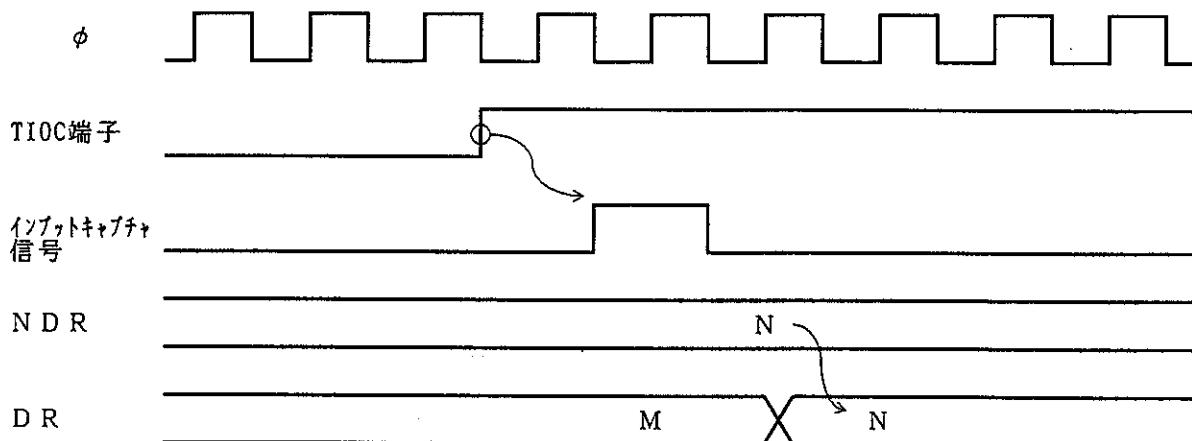

### 11.3.5 インプットキャプチャによるTPC出力

TPC出力は、ITUのコンペアマッチだけではなく、インプットキャプチャによっても可能です。

TPCRによって選択されたITUのGRAがインプットキャプチャレジスタとして機能しているとき、インプットキャプチャ信号によりTPC出力を行います。

このタイミングを図11.8に示します。

図11.8 インプットキャプチャによるTPC出力例

#### 11.4 使用上の注意

#### 11.4.1 TPC出力端子の動作

TP<sub>0</sub>～TP<sub>15</sub>はITU、DMA、アドレスバスなどの端子と兼用になっています。これらの端子は、ITU、DMA、アドレスバスが output許可状態になっているときには、TPC出力を行うことができません。ただし、NDRからDRへの転送は、端子の状態にかかわらず常にを行うことができます。

端子機能の変更は、出力トリガが発生しない状態で行ってください。

#### 11.4.2 ノンオーバラップ動作時の注意

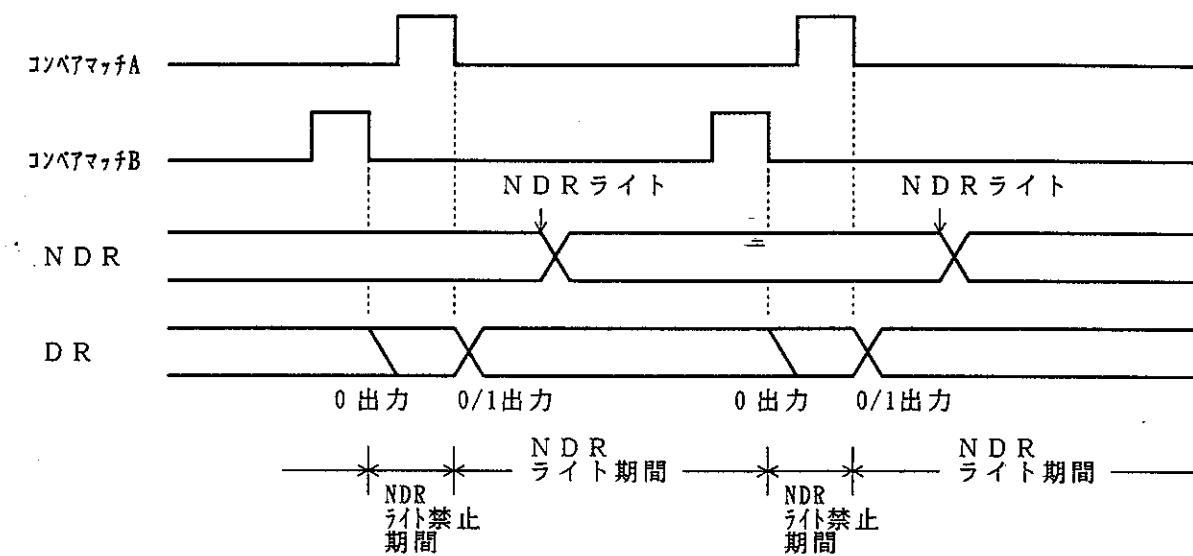

ノンオーバラップ動作時のNDRからDRの転送は以下のようになっています。

- (1) コンペアマッチAではNDRの内容を常にDRへ転送します。

- (2) コンペアマッチBではNDRの転送するビットの内容が“0”的きのみ転送を行います。“1”的きは転送を行いません。

ノンオーバラップ時の TPC 出力動作を図 11.9 に示します。

図11.9 TPC出力ノンオーバラップ動作

したがって、コンペアマッチBを、コンペアマッチAよりも先に発生させることにより、“0”データの転送を“1”データの転送に先だって行うことが可能です。

この場合、コンペアマッチBが発生した後、コンペアマッチAが発生するまで（ノンオーバラップ期間）の間、NDRの内容を変更しないようにしてください。

これはIMFA割込みの割込み処理ルーチンでNDRに次のデータをライトすることによって実現できます。また、IMFA割込みでDMACを起動することもできます。ただし、このライトは次のコンペアマッチBが発生する前に行ってください。

このタイミングを図11.10に示します。

図11.10 ノンオーバラップ動作とNDRライトタイミング