# 14. スマートカード インターフェース

## 第14章 目次

|                              |     |

|------------------------------|-----|

| 14.1 概要                      | 547 |

| 14.1.1 特長                    | 547 |

| 14.1.2 ブロック図                 | 548 |

| 14.1.3 端子構成                  | 549 |

| 14.1.4 レジスタ構成                | 549 |

| 14.2 各レジスタの説明                | 550 |

| 14.2.1 スマートカードモードレジスタ (SCMR) | 550 |

| 14.2.2 シリアルステータスレジスタ (SSR)   | 552 |

| 14.2.3 シリアルモードレジスタ (SMR)     | 553 |

| 14.2.4 シリアルコントロールレジスタ (SCR)  | 554 |

| 14.3 動作説明                    | 556 |

| 14.3.1 概要                    | 556 |

| 14.3.2 端子接続                  | 556 |

| 14.3.3 データフォーマット             | 557 |

| 14.3.4 レジスタ設定                | 558 |

| 14.3.5 クロック                  | 560 |

| 14.3.6 データの送信／受信動作           | 561 |

| 14.4 使用上の注意                  | 569 |

## 14.1 概要

S C I 0 は、シリアルコミュニケーションインターフェースの拡張機能として、I S O / I E C 7 8 1 6 - 3 (Identification Card) に準拠した I C カード（スマートカード）インターフェースをサポートしています。

通常のシリアルコミュニケーションインターフェースとスマートカードインターフェースの切り替えはレジスタの設定で行います。

### 14.1.1 特長

H 8 / 3 0 4 8 がサポートするスマートカードインターフェースには次の特長があります。

#### ■調歩同期式モード

- ・データ長：8ビット

- ・パリティビットの生成およびチェック

- ・受信モードにおけるエラーシグナル（パリティエラー）の送出

- ・送信モードにおけるエラーシグナルの検出とデータの自動再送信

- ・ダイレクトコンベンション／インバースコンベンションの両方をサポート

#### ■内蔵ボーレートジェネレータにより任意のビットレートを選択可能

#### ■3種類の割込み要因

送信データエンプティ、受信データフル、送受信エラーの3種類の割込み要因があり、それぞれ独立に要求することができます。また、送信データエンプティー割込みと受信データフル割込みによりDMAコントローラ（D M A C）を起動させてデータの転送を行うことができます。

#### 14.1.2 ブロック図

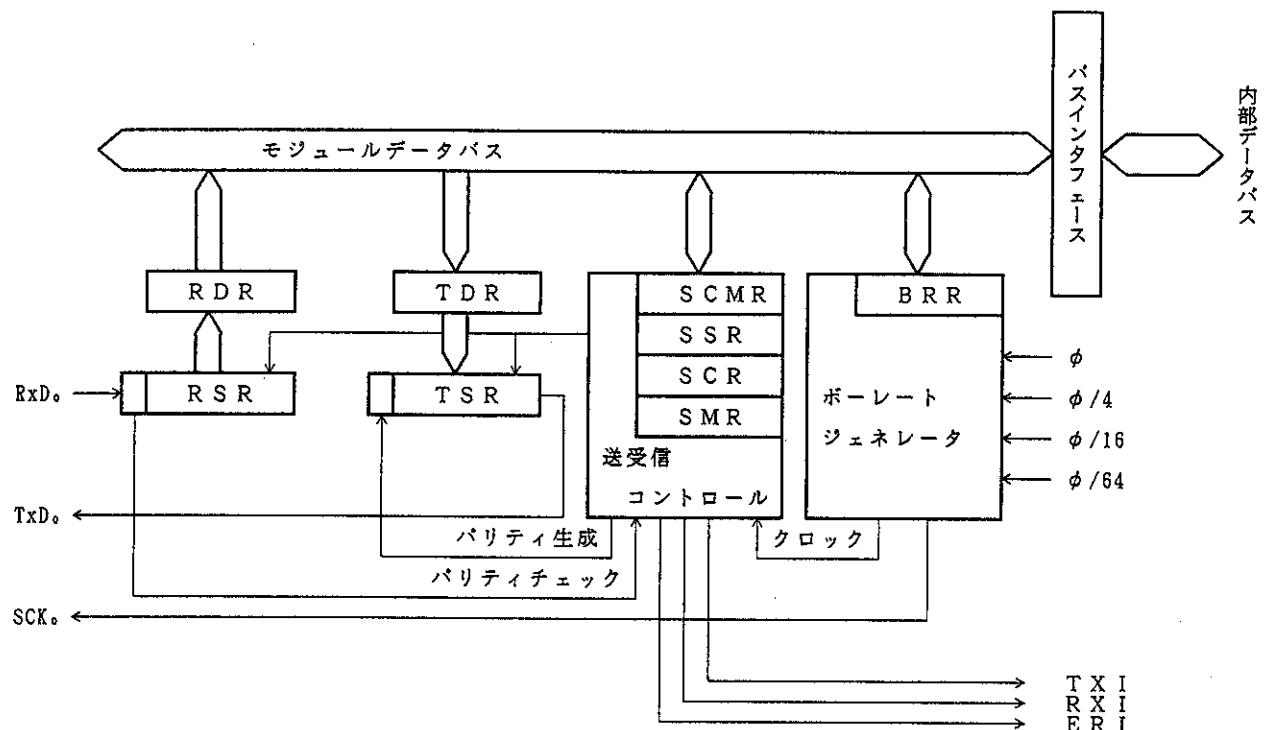

図14.1にスマートカードインターフェースのブロック図を示します。

#### 《記号説明》

- SCMR** : スマートカードモードレジスタ

- RSR** : レシーブシフトレジスタ

- RDR** : レシーブデータレジスタ

- TSR** : トランスマットシフトレジスタ

- TDR** : トランスマットデータレジスタ

- SMR** : シリアルモードレジスタ

- SCR** : シリアルコントロールレジスタ

- SSR** : シリアルステータスレジスタ

- BRR** : ビットレートレジスタ

図14.1 スマートカードインターフェース

### 14.1.3 端子構成

スマートカードインターフェースの端子構成を表14.1に示します。

表14.1 端子構成

| 名 称          | 略 称              | 入出力 | 機 能     |

|--------------|------------------|-----|---------|

| シリアルクロック端子   | SCK <sub>o</sub> | 出力  | クロック出力  |

| レシーブデータ端子    | RxD <sub>o</sub> | 入力  | 受信データ入力 |

| トランスマットデータ端子 | TxD <sub>o</sub> | 出力  | 送信データ出力 |

### 14.1.4 レジスタ構成

スマートカードインターフェースで使用するレジスタ構成を表14.2に示します。BRR、TDR、RDRについては、通常のSCIの機能と同様ですので、「第13章 シリアルコミュニケーションインターフェース」のレジスタの説明を参照してください。

表14.2 レジスタ構成

| アドレス <sup>*1</sup> | 名 称            | 略 称    | R/W                 | 初期値  |

|--------------------|----------------|--------|---------------------|------|

| H'FFB0             | シリアルモードレジスタ    | S MR   | R/W                 | H'00 |

| H'FFB1             | ビットレートレジスタ     | B RR   | R/W                 | H'FF |

| H'FFB2             | シリアルコントロールレジスタ | S CR   | R/W                 | H'00 |

| H'FFB3             | トランスマットデータレジスタ | T DR   | R/W                 | H'FF |

| H'FFB4             | シリアルステータスレジスタ  | S SR   | R/(W) <sup>*2</sup> | H'84 |

| H'FFB5             | レシーブデータレジスタ    | R DR   | R                   | H'00 |

| H'FFB6             | スマートカードモードレジスタ | S CM R | R/W                 | H'F2 |

【注】<sup>\*1</sup> アドレスの下位16ビットを示しています。

<sup>\*2</sup> フラグをクリアするための“0”ライトのみ可能です。

## 14.2 各レジスタの説明

スマートカードインターフェースで追加されるレジスタおよび機能が変更されるビットについて説明します。

### 14.2.1 スマートカードモードレジスタ (SCMR)

SCMRは、8ビットのリード／ライト可能なレジスタで、スマートカードインターフェースの機能の選択を行います。

| ビット                                                     | 7 | 6 | 5 | 4                                                                        | 3   | 2   | 1 | 0                                                                                 |  |

|---------------------------------------------------------|---|---|---|--------------------------------------------------------------------------|-----|-----|---|-----------------------------------------------------------------------------------|--|

| 初期値                                                     | 1 | 1 | 1 | 1                                                                        | 0   | 0   | 1 | 0                                                                                 |  |

| R/W                                                     | — | — | — | —                                                                        | R/W | R/W | — | R/W                                                                               |  |

| <u>リザーブビット</u>                                          |   |   |   | <u>リザーブビット</u>                                                           |     |     |   | スマートカード<br>インターフェース<br>モードセレクト<br>スマートカード<br>インターフェース<br>機能を許可／禁<br>止するビットで<br>す。 |  |

| <u>スマートカードデータインパート</u><br>データのロジックレベルの反転を<br>指定するビットです。 |   |   |   | <u>スマートカードデータトランസファディレ<br/>クション</u><br>シリアル／パラレル変換のフォーマットを<br>選択するビットです。 |     |     |   |                                                                                   |  |

SCMRは、リセットまたはスタンバイモード時にH'F2にイニシャライズされます。

#### ビット7～4：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット3：スマートカードデータトランസファディレクション (SDIR)

シリアル／パラレル変換のフォーマットを選択します。

| ビット3 | 説明                                            |       |

|------|-----------------------------------------------|-------|

| SDIR |                                               |       |

| 0    | TDRの内容をLSBファーストで送信<br>受信データをLSBファーストとしてRDRに格納 | (初期値) |

| 1    | TDRの内容をMSBファーストで送信<br>受信データをMSBファーストとしてRDRに格納 |       |

## ビット2：スマートカードデータインパート（SINV）

データのロジックレベルの反転を指定します。この機能は、ビット3の機能を組合せインバースコンベンションカードとの送受信に使用します。SINVは、パリティビットのロジックレベルには影響しません。パリティに関する設定方法については、「14.3.4 レジスタ設定」を参照してください。

| ビット2 | 説明                                         |

|------|--------------------------------------------|

| SINV | TDRの内容をそのまま送信<br>受信データをそのままRDRに格納<br>（初期値） |

| 1    | TDRの内容を反転してデータを送信<br>受信データを反転してRDRに格納      |

## ビット1：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

## ビット0：スマートカードインターフェースモードセレクト（SMIF）

スマートカードインターフェース機能をイネーブルにするビットです。

| ビット0 | 説明                            |

|------|-------------------------------|

| SMIF | スマートカードインターフェース機能を禁止<br>（初期値） |

| 1    | スマートカードインターフェース機能を許可          |

#### 14.2.2 シリアルステータスレジスタ (S S R)

スマートカードインターフェースモードにおいては、S S Rのビット4の機能が変更されます。また、これに関連してビット2のT E N Dのセット条件が変更になります。

| ビット | 7                   | 6                   | 5                   | 4                   | 3                   | 2    | 1   | 0    |

|-----|---------------------|---------------------|---------------------|---------------------|---------------------|------|-----|------|

|     | TDRE                | RDRF                | ORER                | ERS                 | PER                 | TEND | MPB | MPBT |

| 初期値 | 1                   | 0                   | 0                   | 0                   | 0                   | 1    | 0   | 0    |

| R/W | R/(W)* <sup>1</sup> | R    | R   | R/W  |

|

トランスマットエンド

送信終了を示すフラグです。

|

エラーシグナルステータス (E R S)

エラーシグナルが送出されたことを示すフラグです。

【注】\*<sup>1</sup> フラグをクリアするための“0”ライトのみ可能です。

ビット7～5：通常のS C Iと同様の動作をします。詳細は「第13章 シリアルコミュニケーションインターフェース」を参照してください。

#### ビット4：エラーシグナルステータス (E R S)

スマートカードインターフェースモードでは、送信時に受信側から送り返されるエラーシグナルのステータスを示します。なお、スマートカードインターフェースではフレーミングエラーは検出しません。

| ビット4<br>E R S | 説明                                                                                                   |

|---------------|------------------------------------------------------------------------------------------------------|

| 0             | 正常に受信され、エラーシグナルが無いことを表示<br>(クリア条件)<br>(1) リセット、またはスタンバイモード時<br>(2) E R S = “1”の状態をリードした後、“0”をライトしたとき |

| 1             | 受信側からパリティエラーの検出を示すエラーシグナルが送出されたことを表示<br>(セット条件)<br>エラーシグナル“Low”をサンプリングしたとき                           |

【注】 S C RのT Eビットを“0”にクリアしても、E R Sフラグは影響を受けず以前の状態を保持します。

ビット3～0：通常のSCIと同様の動作をします。詳細は「第13章 シリアルコミュニケーションインターフェース」を参照してください。

ただし、ビット2のトランスマットエンド（TEND）のセット条件は次のようになります。

| ビット2<br>TEND | 説明                                                                                                                                                          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | 送信中であることを表示<br>(クリア条件)<br>(1) TDR = “1”の状態をリードした後、TDRフラグに“0”をライトしたとき<br>(2) DMAでTDRへデータをライトしたとき                                                             |

| 1            | 送信を終了したことを表示<br>(セット条件)<br>(1) リセット、またはスタンバイモード時<br>(2) SCRのTEビットが“0”かつFER/ERSビットが“0”的とき<br>(3) 1バイトのシリアルキャラクタ送信後、2.5etu後にTDR = “1”かつFER/ERS = “0”(正常送信)のとき |

【注】etu (Elementary Time Unit: 1ビットの転送期間の略)

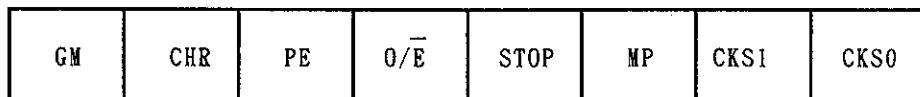

#### 14.2.3 シリアルモードレジスタ (SMR)

スマートカードインターフェースモードにおいては、SMRのビット7の機能が変更されます。また、これに関連してシリアルコントロールレジスタ (SCR) のビット1およびビット0の機能も変更されます。ただし、フラッシュメモリ版にはこの機能はありません。

ビット : 7 6 5 4 3 2 1 0

初期値 : 0 0 0 0 0 0 0 0

R/W : R/W R/W R/W R/W R/W R/W R/W R/W

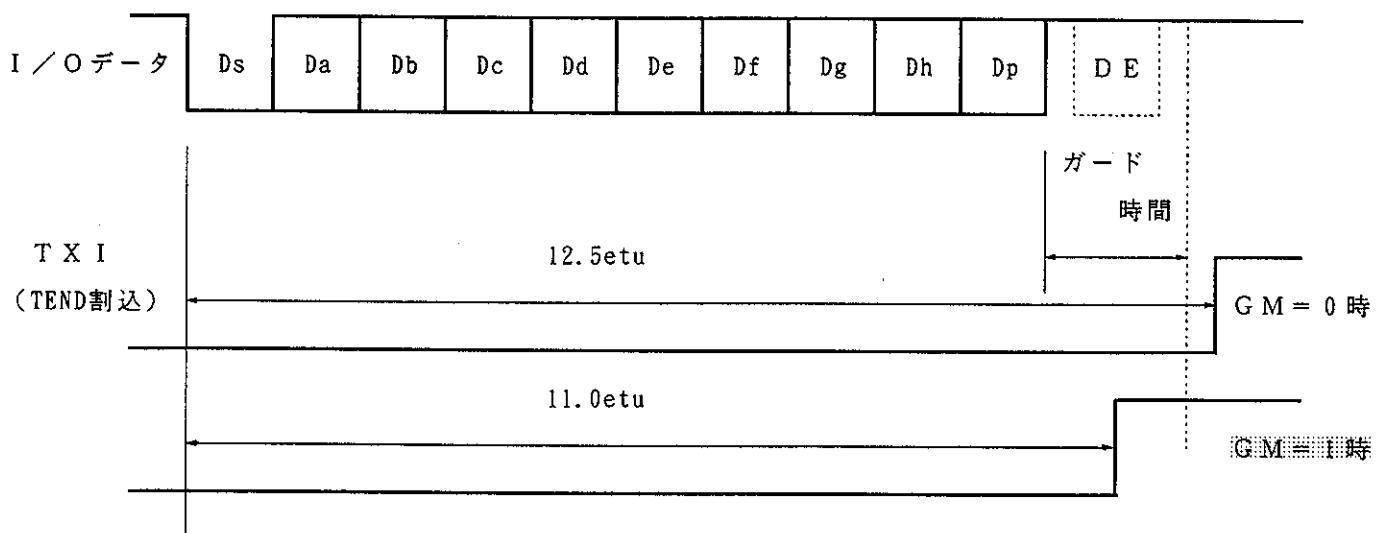

##### ビット7 : GSMモード (GM)

通常のスマートカードインターフェース時は0に設定します。GSMモードは、本ビットを1に設定し、送信完了を示すTENDフラグのセットタイミングの前倒しと、クロック出力の制御モードの追加を行います。クロック出力の制御モードの追加内容は、シリアルコントロールレジスタ (SCR) のビット1およびビット0で指定します。

| ビット 7 | 説明                                                                                                                                     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| G M   |                                                                                                                                        |

| 0     | 通常のスマートカードインターフェースモードの動作<br>(1) T E N D フラグは開始ビットの先頭から12.5etu のタイミングで発生<br>(2) クロック出力のON／OFF 制御のみ<br>(初期値)                             |

| 1     | G S Mモードのスマートカードインターフェースモードの動作<br>(1) T E N D フラグは開始ビットの先頭から11.0etu のタイミングで発生<br>(2) クロック出力のON／OFF、およびH i g h／L o w 固定制御<br>(設定はS C R) |

#### ビット 6～0：

通常のS C Iと同様の動作をします。詳細は「13.2.5 シリアルモードレジスタ(S M R)」を参照してください。

#### 14.2.4 シリアルコントロールレジスタ(S C R)

スマートカードインターフェースモードにおいては、S C Rのビット1、0の機能が変更されます。ただし、フラッシュメモリ版にはこの機能はありません。

ビット : 7 6 5 4 3 2 1 0

初期値 : 0 0 0 0 0 0 0 0

R/W : R/W R/W R/W R/W R/W R/W R/W R/W

#### ビット7～2：

通常のS C Iと同様の動作をします。詳細は「13.2.6 シリアルコントロールレジスタ(S C R)」を参照してください。

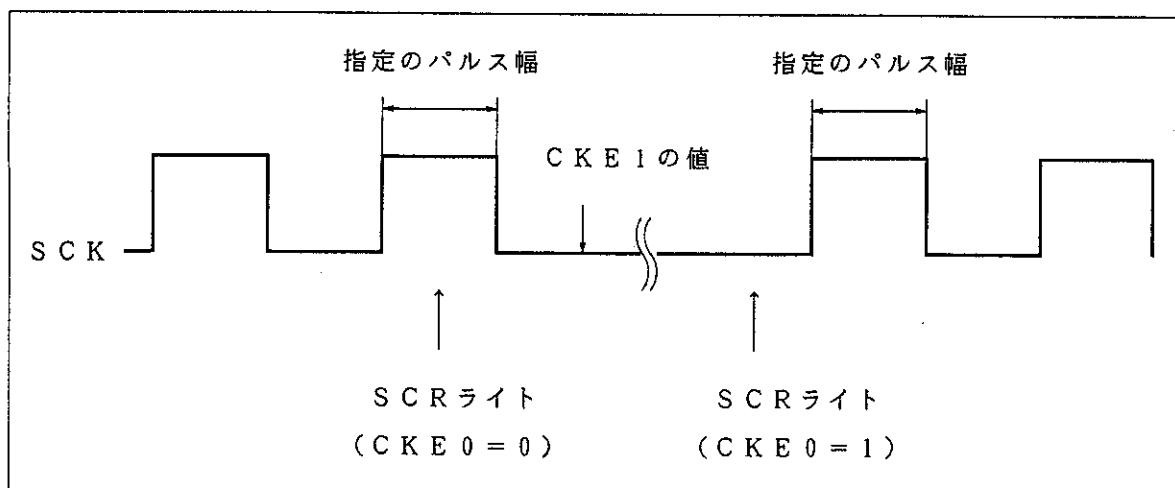

ビット1、0：クロックイネーブル1、0（CKE1、CKE0）

S C I のクロックソースの選択、およびS C K端子からのクロック出力の許可／禁止を設定します。スマートカードインタフェースモードにおいては、通常のクロック出力の許可／禁止の切り替え、およびクロック出力のH i g h レベル固定とL o w レベル固定を指定することができます。

| ビット7<br>GM | ビット1<br>CKE1 | ビット0<br>CKE0 | 説明                          |

|------------|--------------|--------------|-----------------------------|

| 0          | 0            | 0            | 内部クロック／S C K。端子は入出力ポート（初期値） |

|            |              | 1            | 内部クロック／S C K。端子はクロック出力      |

| 1          | 1            | 0            | 内部クロック／S C K。端子はLow出力固定     |

|            |              | 1            | 内部クロック／S C K。端子はクロック出力      |

|            | 1            | 0            | 内部クロック／S C K。端子はHigh出力固定    |

|            |              | 1            | 内部クロック／S C K。端子はクロック出力      |

## 14.3 動作説明

### 14.3.1 概要

スマートカードインターフェースの主な機能は次のとおりです。

- (1) 1フレームは、8ビットデータとパリティビットで構成されます。

- (2) 送信時は、パリティビットの終了から次のフレーム開始まで2etu(Elementary Time Unit: 1ビットの転送期間)以上のガードタイムをおきます。

- (3) 受信時はパリティエラーを検出した場合、スタートビットから10.5etu経過後エラーシグナル“Low”を1etu期間出力します。

- (4) 送信時はエラーシグナルをサンプリングすると、2etu以上経過後、自動的に同じデータを送信します。

- (5) 調歩同期式非同期通信機能のみサポートし、クロック同期式通信機能はありません。

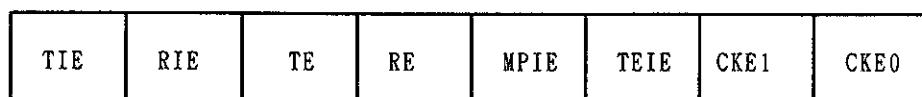

### 14.3.2 端子接続

図14.2にスマートカードインターフェースに関する端子接続概略図を示します。

ICカードとの通信においては、1本のデータ伝送線で送信と受信が行われるので、LSI端子でTXD<sub>0</sub>端子とRXD<sub>0</sub>端子とを結線してください。また、データ伝送線は、抵抗で電源V<sub>cc</sub>側にプルアップしてください。

スマートカードインターフェースで生成するクロックをICカードで使用する場合は、SCK<sub>0</sub>端子出力をICカードのCLK端子に入力します。ICカードで、内部クロックを使用する場合は接続不要です。

リセット信号としては、LSIのポート出力を使用します。

端子としては、これ以外に通常、電源とグランドの接続が必要です。

図14.2 スマートカードインターフェース端子接続概略図

【注】 ICカードを接続しないで、RE=TE="1"に設定すると、閉じた送信／受信が可能となり自己診断をすることができます。

### 14.3.3 データフォーマット

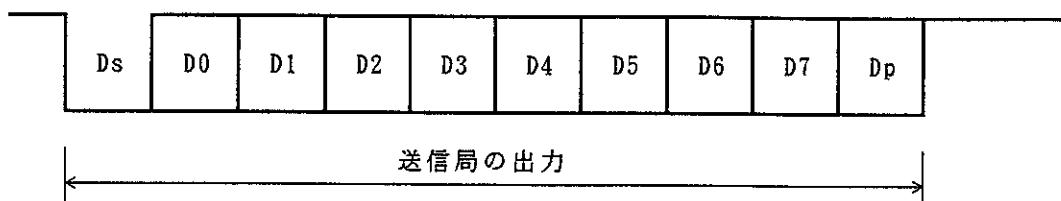

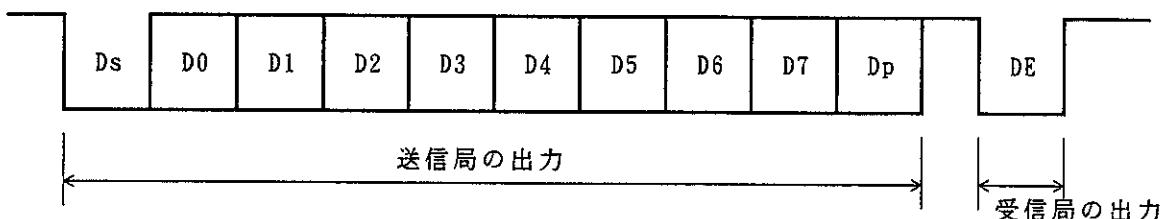

図14.3にスマートカードインターフェースのデータフォーマットを示します。このモードでは、受信時は1フレームごとにパリティチェックを行い、エラーが検出された場合送信側に対してエラーシグナルを送り返し、データの再送信要求をします。送信時はエラーシグナルをサンプリングすると同じデータを再送信します。

パリティエラーが発生しなかった場合

パリティエラーが発生した場合

D<sub>s</sub> : スタートビット D<sub>0</sub>~D<sub>7</sub> : データビット D<sub>p</sub> : パリティビット DE : エラーシグナル

図14.3 スマートカードインターフェースのデータフォーマット

動作シーケンスは次のようになっています。

- (1) データ線は、未使用時にはハイインピーダンス状態であり、プルアップ抵抗により“High”レベルに固定されます。

- (2) 送信側は、1フレームのデータ送信を開始します。データのフレームは、スタートビット (D<sub>s</sub>、“Low” レベル) から開始します。この後に、8ビットのデータビット (D<sub>0</sub>~D<sub>7</sub>) とパリティビット (D<sub>p</sub>) が続きます。

- (3) スマートカードインターフェースでは、この後にデータ線をハイインピーダンスに戻します。データ線はプルアップ抵抗により“High”レベルになります。

- (4) 受信側は、パリティチェックを行います。

パリティエラーが無く正常に受信した場合、そのまま次のデータ受信待ちます。

一方、パリティエラーが発生した場合は、エラーシグナル (DE、“Low” レベル) を出力し、データの再送信を要求します。受信局は、規定の期間エラーシグナルを出力した後、再び信号線をハイインピーダンスにします。信号線はプルアップ抵抗により“High”レベルに戻ります。

- (5) 送信側は、エラーシグナルを受信しなかった場合、次のフレームのデータ送信に移ります。

- 一方、エラーシグナルを受信した場合は、エラーとなったデータを(2)に戻り再送信します。

#### 14.3.4 レジスタ設定

スマートカードインタフェースで使用するレジスタのビットマップを表14.3に示します。

“0”または“1”が表示されているビットは、必ず表示されている値を設定してください。以下にそれ以外のビットの設定方法について説明します。

表14.3 スマートカードインタフェースでのレジスタ設定

| レジスタ    | アドレス <sup>*1</sup> | ビット  |      |      |      |      |      |                    |      |

|---------|--------------------|------|------|------|------|------|------|--------------------|------|

|         |                    | ビット7 | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1               | ビット0 |

| S M R   | H'FFB0             | GM   | 0    | 1    | 0/E  | 1    | 0    | CKS1               | CKS0 |

| B R R   | H'FFB1             | BRR7 | BRR6 | BRR5 | BRR4 | BRR3 | BRR2 | BRR1               | BRR0 |

| S C R   | H'FFB2             | TIE  | RIE  | TE   | RE   | 0    | 0    | CKE1 <sup>*2</sup> | CKE0 |

| T D R   | H'FFB3             | TDR7 | TDR6 | TDR5 | TDR4 | TDR3 | TDR2 | TDR1               | TDR0 |

| S S R   | H'FFB4             | TDRE | RDRF | ORER | ERS  | PER  | TEND | 0                  | 0    |

| R D R   | H'FFB5             | RDR7 | RDR6 | RDR5 | RDR4 | RDR3 | RDR2 | RDR1               | RDR0 |

| S C M R | H'FFB6             | —    | —    | —    | —    | SDIR | SINV | —                  | SMIF |

【注】- : 未使用ビットを示します。

\*<sup>1</sup> : アドレスは下位16ビットを示します。

\*<sup>2</sup> : SMR の GM を “0” に設定したときは、必ず CKE1 ビットを 0 にしてください。

##### (1) シリアルモードレジスタ (S M R) の設定

GM ビットは、通常のスマートカードインタフェースモード時は “0” を設定し、G S M モード時は “1” を設定します。

O/E ビットは I C カードがダイレクトコンベンション時は “0” を設定し、インバースコンベンション時は “1” を設定します。

CKS1、CKS0 ビットは、内蔵ボーレートジェネレータのクロックソースを選択します。

「14.3.5 クロック」を参照してください。

##### (2) ビットレートレジスタ (B R R) の設定

ビットレートを設定します。設定値の算出方法は「14.3.5 クロック」を参照してください。

##### (3) シリアルコントロールレジスタ (S C R) の設定

T I E、R I E、T E、R E ビットの機能は通常の S C I と同様です。詳細は「第13章 シリアルコミュニケーションインターフェース」を参照してください。

CKE1、CKE0 ビットはクロック出力を指定します。SMR の GM ビットが 0 にクリアされているとき、クロックを出力しない場合は、“0 0” に設定し、クロックを出力する場合は “0 1” に設定します。SMR の GM ビットが 1 にセットされているとき、クロック出力を行います。クロック出力を “L o w” レベルまたは “H i g h” レベルに固定することもできます。

(4) スマートカードモードレジスタ (SCMR) の設定

S DIR ビットは、ICカードがダイレクトコンベンション時は“0”を設定し、インバースコンベンション時は“1”を設定します。

S INV ビットは ICカードがダイレクトコンベンション時は“0”を設定し、インバースコンベンション時は“1”を設定します。

S MIF ビットはスマートカードインターフェースの場合“1”を設定します。

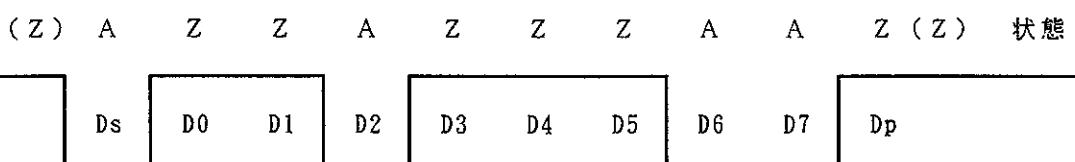

以下に2種類のICカード（ダイレクトコンベンションタイプとインバースコンベンションタイプ）に対するレジスタ設定値と開始キャラクタでの波形例を示します。

ダイレクトコンベンション ( $S\ DIR = S\ INV = 0 / \overline{E} = "0"$ )

ダイレクトコンベンションタイプでは、論理“1”レベルを状態“Z”に、論理“0”レベルを状態“A”に対応付け、LSBファーストで送受信する方式です。上記の開始キャラクタのデータはH'3Bとなります。

パリティビットは、スマートカードの規程により偶数パリティで“1”となります。

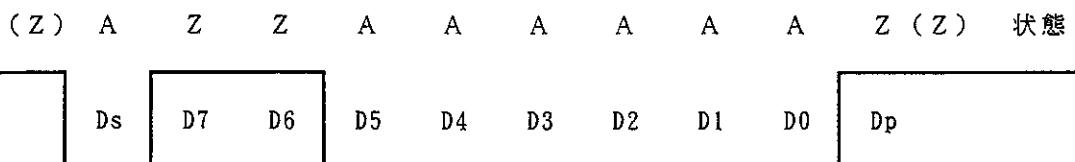

インバースコンベンション ( $S\ DIR = S\ INV = 0 / \overline{E} = "1"$ )

インバースコンベンションタイプでは、論理“1”レベルを状態“A”に、論理“0”レベルを状態“Z”に対応付け、MSBファーストで送受信する方式です。上記の開始キャラクタのデータはH'3Fとなります。

パリティビットは、スマートカードの規程により偶数パリティで論理“0”となり、状態“Z”が対応します。

なお、H8/3048シリーズでは、SINVビットによる反転はデータビットD7～D0のみとなっています。パリティビットの反転のためにSMRのO/Eビットを奇数パリティモードに設定します（送信、受信とも同様です）。

### 14.3.5 クロック

スマートカードインターフェースにおける送受信クロックは内蔵ボーレートジェネレータの生成した内部クロックのみ使用できます。このとき、ビットレートはビットレートレジスタ（BRR）とシリアルモードレジスタ（SMR）のCKS1、CKS0ビットで設定され、以下に示す計算式になります。ビットレートの例を表14.5に示します。

このときCKE0 = “1”でクロック出力を選択するとSCK0端子からはビットレートの372倍の周波数のクロックが出力されます。

$$B = \frac{\phi}{1488 \times 2^{2n-1} \times (N+1)} \times 10^6$$

ただし、N = BRRの設定値 ( $0 \leq N \leq 255$ )

B = ビットレート (bit/s)

$\phi$  = 動作周波数 (MHz) \*

n = 表14.4を参照

表14.4 nとCKS1、CKS0の対応表

| n | CKS1 | CKS0 |

|---|------|------|

| 0 | 0    | 0    |

| 1 | 0    | 1    |

| 2 | 1    | 0    |

| 3 | 1    | 1    |

【注】\* ギア機能によりクロックを分周して使用する場合には、動作周波数に分周比を考慮した値を設定してください。上記は分周比1:1の場合を示します。

表14.5 BRRの設定に対するビットレートB (bit/s)の例 (ただし、n = 0 のとき)

| N \ $\phi$ (MHz) | 7.1424 | 10.00   | 10.7136 | 13.00   | 14.2848 | 16.00   | 18.00   |

|------------------|--------|---------|---------|---------|---------|---------|---------|

| 0                | 9600.0 | 13440.9 | 14400.0 | 17473.1 | 19200.0 | 21505.4 | 24193.5 |

| 1                | 4800.0 | 6720.4  | 7200.0  | 8736.6  | 9600.0  | 10752.7 | 12096.8 |

| 2                | 3200.0 | 4480.3  | 4800.0  | 5824.4  | 6400.0  | 7168.5  | 8064.5  |

【注】 ビットレートは、小数点以下2桁目を四捨五入した数値です。

一方、動作周波数とビットレートからビットレートレジスタ（B R R）の設定値を算出する式は次のようにになります。ただし、Nは整数値、 $0 \leq N \leq 255$ であり、誤差の小さい方を指定します。

$$N = \frac{\phi}{1488 \times 2^{2n-1} \times B} \times 10^3 - 1$$

表14.6 ビットレートB (bit/s)に対するB R Rの設定例 (ただし、n = 0時)

| $\phi$ (MHz)<br>bit/s | 7.1424 |      | 10.00 |       | 10.7136 |       | 13.00 |      | 14.2848 |      | 16.00 |       | 18.00 |       |

|-----------------------|--------|------|-------|-------|---------|-------|-------|------|---------|------|-------|-------|-------|-------|

|                       | N      | 誤差   | N     | 誤差    | N       | 誤差    | N     | 誤差   | N       | 誤差   | N     | 誤差    | N     | 誤差    |

| 9.600                 | 0      | 0.00 | 1     | 30.00 | 1       | 25.00 | 1     | 8.99 | 1       | 0.00 | 1     | 12.01 | 2     | 15.99 |

表14.7 各周波数における最大ビットレート (スマートカードインターフェースモード時)

| $\phi$ (MHz) | 最大ビットレート (bit/s) | N | n |

|--------------|------------------|---|---|

| 7.1424       | 9600             | 0 | 0 |

| 10.00        | 13441            | 0 | 0 |

| 10.7136      | 14400            | 0 | 0 |

| 13.00        | 17473            | 0 | 0 |

| 14.2848      | 19200            | 0 | 0 |

| 16.00        | 21505            | 0 | 0 |

| 18.00        | 24194            | 0 | 0 |

ビットレート誤差は以下の計算式で求められます。

$$\text{誤差 (\%)} = \left( \frac{\phi}{1488 \times 2^{2n-1} \times B \times (N+1)} \times 10^6 - 1 \right) \times 100$$

#### 14.3.6 データの送信／受信動作

##### (1) イニシャライズ

データの送受信の前に、以下の手順でS C Iをイニシャライズしてください。送信モードから受信モードへの切り替え、受信モードから送信モードへの切り替えにおいてもイニシャライズが必要です。

- ①シリアルコントロールレジスタ（S C R）のT E、R Eビットを“0”にクリアします。

- ②シリアルステータスレジスタ（S S R）のエラーフラグE R S、P E R、O R E Rを“0”にクリアしてください。

- ③ シリアルモードレジスタ (S M R) のパリティビット (O /  $\overline{E}$  ビット) とボーレートジェネレータの選択ビット (C K S 1、C K S 0 ビット) を設定してください。このとき、C / A、C H R、M P ビットは “0” に、S T O P、P E ビットは “1” に設定してください。

- ④ スマートカードモードレジスタ (S C M R) のS M I F、S D I R、S I N V ビットを設定してください。

- S M I F ビットを “1” にセットすると、T X D<sub>0</sub> 端子およびR X D<sub>0</sub> 端子は共にポートからS C I の端子に切り換えられ、ハイインピーダンス状態となります。

- ⑤ ビットレートに対応する値をビットレートレジスタ (B R R) に設定します。

- ⑥ シリアルコントロールレジスタ (S C R) のクロックソースの選択ビット (C K E 0 ビット) を設定してください。このとき、T I E、R I E、T E、R E、M P I E、T E I E、C K E 1 ビットは、“0” に設定してください。

- C K E 0 ビットを “1” にセットした場合は、S C K 0 端子からクロック出力されます。

- ⑦ 少なくとも、1 ビット期間待ってから、S C R のT I E、R I E、T E、R E ビットを設定してください。自己診断以外はT E ビットとR E ビットを同時にセットしないでください。

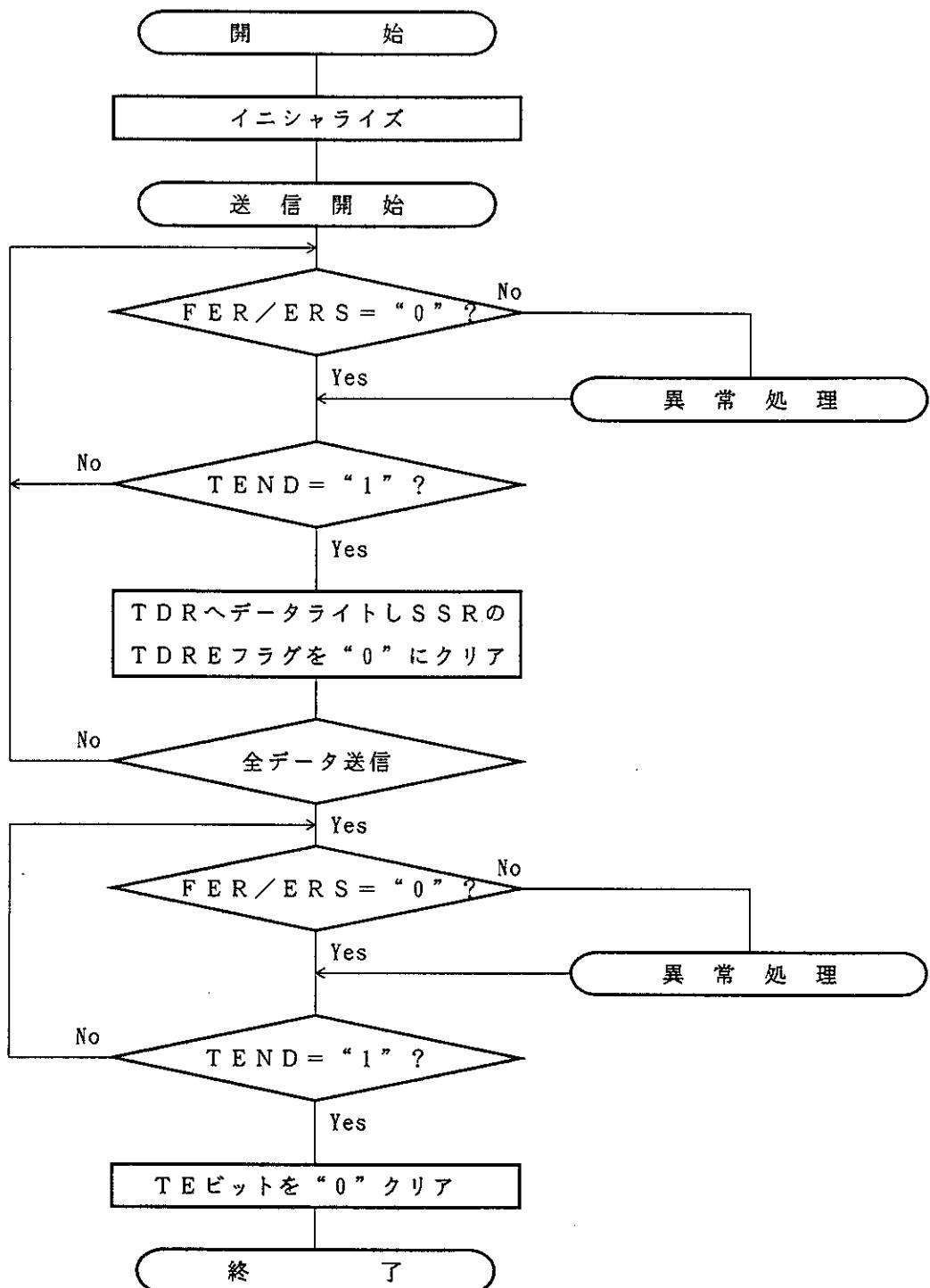

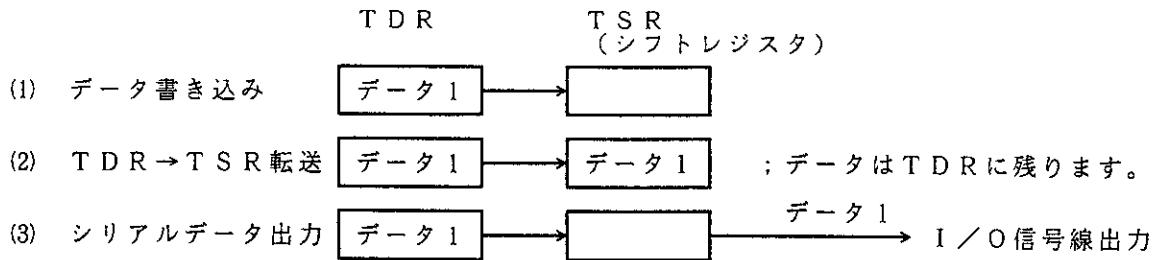

## (2) シリアルデータ送信

スマートカードモードにおけるデータ送信ではエラーシグナルのサンプリングと再送信処理があるため、通常のS C I とは処理手順が異なります。送信処理フローの例を図14.4に示します。また、送信動作と内部レジスタの関連を図14.5に示します。

- ① (1)の手順に従いスマートカードインターフェースモードにイニシャライズします。

- ② S S R のエラーフラグE R S ビットが “0” にクリアされていることを確認してください。

- ③ S S R のT E N D フラグが “1” にセットされていることが確認できるまで、②～③を繰り返してください。

- ④ T D R に送信データをライトして、T D R E フラグを “0” にクリアし送信動作を行います。このとき、T E N D フラグは “0” にクリアされます。

- ⑤ 連続してデータを送信する場合は、②に戻ってください。

- ⑥ 送信を終了する場合は、T E ビットを “0” にクリアします。

以上の一連の処理は、割込み処理またはD M A 転送が可能です。

T I E ビットを “1” にセットし、割込み要求を許可しておいたとき、送信が終了しT E N D フラグが “1” にセットされると、送信データエンプティ割込 (T X I) 要求を発生します。R I E ビットを “1” にセットし、割込み要求を許可しておいたとき、送信時にエラーが発生し、E R S フラグが “1” にセットされると、送受信エラー割込み (E R I) 要求を発生します。

S M R のG M ビットにより、T E N D フラグのセットタイミングが異なります。図14.6にT E N D フラグ発生タイミングを示します。

T X I 要求でD M A C 起動する場合、自動再転送を含めD M A C に設定したバイト数を自動的に送信することができます。

詳細は(6)割込動作、(7)D M A C によるデータ転送動作を参照してください。

図14.4 送信処理フローの例

ここで、正常な送信時 → T E N D フラグセット

送信エラー時 → E R S フラグセット

T E N D フラグがセットされるまで上記(2)(3)を繰り返す

**【注】** E R S フラグがセットされた場合、本フラグは続いて送信する再転送データの最終ビット (L S B ファーストの場合 D 7 、 M S B ファーストの場合 D 0 ) 転送完了時までにクリアしてください。

図14.5 送信動作と内部レジスタの関連

図14.6 T E N D フラグ発生タイミング

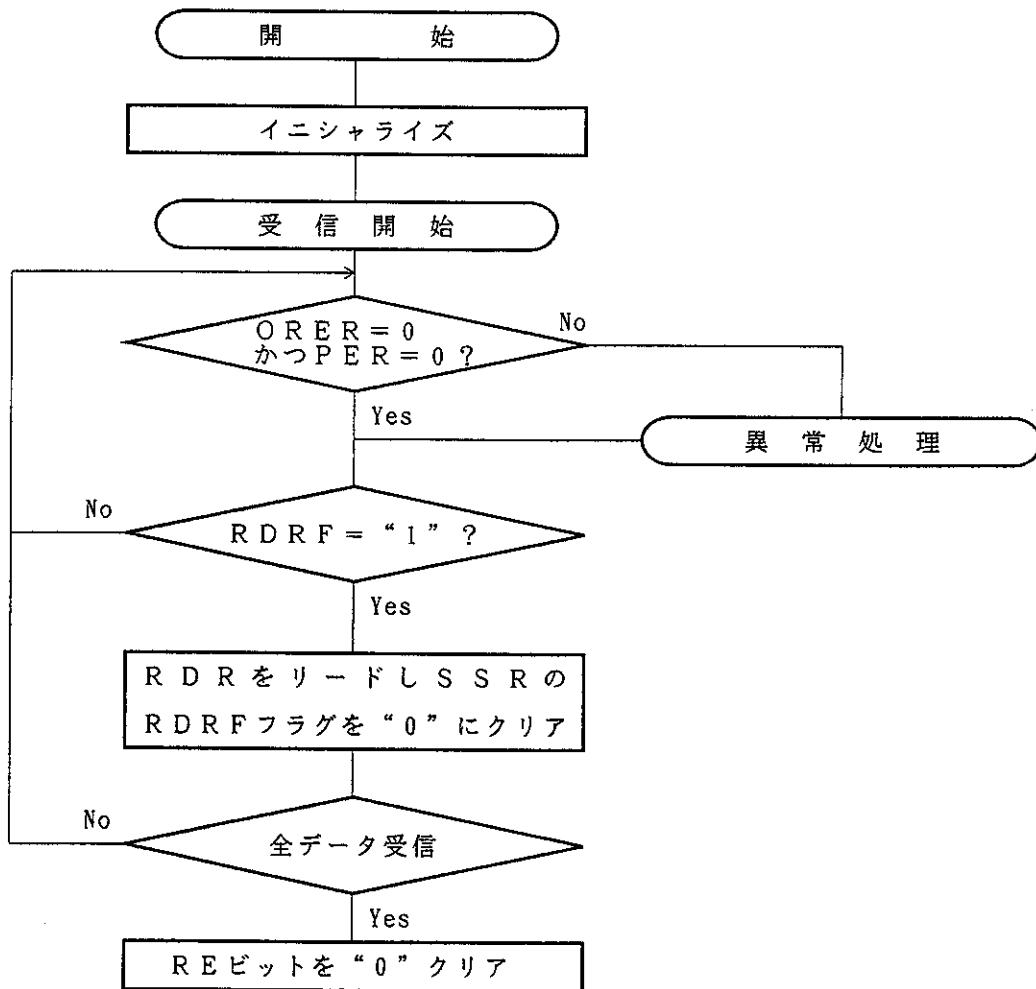

### (3) シリアルデータ受信

スマートカードモードのデータ受信は、通常の S C I と同様の処理手順になります。受信処理フローの例を図14.7に示します。

- ① S C I を(1)に従いスマートカードインタフェースモードにイニシャライズします。

- ② S S R の O R E R フラグと P E R フラグが “0” であることを確認してください。どちらかのフラグがセットされている場合は、所定の受信異常処理を行った後、 O R E R と P E R フラグを全て “0” にクリアしてください。

- ③ R D R F フラグが “1” であることを確認できるまで②、③を繰り返してください。

- ④ R D R から受信データをリードしてください。

- ⑤ 繼続してデータを受信する場合は、 R D R F フラグを “0” にクリアして②の手順に戻ってください。

- ⑥ 受信を終了する場合は、 R E ビットを “0” にクリアします。

図14.7 受信処理フローの例

以上の一連の処理は、割込み処理またはDMA転送が可能です。

RIEビットを“1”にセットし、割込み要求を許可しておいたとき受信が終了し、RDRFフラグが“1”にセットされると、受信データフル割込み(RXI)要求を発生します。また、受信時にエラーが発生しORER、PERフラグのいずれかが“1”にセットされると、送受信エラー割込み(ERI)要求を発生します。

RXI要求でDMACを起動する場合、エラーの発生した受信データをスキップしてDMACに設定したバイト数だけ受信データを転送します。

詳細は(6)、(7)を参照してください。

なお、受信時にパリティエラーが発生しPERが“1”にセットされた場合でも、受信したデータはRDRに転送されるのでこのデータをリードすることは可能です。

#### (4) モード切替動作

受信モードから送信モードに切り替える場合、受信動作が完了していることを確認した後、イニシャライズから開始し、RE = “0”、TE = “1”に設定してください。受信動作の完了はRDRFフラグあるいはPER、ORERフラグで確認できます。

送信モードから受信モードに切り替える場合、送信動作が完了していることを確認した後、イニシャライズから開始し、TE = “0”、RE = “1”に設定してください。送信動作の完了はTENDフラグで確認できます。

#### (5) クロック出力の固定

SMRのGMビットが1にセットされているとき、SCRのCKE1、CKE0ビットによってクロック出力を固定することができます。このときクロックパルスの最小幅を指定の幅とすることができます。

図14.8にクロック出力の固定タイミングを示します。GM = 1、CKE1 = 0とし、CKE0ビットを制御した場合の例です。

図14.8 クロック出力固定タイミング

#### (6) 割込動作

スマートカードインターフェースモードでは、送信データエンプティ割込（T X I）要求、送受信エラー割込（E R I）要求、受信データフル割込（R X I）要求の3種類の割込み要因があります。なお、本モードでは、送信終了割込（T E I）要求は使用できません。

S S R の T E N D フラグが“1”にセットされると、T X I 割込要求を発生します。

S S R の R D R F フラグが“1”にセットされると、R X I 割込要求を発生します。

S S R の O R E R 、 P E R 、 E R S フラグのいずれかが“1”にセットされると、E R I 割込み要求を発生します。これらの関係を表14.8に示します。

表14.8 スマートカードモードの動作状態と割込要因

| 動作状態  |      | フラグ             | マスクビット | 割込要因  | D M A C 起動 |

|-------|------|-----------------|--------|-------|------------|

| 送信モード | 正常動作 | T E N D         | T I E  | T X I | 可能         |

|       | エラー  | E R S           | R I E  | E R I | 不可能        |

| 受信モード | 正常動作 | R D R F         | R I E  | R X I | 可能         |

|       | エラー  | P E R 、 O R E R | R I E  | E R I | 不可能        |

#### (7) D M A C によるデータ転送動作

スマートカードモードの場合も通常のS C I の場合と同様に、D M A C を使って送受信を行うことができます。送信動作では、S S R の T E N D フラグが“1”にセットされると同時にT D R E フラグもセットされ、T X I 割込みが発生します。あらかじめD M A C の起動要因にT X I 要求を設定しておけば、T X I 要求によりD M A C が起動されて送信データの転送を行います。T D R E およびT E N D フラグは、D M A C によるデータ転送時に自動的に“0”にクリアされます。エラーが発生した場合はS C I が自動的に同じデータを再送信します。この間T E N D は“0”的まま保持され、D M A C は起動されません。したがって、エラー発生時の再送信を含め、S C I とD M A C が指定されたバイト数を自動的に送信します。ただし、エラー発生時E R S フラグは、自動的にクリアされませんのでR I E ビットを“1”にセットしておき、エラー発生時にE R I 要求を発生させ、E R S をクリアしてください。

なお、D M A C を使って送受信を行う場合は必ず先にD M A C を設定し、イネーブル状態にしてからS C I の設定を行ってください。D M A C の設定方法は「第8章 D M A コントローラ」を参照してください。

なお、受信動作では、S S R の R D R F フラグが“1”にセットされるとR X I 割込要求が発生します。あらかじめD M A C の起動要因にR X I 要求を設定しておけばR X I 要求でD M A C が起動されて受信データの転送を行います。R D R F フラグは、D M A C によるデータ転送時に自動的に“0”にクリアされます。エラーが発生した場合は、R D R F フラグはセットされずエラーフラグがセットされます。D M A C は起動されず、かわりにC P U に対しE R I を発生しますのでエラーフラグをクリアしてください。

#### (8) GSMモード時の動作例

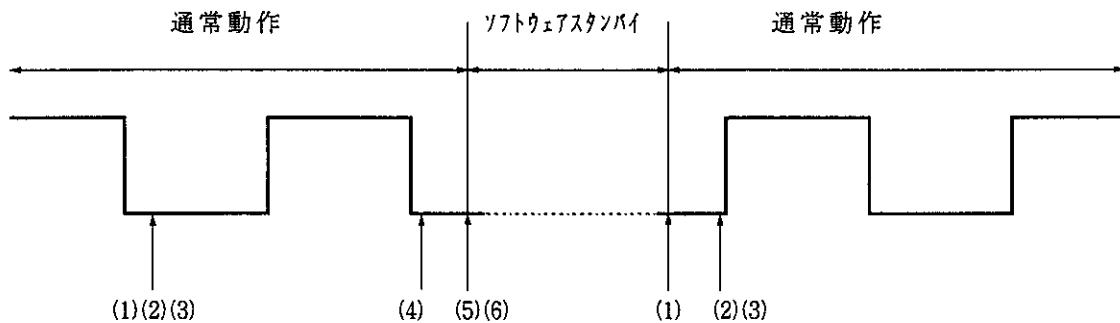

スマートカードインターフェースモードとソフトウェアスタンバイ間でモード切替えを行う際、クロックデューティを保持するため、下記の切り替え手順で処理してください。

#### ■スマートカードインターフェースモードからソフトウェアスタンバイモードに遷移するとき

- (1) P<sub>9</sub>のデータレジスタ（D R）とデータディレクションレジスタ（D D R）をソフトウェアスタンバイ時の出力固定状態の値に設定する。

- (2)シリアルコントロールレジスタ（S C R）のT EビットとR Eビットに“0”を書き込み、送信/受信動作を停止させる。同時に、C K E 1ビットをソフトウェアスタンバイ時の出力固定状態の値に設定する。

- (3) S C RのC K E 0ビットに“0”を書き込み、クロックを停止させる。

- (4)シリアルクロックの1クロック周期の間、待つ。

この間に、デューティを守って、指定のレベルでクロック出力は固定される。

- (5)シリアルモードレジスタ（S M R）とスマートカードモードレジスタ（S C M R）にH'00を書込む。

- (6)ソフトウェアスタンバイ状態に遷移させる。

#### ■ソフトウェアスタンバイモードからスマートカードインターフェースモードに戻す時

- (1)ソフトウェアスタンバイ状態を解除する。

- (2) S C RのC K E 1ビットをソフトウェアスタンバイ開始時の出力固定状態（現在のP<sub>9</sub>端子の状態）の値に設定する。

- (3)スマートカードインターフェースモードに設定し、クロック出力させる。正常なデューティにてクロック信号発生を開始する。

図14.9 クロック停止・再起動手順

電源投入時からクロックデューティを確保するためには、下記の切替え手順で処理をしてください。

- (1) 初期状態は、ポート入力でありハイインピーダンスである。電位を固定するには、プルアップ抵抗／プルダウン抵抗を使用する。

- (2) S C R の C K E 1 ビットで指定の出力に固定する。

- (3) S M R と S C M R をセットし、スマートカードインターフェースモードの動作に切り替える。

- (4) S C R の C K E 0 ビットを“1”に設定して、クロック出力を開始する。

#### 14.4 使用上の注意

S C I をスマートカードインターフェースとして使用する際は、以下のことに注意してください。

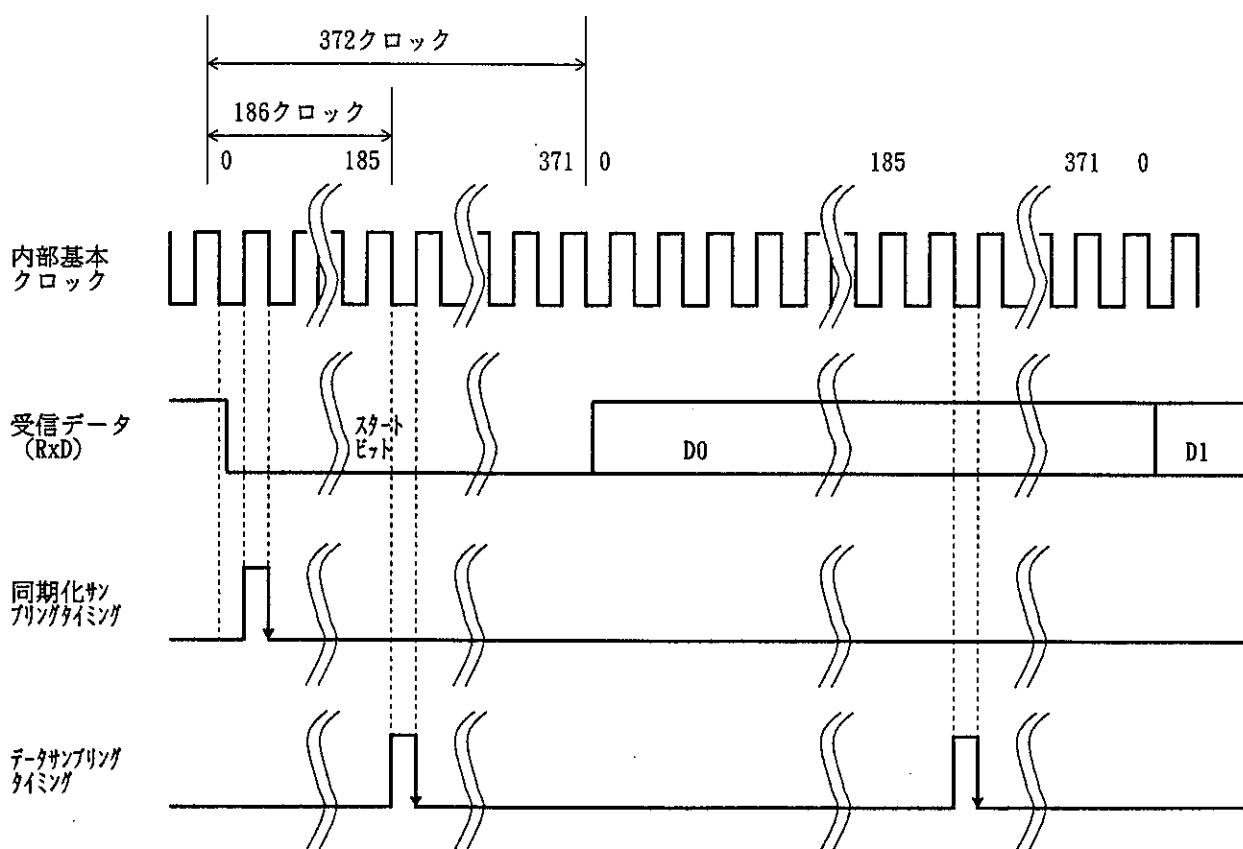

- (1) スマートカードインターフェースモードの受信データサンプリングタイミングと受信マージン

スマートカードインターフェースモードでは、S C I は転送レートの372倍の周波数の基本クロックで動作しています。

受信時にS C I は、スタートビットの立ち下がりを基本クロックでサンプリングして、内部を同期化します。また、受信データを基本クロックの186クロック目の立ち上がりエッジで内部に取り込みます。これを図14.10 に示します。

図14.10 スマートカードモード時の受信データサンプリングタイミング

したがって、受信マージンは、次の式のようになります。

#### スマートカードインターフェースモード時の受信マージン式

$$M = \left| \left( 0.5 - \frac{1}{2N} \right) - (L - 0.5)F - \frac{|D - 0.5|}{N} (1 + F) \right| \times 100\%$$

M : 受信マージン (%)

N : クロックに対するビットレートの比 (N = 372)

D : クロックデューティー (D = 0 ~ 1.0)

L : フレーム長 (L = 10)

F : クロック周波数の偏差の絶対値

上式で、F = 0、D = 0.5 とすると、受信マージン式は次のようになります。

D = 0.5、F = 0 のとき、

$$M = (0.5 - 1/2 \times 372) \times 100\%$$

$$= 49.866\%$$

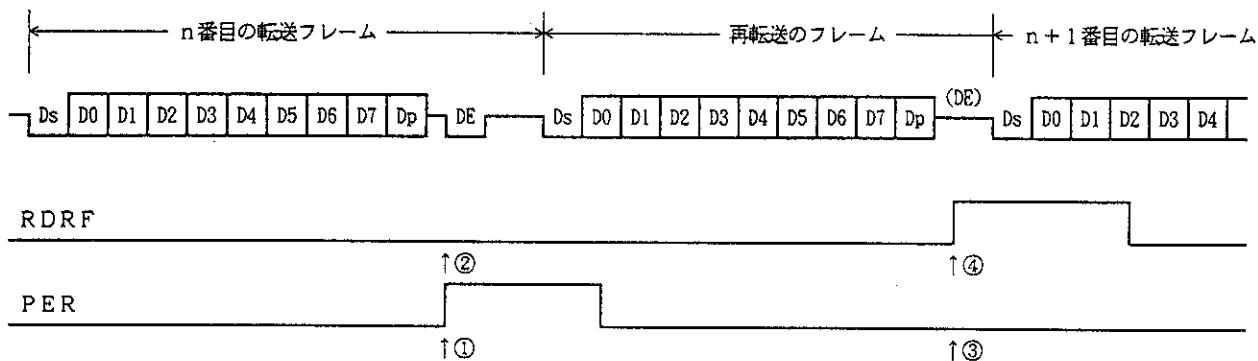

## (2) 再転送動作

S C I がそれぞれ受信モードの場合と、送信モードの場合の再転送動作を、次に示します。

### ■ S C I が受信モードの場合の再転送動作

S C I 受信モードの場合の再転送動作を図14.11 に示します。

- ① 受信したパリティビットをチェックした結果、エラーが検出されると、S S R の P E R ビットが自動的に 1 にセットされます。このとき、S C R の R I E ビットがイネーブルになっていれば、R X I 割込み要求が発生します。次のパリティビットのサンプリングタイミングまでに、S S R の P E R ビットを“0”にクリアしてください。

- ② 異常が発生したフレームでは、S S R の R D R F ビットはセットされません。

- ③ 受信したパリティビットをチェックした結果、エラーが検出されない場合は、S S R の P E R ビットはセットされません。

- ④ 受信したパリティビットをチェックした結果、エラーが検出されない場合は、正常に受信動作が完了したと判断して、S S R の R D R F ビットが自動的に 1 にセットされます。このとき S C R の R I E ビットが許可になっていれば、R X I 割込み要求が発生します。さらに、R X I 要因によるD M A 転送が許可されていれば、R D R の内容を自動的に読み出すことができます。D M A C でR D R のデータを読み出した場合、R D R F は自動的に“0”にクリアされます。

- ⑤ 正常なフレームを受信した場合、エラーシグナルを送信するタイミングで端子はスリーステート状態を保持します。

図14.11 S C I 受信モードの場合の再転送動作

## ■ S C I が送信モードの場合の再転送動作

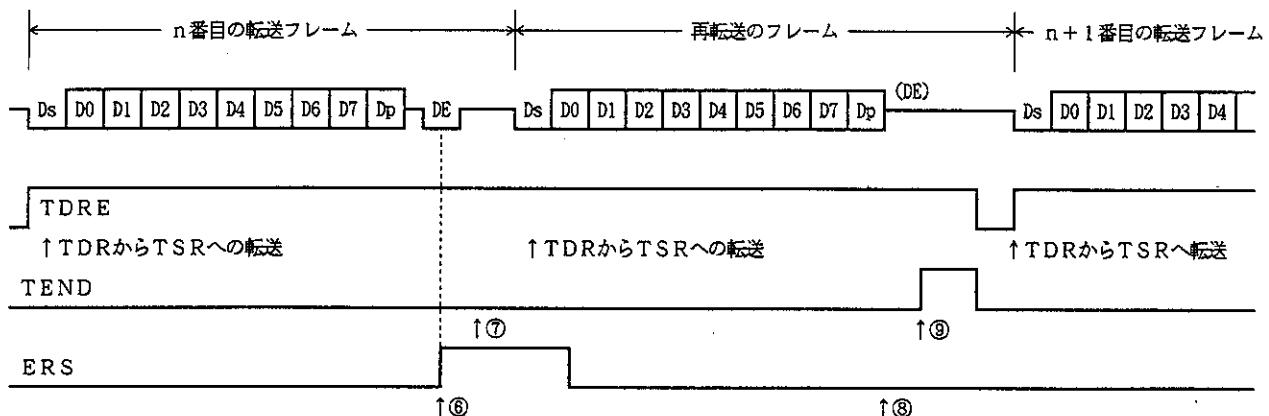

S C I 送信モードの場合の再転送動作を図14.12 に示します。

- ⑥ 1 フレーム分の送信を完了した後、受信側からエラーシグナルが返されると、S S R の E R S ビットが 1 にセットされます。このとき、S C R の R I E ビットがイネーブルになっていれば、E R I 割込み要求が発生します。次のパリティビットのサンプリングタイミングまでに、S S R の E R S ビットを “0” にクリアしてください。

- ⑦ 異常を示すエラーシグナルを受信したフレームでは、S S R の T E N D ビットはセットされません。

- ⑧ 受信側からエラーシグナルが返ってこない場合は、S S R の E R S ビットはセットされません。

- ⑨ 受信側からエラーシグナルが返ってこない場合は、再転送を含む 1 フレームの送信が完了したと判断して、S S R の T E N D ビットが “1” にセットされます。このとき S C R の T I E ビットがイネーブルになっていれば、T X I 割込み要求を発生します。

さらに、T X I 要因によるD M A 転送が許可されていれば、自動的にT D R に次のデータを書込むことができます。D M A C でT D R にデータを書き込んだ場合、T D R E ビットは自動的に “0” にクリアされます。

図14.12 S C I 送信モードの場合の再転送動作