# 15. A/D 変換器

## 第15章 目次

|                                    |     |

|------------------------------------|-----|

| 15.1 概要                            | 575 |

| 15.1.1 特長                          | 575 |

| 15.1.2 ブロック図                       | 576 |

| 15.1.3 端子構成                        | 577 |

| 15.1.4 レジスタ構成                      | 578 |

| 15.2 各レジスタの説明                      | 579 |

| 15.2.1 A/DデータレジスタA～D (ADDRA～D)     | 579 |

| 15.2.2 A/Dコントロール／ステータスレジスタ (ADCSR) | 580 |

| 15.2.3 A/Dコントロールレジスタ (ADCR)        | 583 |

| 15.3 CPUとのインターフェイス                 | 584 |

| 15.4 動作説明                          | 585 |

| 15.4.1 単一モード (SCAN = "0")          | 585 |

| 15.4.2 スキャンモード (SCAN = "1")        | 587 |

| 15.4.3 入力サンプリングとA/D変換時間            | 589 |

| 15.4.4 外部トリガ入力タイミング                | 590 |

| 15.5 割込み                           | 591 |

| - 15.6 使用上の注意                      | 591 |

## 15.1 概要

H 8 / 3048 シリーズには、逐次比較方式で動作する10ビットのA/D変換器が内蔵されており、最大8チャネルのアナログ入力を選択することができます。

消費電流低減のためにA/D変換器を使用しない場合には、A/D変換器を単独に停止することができます。詳細は「20.6 モジュールスタンバイ機能」を参照してください。

### 15.1.1 特長

A/D変換器の特長を以下に示します。

- 10ビットの分解能

- 入力チャネル：8チャネル

- アナログ変換電圧範囲の設定が可能

リファレンス電圧端子( $V_{REF}$ )をアナログ基準電圧としてアナログ変換電圧範囲を設定します。

- 高速変換

変換時間：1チャネル当り最小 $7.4\mu s$  (18MHz動作時)

- 単一モード／スキャンモードの2種類の動作モードから選択可能

- 单一モード：1チャネルのA/D変換

- スキャンモード：1～4チャネルの連続A/D変換

- 4本の16ビットデータレジスタ

A/D変換された結果は、各チャネルに対応したデータレジスタに転送され、保持されます。

- サンプル&ホールド機能

- 外部トリガ信号による、A/D変換の開始が可能

- A/D変換終了割込み要求を発生

A/D変換終了時には、A/D変換終了割込み (ADI) 要求を発生させることができます。

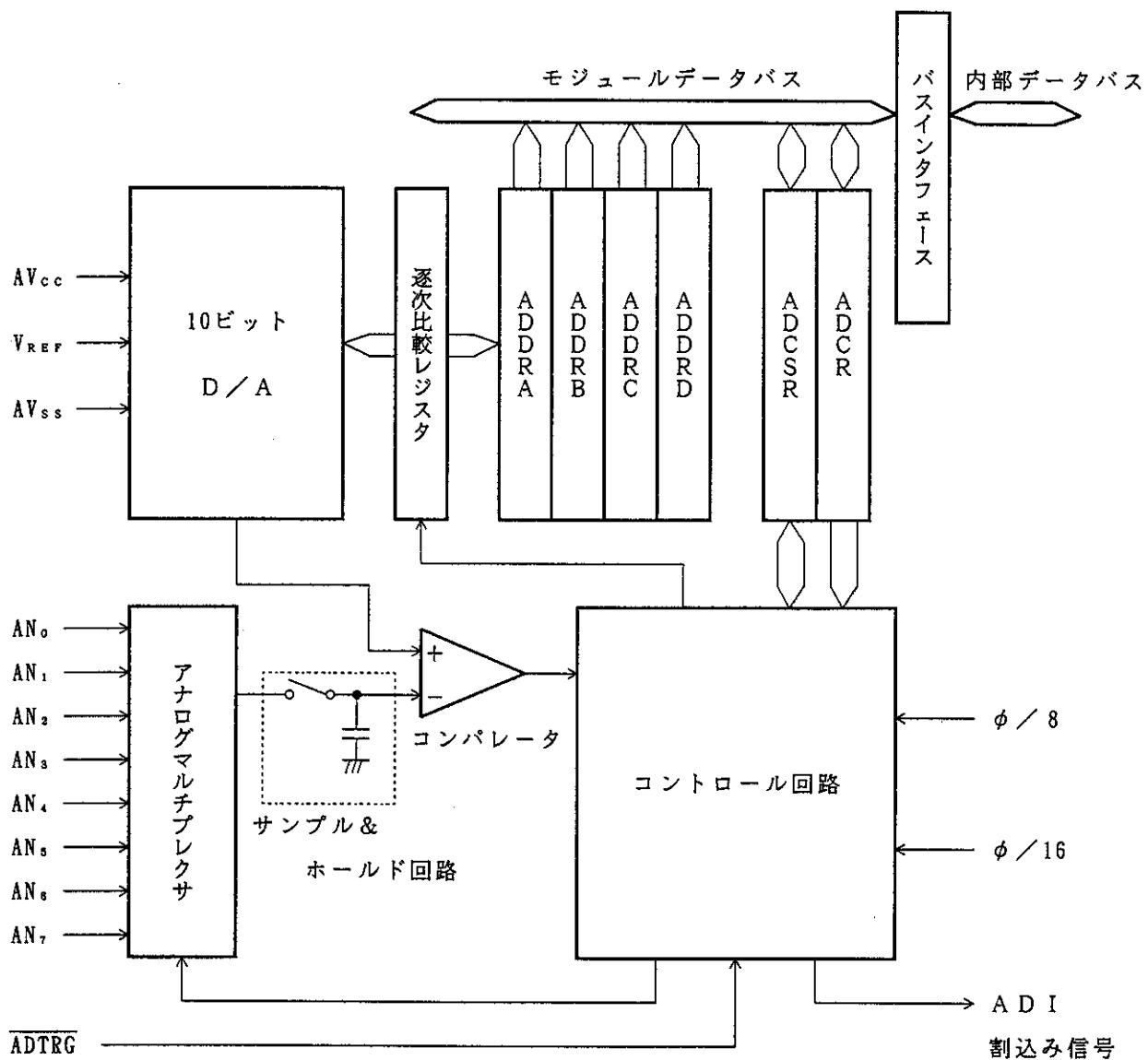

### 15.1.2 ブロック図

A/D変換器のブロック図を図15.1に示します。

図15.1 A/D変換器のブロック図

### 15.1.3 端子構成

A/D変換器で使用する入力端子を表15.1に示します。

8本のアナログ入力端子は2グループに分類されており、アナログ入力端子0～3(AN<sub>0</sub>～AN<sub>3</sub>)がグループ0、アナログ入力端子4～7(AN<sub>4</sub>～AN<sub>7</sub>)がグループ1になっています。

AV<sub>cc</sub>、AV<sub>ss</sub>端子は、A/D変換器内のアナログ部の電源です。V<sub>REF</sub>端子は、A/D変換基準電圧端子です。

表15.1 端子構成

| 端子名          | 略称               | 入出力 | 機能                 |

|--------------|------------------|-----|--------------------|

| アナログ電源端子     | AV <sub>cc</sub> | 入力  | アナログ部の電源           |

| アナロググランド端子   | AV <sub>ss</sub> | 入力  | アナログ部のグランドおよび基準電圧  |

| リファレンス電圧端子   | V <sub>REF</sub> | 入力  | アナログ部の基準電圧         |

| アナログ入力端子0    | AN <sub>0</sub>  | 入力  | グループ0のアナログ入力       |

| アナログ入力端子1    | AN <sub>1</sub>  | 入力  |                    |

| アナログ入力端子2    | AN <sub>2</sub>  | 入力  |                    |

| アナログ入力端子3    | AN <sub>3</sub>  | 入力  |                    |

| アナログ入力端子4    | AN <sub>4</sub>  | 入力  | グループ1のアナログ入力       |

| アナログ入力端子5    | AN <sub>5</sub>  | 入力  |                    |

| アナログ入力端子6    | AN <sub>6</sub>  | 入力  |                    |

| アナログ入力端子7    | AN <sub>7</sub>  | 入力  |                    |

| A/D外部トリガ入力端子 | ADTRG            | 入力  | A/D変換開始のための外部トリガ入力 |

#### 15.1.4 レジスタ構成

A/D変換器のレジスタ構成を表15.2に示します。

表15.2 レジスタ構成

| アドレス <sup>*1</sup> | 名 称                 | 略 称    | R/W                 | 初期値  |

|--------------------|---------------------|--------|---------------------|------|

| H'FFE0             | A/DデータレジスタAH        | ADDRAH | R                   | H'00 |

| H'FFE1             | A/DデータレジスタAL        | ADDRAL | R                   | H'00 |

| H'FFE2             | A/DデータレジスタBH        | ADDRBH | R                   | H'00 |

| H'FFE3             | A/DデータレジスタBL        | ADDRBL | R                   | H'00 |

| H'FFE4             | A/DデータレジスタCH        | ADDRCH | R                   | H'00 |

| H'FFE5             | A/DデータレジスタCL        | ADDRCL | R                   | H'00 |

| H'FFE6             | A/DデータレジスタDH        | ADDRDH | R                   | H'00 |

| H'FFE7             | A/DデータレジスタDL        | ADDRDL | R                   | H'00 |

| H'FFE8             | A/Dコントロール/ステータスレジスタ | ADCSR  | R/(W) <sup>*2</sup> | H'00 |

| H'FFE9             | A/Dコントロールレジスタ       | ADCR   | R/W                 | H'7E |

【注】<sup>\*1</sup> アドレスの下位16ビットを示しています。

<sup>\*2</sup> ビット7は、フラグをクリアするための“0”ライトのみ可能です。

## 15.2 各レジスタの説明

### 15.2.1 A/DデータレジスタA~D (ADDRA~D)

| ビット         | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|---|---|---|

| ADDRn       | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 | — | — | — | — | — | — |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W         | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R | R | R | R | R | R |

| (n = A ~ D) |     |     |     |     |     |     |     |     |     |     |   |   |   |   |   |   |

A/D変換データ      リザーブビット

A/D変換結果の10ビットデータを

格納するビットです。

ADDRは、A/D変換された結果を格納する16ビットのリード専用レジスタで、ADDRA～ADDRDの4本があります。

A/D変換されたデータは10ビットデータで、選択されたチャネルのADDRに転送され、保持されます。A/D変換されたデータの上位8ビットがADDRの上位バイトに、また下位2ビットが下位バイトに対応します。ADDRの下位バイトのビット5～0はリザーブビットで、リードすると常に“0”が読み出されます。アナログ入力チャネルとADDRの対応を表15.3に示します。

ADDRは、常にCPUからリード可能です。上位バイトは直接リードできますが、下位バイトはテンポラリレジスタ(TEMP)を介してデータ転送が行われます。詳細は「15.3 CPUとのインターフェース」を参照してください。

ADDRは、リセットまたはスタンバイモード時に、#0000にイニシャライズされます。

表15.3 アナログ入力チャネルとADDRA～ADD RDの対応

| アナログ入力チャネル      |                 | A/Dデータレジスタ |

|-----------------|-----------------|------------|

| グループ0           | グループ1           |            |

| AN <sub>0</sub> | AN <sub>4</sub> | ADDRA      |

| AN <sub>1</sub> | AN <sub>5</sub> | ADD RB     |

| AN <sub>2</sub> | AN <sub>6</sub> | ADD RC     |

| AN <sub>3</sub> | AN <sub>7</sub> | ADD RD     |

### 15.2.2 A/Dコントロール/ステータスレジスタ (ADC S R)

【注】\* フラグをクリアするための“0”ライトのみ可能です。

A D C S R は、 8 ビットのリード／ライト可能なレジスタで、モードの選択など A / D 変換器の動作を制御します。

A D C S R は、リセットまたはスタンバイモード時に、H'00にイニシャライズされます。

### ビット7：A/Dエンドフラグ（A D F）

A/D変換の終了を示すステータスフラグです。

| ビット7  | 説明                                                                          |

|-------|-----------------------------------------------------------------------------|

| A D F |                                                                             |

| 0     | 〔クリア条件〕<br>A D F = “1” の状態で、A D F フラグをリードした後、A D F フラグに“0”をライトしたとき<br>(初期値) |

| 1     | 〔セット条件〕<br>(1) 単一モード：A/D変換が終了したとき<br>(2) スキャンモード：設定されたすべてのチャネルのA/D変換が終了したとき |

### ビット6：A/Dインターラプトイネーブル（A D I E）

A/D変換の終了による割込み（A D I）要求の許可／禁止を選択します。

| ビット6    | 説明                                 |

|---------|------------------------------------|

| A D I E |                                    |

| 0       | A/D変換終了による割込み（A D I）要求を禁止<br>(初期値) |

| 1       | A/D変換終了による割込み（A D I）要求を許可          |

### ビット5：A/Dスタート（A D S T）

A/D変換の開始／停止を選択します。

A/D変換中は“1”を保持します。また、A D S T ビットはA/D外部トリガ入力端子(ADTRG)により“1”にセットすることもできます。

| ビット5    | 説明                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------|

| A D S T |                                                                                                                          |

| 0       | A/D変換を停止<br>(初期値)                                                                                                        |

| 1       | (1) 単一モード：A/D変換を開始し、変換が終了すると自動的に“0”にクリア<br>(2) スキャンモード：A/D変換を開始し、ソフトウェア、リセット、またはスタンバイモードによって“0”にクリアされるまで選択されたチャネルを順次連続変換 |

#### ビット4：スキャンモード（S C A N）

A/D変換のモードを、單一モード／スキャンモードから選択します。單一モード／スキャンモード時の動作については、「15.4 動作説明」を参照してください。モードの切換えは、A D S T = “0”の状態で行ってください。

| ビット4    | 説明      |       |

|---------|---------|-------|

| S C A N |         |       |

| 0       | 單一モード   | (初期値) |

| 1       | スキャンモード |       |

#### ビット3：クロックセレクト（C K S）

A/D変換時間の設定を行います。

変換時間の切換えは、A D S T = “0”の状態で行ってください。

| ビット3  | 説明                  |       |

|-------|---------------------|-------|

| C K S |                     |       |

| 0     | 変換時間 = 266ステート(max) | (初期値) |

| 1     | 変換時間 = 134ステート(max) |       |

#### ビット2～0：チャネルセレクト2～0（C H 2～0）

S C A Nビットとともにアナログ入力チャネルを選択します。

チャネル選択と切換えは、A D S T = “0”の状態で行ってください。

| グループ選択 | チャネル選択 |       | 説明                     |                                    |

|--------|--------|-------|------------------------|------------------------------------|

| C H 2  | C H 1  | C H 0 | 單一モード                  | スキャンモード                            |

| 0      | 0      | 0     | A N <sub>0</sub> (初期値) | A N <sub>0</sub>                   |

|        | 0      | 1     | A N <sub>1</sub>       | A N <sub>0</sub> 、A N <sub>1</sub> |

|        | 1      | 0     | A N <sub>2</sub>       | A N <sub>0</sub> ～A N <sub>2</sub> |

|        | 1      | 1     | A N <sub>3</sub>       | A N <sub>0</sub> ～A N <sub>3</sub> |

| 1      | 0      | 0     | A N <sub>4</sub>       | A N <sub>4</sub>                   |

|        | 0      | 1     | A N <sub>5</sub>       | A N <sub>4</sub> 、A N <sub>5</sub> |

|        | 1      | 0     | A N <sub>6</sub>       | A N <sub>4</sub> ～A N <sub>6</sub> |

|        | 1      | 1     | A N <sub>7</sub>       | A N <sub>4</sub> ～A N <sub>7</sub> |

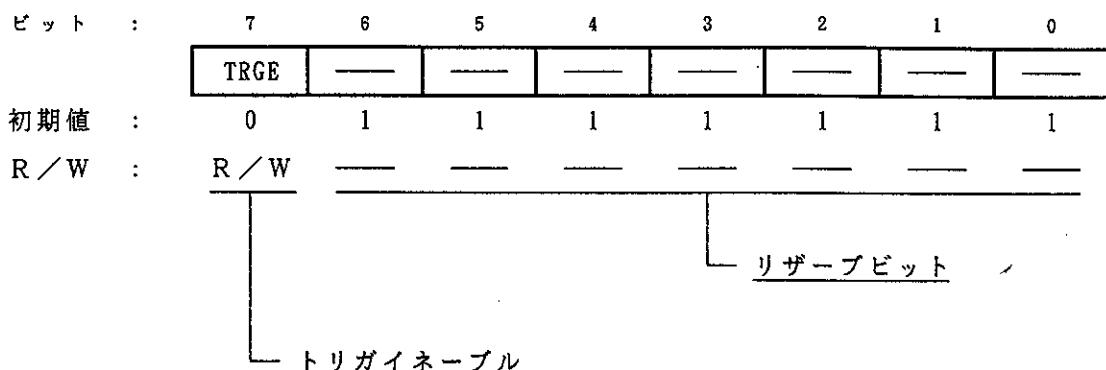

### 15.2.3 A/Dコントロールレジスタ (ADC R)

外部トリガによるA/D変換の許可/禁止を選択するビットです。

ADC Rは、8ビットのリード/ライト可能なレジスタで、外部トリガ入力によるA/D変換の開始の許可/禁止を選択します。

ADC Rは、リセットまたはスタンバイモード時、H'7Fにイニシャライズされます。

#### ビット7：トリガイネーブル (TRGE)

外部トリガ入力によるA/D変換の開始の許可/禁止を選択します。

| ビット7 | 説明                                |

|------|-----------------------------------|

| TRGE |                                   |

| 0    | 外部トリガ入力によるA/D変換の開始を禁止<br>(初期値)    |

| 1    | 外部トリガ端子 (ADTRG) の立下がりエッジでA/D変換を開始 |

#### ビット6～0：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

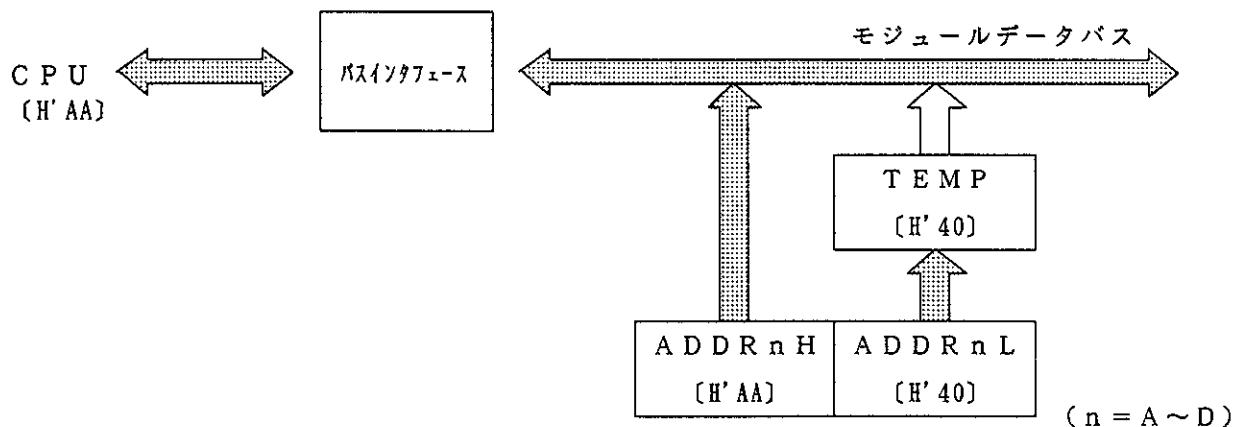

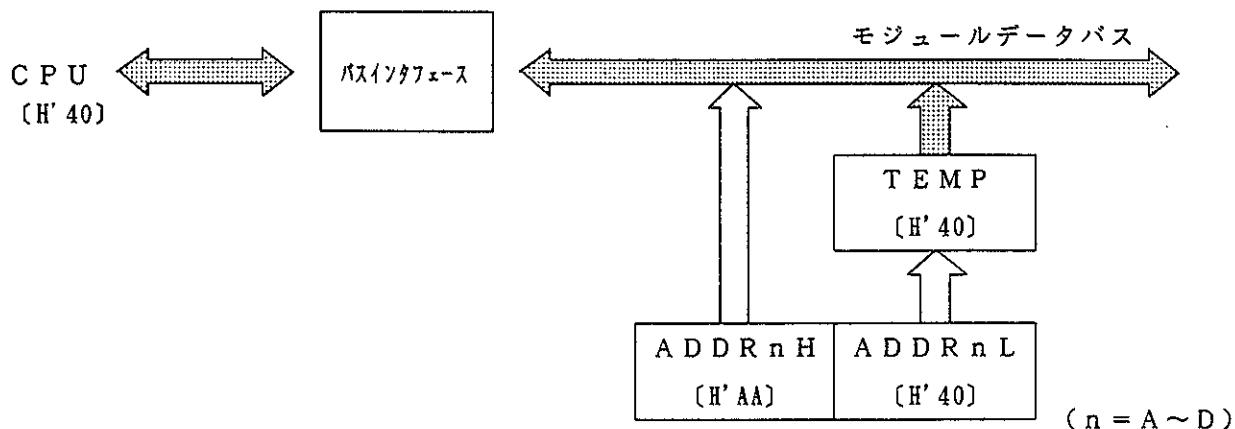

### 15.3 CPUとのインターフェース

ADDRA～ADDRDはそれぞれ16ビットのレジスタですが、CPUとの間のデータバスは8ビット幅です。そのため、CPUからのアクセスは上位バイトは直接行われますが、下位バイトは8ビットのテンポラリレジスタ（TEMP）を介して行います。

ADDRからのデータのリードは、次のように行われます。上位バイトのリードで上位バイトの値はCPUへ、下位バイトの値はTEMPへ転送されます。次に下位バイトのリードでTEMPの内容がCPUへ転送されます。

ADDRをリードする場合は、必ず上位バイト、下位バイトの順で行ってください。また、上位バイトのみのリードは可能ですが、下位バイトのみのリードでは内容は保証されませんので注意してください。

図15.2に、ADDRのアクセス時のデータの流れを示します。

<上位バイトのリード>

<下位バイトのリード>

図15.2 ADDRのアクセス動作 ([H'AA40] リード時)

## 15.4 動作説明

A/D変換器は逐次比較方式で動作し、10ビットの分解能をもっています。単一モードとスキャンモードの各モードの動作についての説明をします。

### 15.4.1 単一モード (SCAN = "0")

单一モードは、1チャネルのみのA/D変換を行う場合に選択します。ソフトウェアまたは外部トリガ入力によってADSTビットが“1”にセットされると、A/D変換を開始します。ADSTビットは、A/D変換中は“1”を保持しており、変換が終了すると自動的に“0”にクリアされます。

また、変換が終了すると、ADFフラグが“1”にセットされます。このとき、ADI Eビットが“1”にセットされていると、ADI割込み要求が発生します。

ADFフラグは、ADC SRをリードした後、“0”をライトするとクリアされます。

A/D変換中に、モードやアナログ入力チャネルの切換えを行う場合は、誤動作を避けるためにADC SRのADSTビットを“0”にクリアして、A/D変換を停止した状態で行ってください。変更した後、ADSTビットを“1”にセットすると（モードおよびチャネルの変更とADSTビットのセットは、同時に行うことができます）、再びA/D変換を開始します。

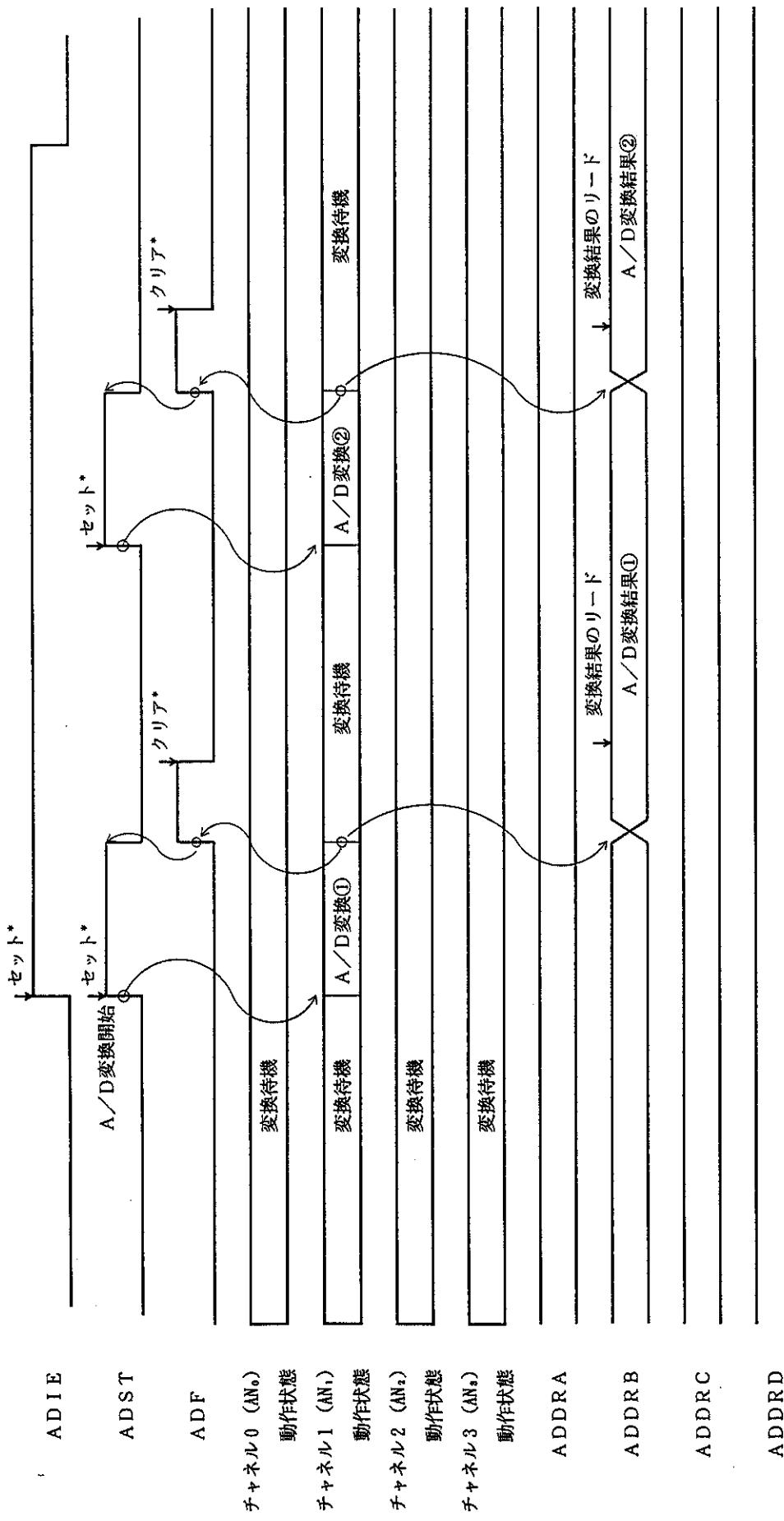

单一モードでチャネル1(AN<sub>1</sub>)が選択された場合の動作例を以下に示します。また、このときの動作タイミングを図15.3に示します。

- (1) 動作モードを单一モードに(SCAN = "0")、入力チャネルをAN<sub>1</sub>に(CH2 = CH1 = "0"、CH0 = "1")、A/D割込み要求許可(ADI E = "1")に設定して、A/D変換を開始(ADST = "1")します。

- (2) A/D変換が終了すると、A/D変換結果がADDRBに転送されます。同時に、ADF = "1"、ADST = "0"となり、A/D変換器は変換待機となります。

- (3) ADF = "1"、ADI E = "1"となっているため、ADI割込み要求が発生します。

- (4) A/D割込み処理ルーチンが開始されます。

- (5) ADC SRをリードした後、ADFに"0"をライトします。

- (6) A/D変換結果(ADDRB)をリードして、処理します。

- (7) A/D割込み処理ルーチンの実行を終了します。

この後、ADSTビットを“1”にセットするとA/D変換が開始され(2)～(7)を行います。

【注】 \* ↓は、ソフトウェアによる命令実行を示します。

図15.3 A/D変換器の動作例（單一モード チャネル1選択時）

#### 15.4.2 スキャンモード (S C A N = "1")

スキャンモードは、複数チャネル（1チャネルを含む）のアナログ入力を常にモニタするような応用に適しています。A／D変換はソフトウェアまたは外部トリガ入力によってA D S Tビットが“1”にセットされると、グループの第1チャネル(C H 2 = “0”的ときAN<sub>0</sub>、C H 2 = “1”的ときAN<sub>1</sub>)から開始されます。

複数のチャネルが選択されている場合は、第1チャネルの変換が終了した後、ただちに第2チャネル(AN<sub>1</sub>またはAN<sub>2</sub>)のA／D変換を開始します。

A／D変換は、A D S Tビットが“0”にクリアされるまで、選択されたチャネル内を連続して繰り返し行います。変換された結果は、各チャネルに対応したA D D Rに転送され保持されます。

A／D変換中に、モードやアナログ入力チャネルの切換えを行う場合は、誤動作を避けるためにA D C S RのA D S Tビットを“0”にクリアして、A／D変換を停止した状態で行ってください。変更した後、A D S Tビットに“1”をセットすると（モードおよびチャネルの変更とA D S Tビットのセットは、同時にできます）、第1チャネルが選択され、再びA／D変換を開始します。

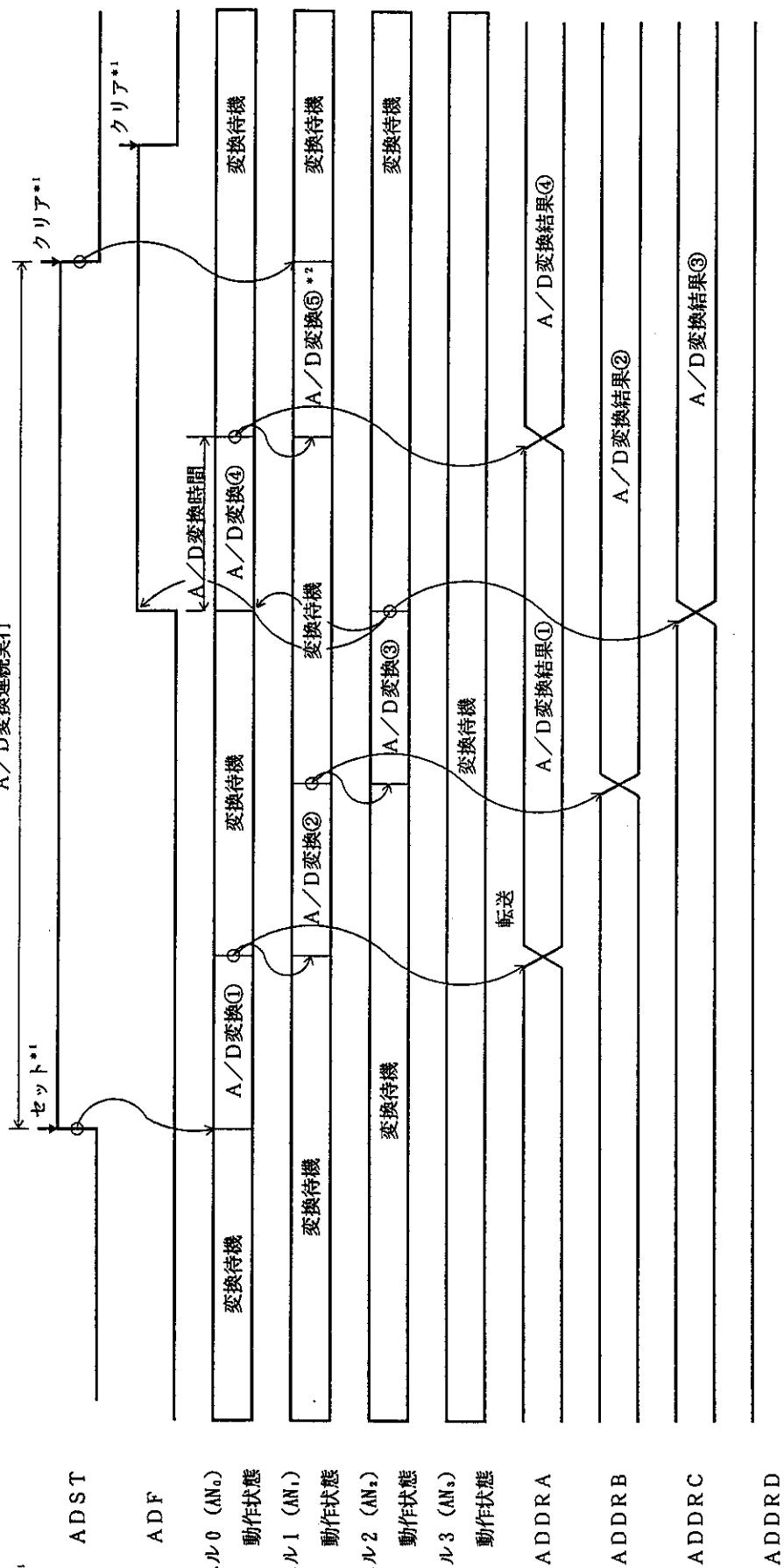

スキャンモードでグループ0の3チャネル(AN<sub>0</sub>～AN<sub>2</sub>)を選択してA／D変換を行う場合の動作例を以下に示します。また、このときの動作タイミングを図15.4に示します。

- (1) 動作モードをスキャンモードに(S C A N = "1")、スキャングループをグループ0に(C H 2 = "0")、アナログ入力チャネルをAN<sub>0</sub>～AN<sub>2</sub>(C H 1 = "1"、C H 0 = "0")に設定してA／D変換を開始(A D S T = "1")します。

- (2) 第1チャネル(AN<sub>0</sub>)のA／D変換が開始され、A／D変換が終了すると、変換結果をA D D R Aに転送します。

次に第2チャネル(AN<sub>1</sub>)が自動的に選択され、変換を開始します。

- (3) 同様に第3チャネル(AN<sub>2</sub>)まで変換を行います。

- (4) 選択されたすべてのチャネル(AN<sub>0</sub>～AN<sub>2</sub>)の変換が終了すると、A D F = "1"となり、再び第1チャネル(AN<sub>0</sub>)を選択し、変換が行われます。

このときA D I Eビットが“1”にセットされていると、A／D変換終了後、A D I割込みを発生します。

- (5) A D S Tビットが“1”にセットされている間は、(2)～(4)を繰り返します。

A D S Tビットを“0”にクリアするとA／D変換が停止します。この後、A D S Tビットを“1”にセットすると再びA／D変換を開始し、第1チャネル(AN<sub>0</sub>)から変換が行われます。

【注】 \*<sup>1</sup> クリアは、ソフトウェアによる命令実行を示します。

\*<sup>2</sup> 変換中のデータは無視されます。

図15.4 A/D変換器の動作例（スキャンモード AN<sub>0</sub>～AN<sub>3</sub>の3チャネル選択時）

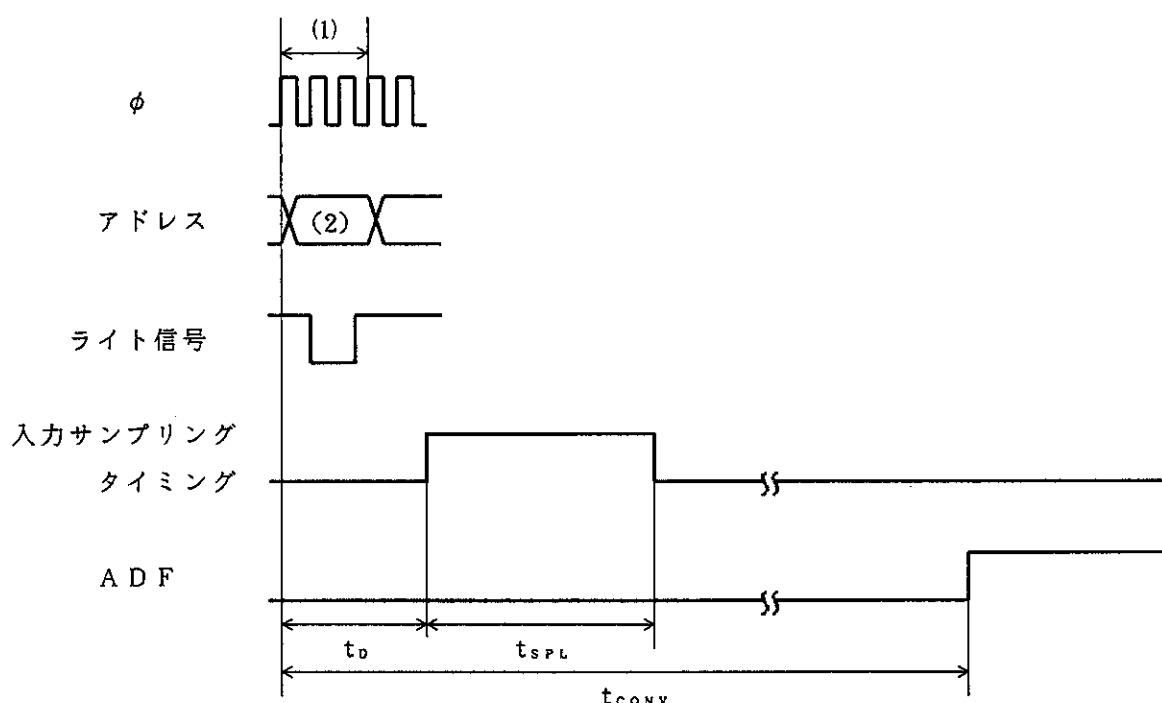

### 15.4.3 入力サンプリングとA/D変換時間

A/D変換器には、サンプル&ホールド回路が内蔵されています。A/D変換器は、ADSTビットが“1”にセットされてから $t_D$ 時間経過後、入力のサンプリングを行い、その後変換を開始します。A/D変換のタイミングを図15.5に示します。また、A/D変換時間を表15.4に示します。

A/D変換時間は、図15.5に示すように、 $t_D$ と入力サンプリング時間を持めた時間となります。ここで $t_D$ は、ADC SRへのライトタイミングにより決まり、一定値とはなりません。そのため、変換時間は表15.4に示す範囲で変化します。

スキャンモードの変換時間は、表15.4に示す値が1回目の変換時間となります。2回目以降はCKS = “0”的場合は256ステート(固定)、CKS = “1”的場合は128ステート(固定)となります。

#### 《記号説明》

(1) : ADC SRライトサイクル

(2) : ADC SRのアドレス

$t_D$  : A/D変換開始遅延時間

$t_{SPL}$  : 入力サンプリング時間

$t_{conv}$  : A/D変換時間

図15.5 A/D変換タイミング

表15.4 A/D変換時間（單一モード）

|             | 記号         | CKS = "0" |     |     | CKS = "1" |     |     |

|-------------|------------|-----------|-----|-----|-----------|-----|-----|

|             |            | min       | typ | max | min       | typ | max |

| A/D変換開始遅延時間 | $t_b$      | 10        | —   | 17  | 6         | —   | 9   |

| 入力サンプリング時間  | $t_{sPL}$  | —         | 63  | —   | —         | 31  | —   |

| A/D変換時間     | $t_{conv}$ | 259       | —   | 266 | 131       | —   | 134 |

【注】 表中の数値の単位はステートです。

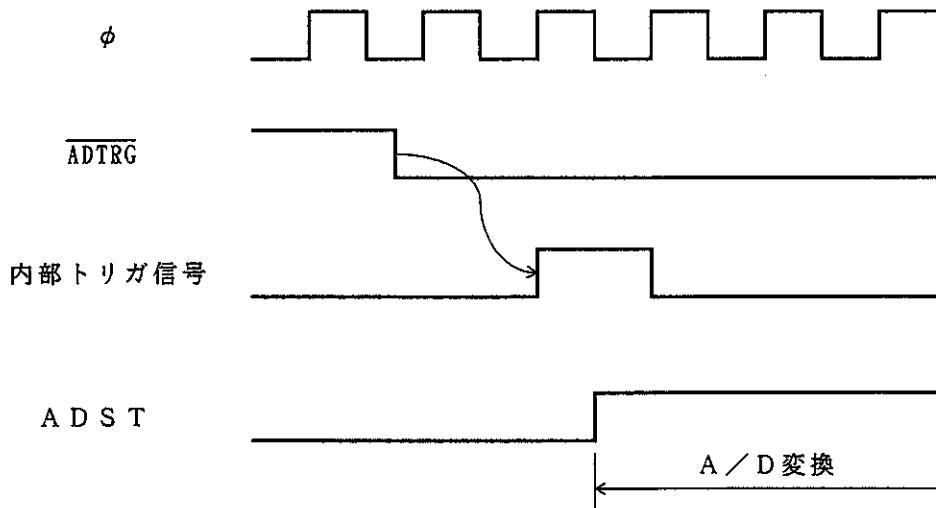

#### 15.4.4 外部トリガ入力タイミング

A/D変換は、外部トリガ入力により開始することも可能です。外部トリガ入力は、ADC\_RのTRGEビットが“1”にセットされているとき、ADTRG端子から入力されます。ADTRG入力端子の立下がりエッジで、ADC\_SRのADSTビットが“1”にセットされ、A/D変換が開始されます。

その他の動作は、單一モード／スキャンモードによらず、ソフトウェアによってADSTビットを“1”にセットした場合と同じです。

このタイミングを図15.6に示します。

図15.6 外部トリガ入力タイミング

## 15.5 割込み

A/D変換器は、A/D変換の終了により、A/D変換終了割込み（A D I）を発生します。ADI割込み要求は、ADC S RのA D I E ビットで許可／禁止することができます。

## 15.6 使用上の注意

A/D変換器を使用する際は、以下のことに注意してください。

### (1) アナログ入力電圧の範囲

A/D変換中、アナログ入力端子AN<sub>n</sub>に印加する電圧はAV<sub>ss</sub>≤AN<sub>n</sub>≤V<sub>REF</sub>の範囲としてください。

### (2) AV<sub>cc</sub>、AV<sub>ss</sub>とV<sub>cc</sub>、V<sub>ss</sub>の関係

AV<sub>cc</sub>、AV<sub>ss</sub>とV<sub>cc</sub>、V<sub>ss</sub>との関係は、AV<sub>ss</sub>=V<sub>ss</sub>とし、さらに、A/D変換器を使用しないときも、AV<sub>cc</sub>、AV<sub>ss</sub>端子を決してオープンにしないでください。

### (3) V<sub>REF</sub>の設定範囲

V<sub>REF</sub>端子によるリファレンス電圧の設定範囲はV<sub>REF</sub>≤AV<sub>cc</sub>にしてください。

### (4) アナログ電源電圧について

A/D変換器を使用する場合、電源電圧を以下の関係に従って設定してください。

$$(1) V_{cc} \geq AV_{cc}-0.3V$$

$$(2) AV_{cc} \geq V_{REF} \geq AN_n \geq AV_{ss} = V_{ss}$$

(n=0~7)

【注】Z T A T版のみの制限事項です。Z T A TのSマスク版、フラッシュメモリ版およびマスクROM版では通常の使用が可能であり、制限はありません。

以上(1)、(2)、(3)、(4)のことが守られない場合、LSIの信頼性に悪影響を及ぼすことがあります。

### (5) ボード設計上の注意

ボード設計時には、デジタル回路とアナログ回路ができるだけ分離してレイアウトしてください。また、デジタル回路の信号配線とアナログ回路の信号配線を交差させたり、近接させるようなレイアウトは極力避けてください。誘導などにより、アナログ回路の誤動作や、A/D変換値に悪影響を及ぼします。

なお、アナログ入力信号(AN<sub>0</sub>~<sub>7</sub>)、アナログ基準電源(V<sub>REF</sub>)、アナログ電源(AV<sub>cc</sub>)は、アナログ・グランド(AV<sub>ss</sub>)で、デジタル回路を必ず分離してください。さらに、アナログ・グランド(AV<sub>ss</sub>)は、ボード上の安定したデジタル・グランド(V<sub>ss</sub>)に一点接続してください。

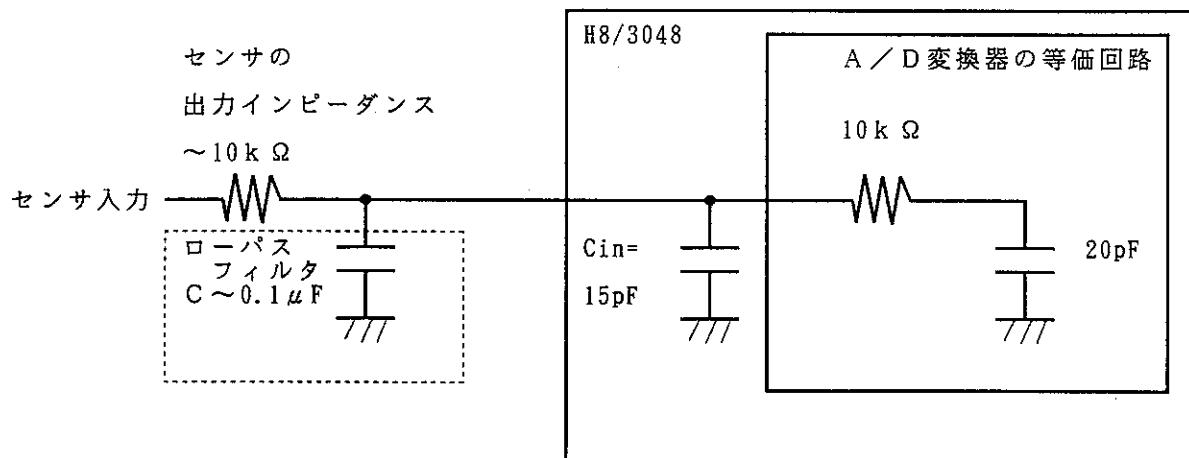

#### (6) ノイズ対策上の注意

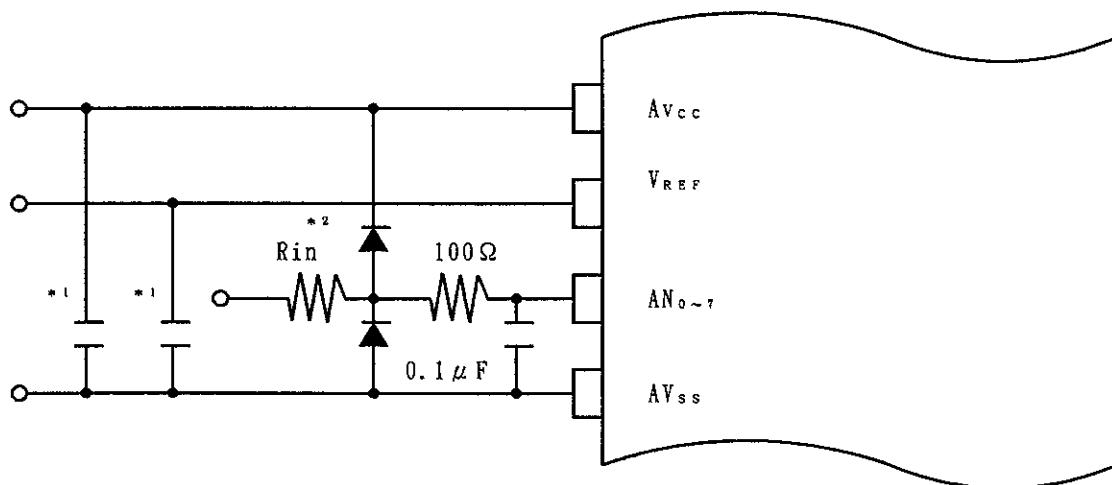

アナログ入力端子 ( $AN_0 \sim _7$ )、アナログ基準電源 ( $V_{REF}$ )に、過大なサージなど異常電圧による破壊を防ぐために接続する保護回路は、図15.7に示すように  $AV_{cc} - AV_{ss}$  間に接続してください。

また、 $AV_{cc}$ 、 $V_{REF}$ に接続するバイパス・コンデンサ、 $AN_0 \sim _7$ に接続するフィルタのコンデンサは、必ず  $AV_{ss}$  に接続してください。

なお、図15.7のようにフィルタ用のコンデンサを接続するとアナログ入力端子 ( $AN_0 \sim _7$ ) の入力電流が平均化されるため、誤差を生じることがあります。また、スキャンモード等で頻繁に A/D 変換を行う場合、A/D 変換器内部のサンプル&ホールド回路の容量に充放電される電流が入力インピーダンス ( $R_{in}$ ) を経由して入力される電流を上回るとアナログ入力端子の電圧に誤差を生じます。したがって回路定数の決定については、十分ご検討くださいますようお願いいたします。

【注】 数値は参考値です。

\*<sup>2</sup>  $R_{in}$ :入力インピーダンス

図15.7 アナログ入力保護回路の例

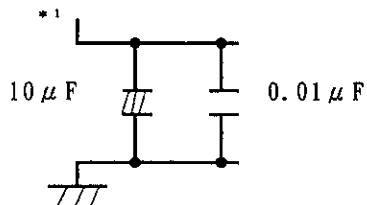

表15.5 アナログ端子の規格

| 項目           | min | max | 単位 |

|--------------|-----|-----|----|

| アナログ入力容量     | —   | 20  | pF |

| 許容信号源インピーダンス | —   | 10* | kΩ |

\*  $V_{cc} = 4.0 \sim 5.5V$ 、 $\phi \leq 12MHz$  の場合

【注】 数値は参考値です。

図15.8 アナログ入力端子等価回路

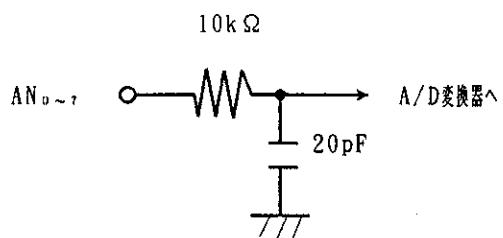

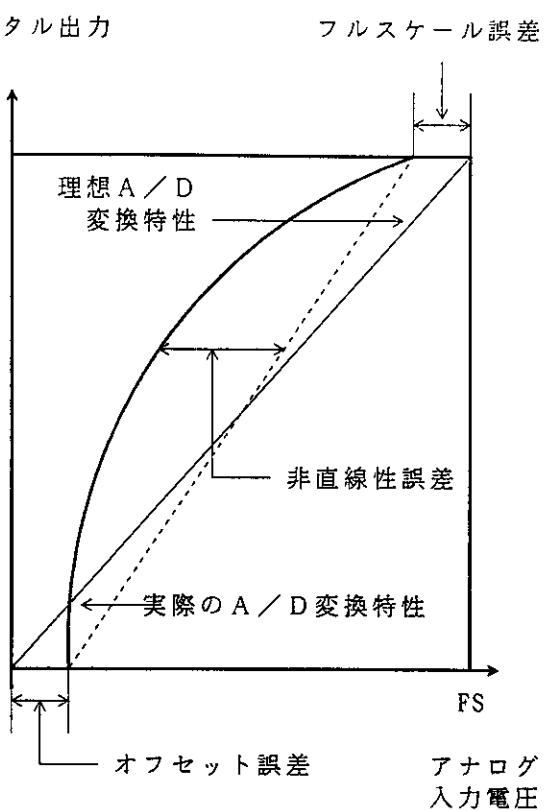

(7) A／D変換精度の定義：

以下に、H 8／3048シリーズのA／D変換精度の定義を示します。

- ・分解能……………A／D変換器のデジタル出力コード数

- ・オフセット誤差…………デジタル出力が最小電圧値0000000000から0000000001に変化するときの

アナログ入力電圧値の理想A／D変換特性からの偏差（図15.10）

- ・フルスケール誤差…デジタル出力が1111111110から1111111111に変化するときのアナログ入

力電圧値の理想A／D変換特性からの偏差（図15.10）

- ・量子化誤差…………A／D変換器が本質的に有する偏差であり、 $1/2$  LSBで与えられる

（図15.9）

- ・非直線性誤差…………ゼロ電圧からフルスケール電圧までの間の理想A／D変換特性からの誤

差。ただし、オフセット誤差、フルスケール誤差、量子化誤差を含まな

い。

- ・絶対精度……………デジタル値とアナログ入力値との偏差。オフセット誤差、フルスケール

誤差、量子化誤差および非直線誤差を含む。

デジタル出力

デジタル出力

図 15.9 A/D 変換精度の定義(1)

図 15.10 A/D 変換精度の定義(2)

#### (8) 許容信号源インピーダンスについて

H8/3048のアナログ入力は、信号源インピーダンスが $10\text{ k}\Omega$ 以下の入力信号に対し、変換精度が保証される設計となっております。これはA/D変換器のサンプル&ホールド回路の入力容量をサンプリング時間内に充電するために設けている規格で、センサの出力インピーダンスが $10\text{ k}\Omega$ を越える場合充電不足が生じ、A/D変換精度が保証できなくなる場合があります。

単一モードで変換を行う場合で外部に大容量を設けている場合、入力の負荷は実質的に内部入力抵抗の $10\text{ k}\Omega$ だけになりますので信号源インピーダンスは不問となります。

ただし、この場合ローパスフィルターとなりますので、微分係数の大きなアナログ信号（例えば電圧の変動率が $5\text{ mV}/\mu\text{s}$ 以上）には追従できない場合があります（図15.11）。

高速のアナログ信号を変換する場合や、スキャンモードで変換を行う場合には、低インピーダンスのバッファを入れてください。

#### (9) 絶対精度への影響について

容量を付加するとにより、GNDとのカップリングを受けることになりますので、GNDにノイズがあると絶対精度が悪化する可能性があります。必ずAV<sub>ss</sub>等の電気的に安定なGNDに接続してください。

またフィルター回路が実装基板上でデジタル信号と干渉したり、アンテナとならないように注意が必要です。

図15.11 アナログ入力回路の例