# 16. D/A 変換器

16

## 第16章 目次

|                                    |     |

|------------------------------------|-----|

| 16.1 概要                            | 599 |

| 16.1.1 特長                          | 599 |

| 16.1.2 ブロック図                       | 599 |

| 16.1.3 端子構成                        | 600 |

| 16.1.4 レジスタ構成                      | 600 |

| 16.2 各レジスタの説明                      | 601 |

| 16.2.1 D/Aデータレジスタ0、1 (DADR0、DADR1) | 601 |

| 16.2.2 D/Aコントロールレジスタ (DACR)        | 601 |

| 16.2.3 D/Aスタンバイコントロールレジスタ (DASTCR) | 603 |

| 16.3 動作説明                          | 604 |

| 16.4 D/A出力制御                       | 605 |

| 16.5 使用上の注意                        | 605 |

## 16.1 概要

H 8 / 3048 シリーズには 2 チャネルの D / A 変換器が内蔵されています。

### 16.1.1 特長

D / A 変換器の特長を以下に示します。

- 8 ビットの分解能

- 2 チャネル出力

- 変換時間最大  $10\mu s$  (負荷容量  $20\text{pF}$  時)

- 出力電圧  $0\text{V} \sim V_{REF}$

- ソフトウェアスタンバイ時の D / A 出力保持機能

### 16.1.2 ブロック図

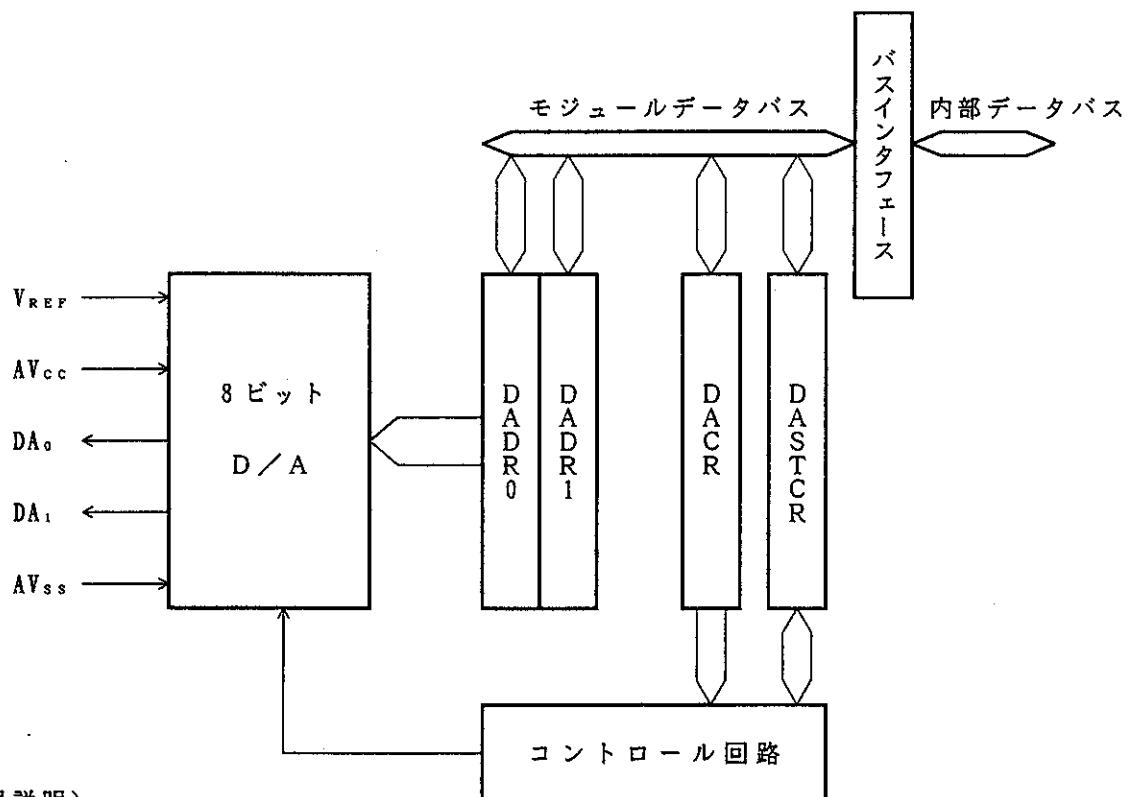

D / A 変換器のブロック図を図16.1に示します。

〈記号説明〉

- D A C R : D / A コントロールレジスタ

- D A D R 0 : D / A データレジスタ 0

- D A D R 1 : D / A データレジスタ 1

- D A S T C R : D / A スタンバイコントロールレジスタ

図16.1 D / A 変換器のブロック図

### 16.1.3 端子構成

D/A変換器で使用する入出力端子を表16.1に示します。

表16.1 端子構成

| 端子名        | 略称               | 入出力 | 機能                |

|------------|------------------|-----|-------------------|

| アナログ電源端子   | AV <sub>cc</sub> | 入力  | アナログ部の電源および基準電圧   |

| アナロググランド端子 | AV <sub>ss</sub> | 入力  | アナログ部のグランドおよび基準電圧 |

| アナログ出力端子0  | DA <sub>0</sub>  | 出力  | チャネル0のアナログ出力      |

| アナログ出力端子1  | DA <sub>1</sub>  | 出力  | チャネル1のアナログ出力      |

| リファレンス電圧端子 | V <sub>REF</sub> | 入力  | アナログ部の基準電圧        |

### 16.1.4 レジスタ構成

D/A変換器でレジスタ構成を表16.2に示します。

表16.2 レジスタ構成

| アドレス*  | 名 称                | 略 称    | R/W | 初期値  |

|--------|--------------------|--------|-----|------|

| H'FFDC | D/Aデータレジスタ0        | DADR0  | R/W | H'00 |

| H'FFDD | D/Aデータレジスタ1        | DADR1  | R/W | H'00 |

| H'FFDE | D/Aコントロールレジスタ      | DACR   | R/W | H'1F |

| H'FF5C | D/Aスタンバイコントロールレジスタ | DASTCR | R/W | H'FE |

【注】\* アドレスの下位16ビットを示します。

## 16.2 各レジスタの説明

### 16.2.1 D/Aデータレジスタ0、1 (DADR0、1)

|      |     |     |     |     |     |     |     |     |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| ビット: | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 初期値: | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W: | R/W |

D/Aデータレジスタ0、1 (DADR0、1) は、変換を行うデータを格納するリード/ライト可能な8ビットのレジスタです。

アナログ出力を許可すると、DADRの値が常に変換され、アナログ出力端子に出力されます。

DADRは、リセットまたはスタンバイモード時に、H'00にイニシャライズされます。

### 16.2.2 D/Aコントロールレジスタ (DACR)

|      |       |       |     |          |                  |                         |                         |   |

|------|-------|-------|-----|----------|------------------|-------------------------|-------------------------|---|

| ビット: | 7     | 6     | 5   | 4        | 3                | 2                       | 1                       | 0 |

|      | DAOE1 | DAOE0 | DAE | —        | —                | —                       | —                       | — |

| 初期値: | 0     | 0     | 0   | 1        | 1                | 1                       | 1                       | 1 |

| R/W: | R/W   | R/W   | R/W | —        | —                | —                       | —                       | — |

|      |       |       |     | D/Aイネーブル |                  |                         |                         |   |

|      |       |       |     |          | D/A変換を制御するビットです。 |                         |                         |   |

|      |       |       |     |          | D/Aアウトプットイネーブル0  |                         |                         |   |

|      |       |       |     |          |                  | D/A変換とアナログ出力を制御するビットです。 |                         |   |

|      |       |       |     |          |                  | D/Aアウトプットイネーブル1         |                         |   |

|      |       |       |     |          |                  |                         | D/A変換とアナログ出力を制御するビットです。 |   |

DACRは、8ビットのリード/ライト可能なレジスタで、D/A変換器の動作を制御します。

DACRは、リセットまたはスタンバイモード時に、H'1Fにイニシャライズされます。

#### ビット7:D/Aアウトプットイネーブル1 (DAOE1)

D/A変換とアナログ出力を制御します。

| ビット7  | 説明                                       |

|-------|------------------------------------------|

| DAOE1 |                                          |

| 0     | アナログ出力DA <sub>1</sub> を禁止                |

| 1     | チャネル1のD/A変換を許可。アナログ出力DA <sub>1</sub> を許可 |

### ビット6:D/Aアウトプットイネーブル0(DAOE0)

D/A変換とアナログ出力を制御します。

| ビット6  | 説明                                       |

|-------|------------------------------------------|

| DAOE0 |                                          |

| 0     | アナログ出力DA <sub>0</sub> を禁止                |

| 1     | チャネル0のD/A変換を許可。アナログ出力DA <sub>0</sub> を許可 |

### ビット5:D/Aイネーブル(DAE)

DAOE0、DAOE1とともに、D/A変換を制御します。DAEビットが“0”にクリアされているときチャネル0、1のD/A変換は独立に制御され、DAEビットが“1”にセットされているときチャネル0、1のD/A変換は一括して制御されます。

変換結果を出力するか否かは、DAOE0、DAOE1により、常に独立に制御されます。

| ビット7  | ビット6  | ビット5 | 説明                               |

|-------|-------|------|----------------------------------|

| DAOE1 | DAOE0 | DAE  |                                  |

| 0     | 0     | -    | チャネル0、1のD/A変換を禁止                 |

| 0     | 1     | 0    | チャネル0のD/A変換を許可<br>チャネル1のD/A変換を禁止 |

| 0     | 1     | 1    | チャネル0、1のD/A変換を許可                 |

| 1     | 0     | 0    | チャネル0のD/A変換を禁止<br>チャネル1のD/A変換を許可 |

| 1     | 0     | 1    | チャネル0、1のD/A変換を許可                 |

| 1     | 1     | -    | チャネル0、1のD/A変換を許可                 |

DAEビットを“1”にセットすると、DACRのDAOE0、1ビット、ADCSCRのADSTビットが“0”にクリアされていても、アナログ電源電流はA/D、D/A変換中と同等になります。

### ビット4～0：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

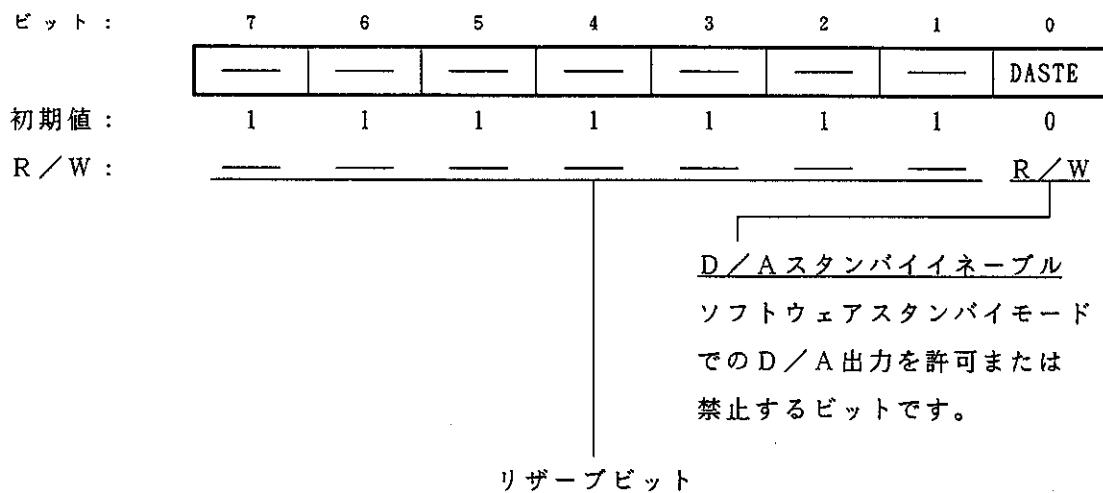

### 16.2.3 D/Aスタンバイコントロールレジスタ (DASTCR)

DASTCRは8ビットのリード/ライト可能なレジスタで、ソフトウェアスタンバイモードでのD/Aの出力を許可または禁止します。

DASTCRはリセット、またはハードウェアスタンバイモード時に、H'FEにイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

#### ビット7～1：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット0：D/Aスタンバイイネーブル (DASTE)

ソフトウェアスタンバイモードでのD/A出力を許可または禁止します。

| ビット0  | 説明                       |       |

|-------|--------------------------|-------|

| DASTE |                          |       |

| 0     | ソフトウェアスタンバイモードでのD/A出力を禁止 | (初期値) |

| 1     | ソフトウェアスタンバイモードでのD/A出力を許可 |       |

## 16.3 動作説明

D/A変換器は、2チャネルのD/A変換回路を内蔵し、それぞれ独立に変換を行うことができます。

DACRによってD/A変換が許可されている期間は常にD/A変換が行われています。DADR0、1を書き換えるとただちに、新しいデータが変換されます。DAOE0、1ビットを“1”にセットすることにより、変換結果が出力されます。

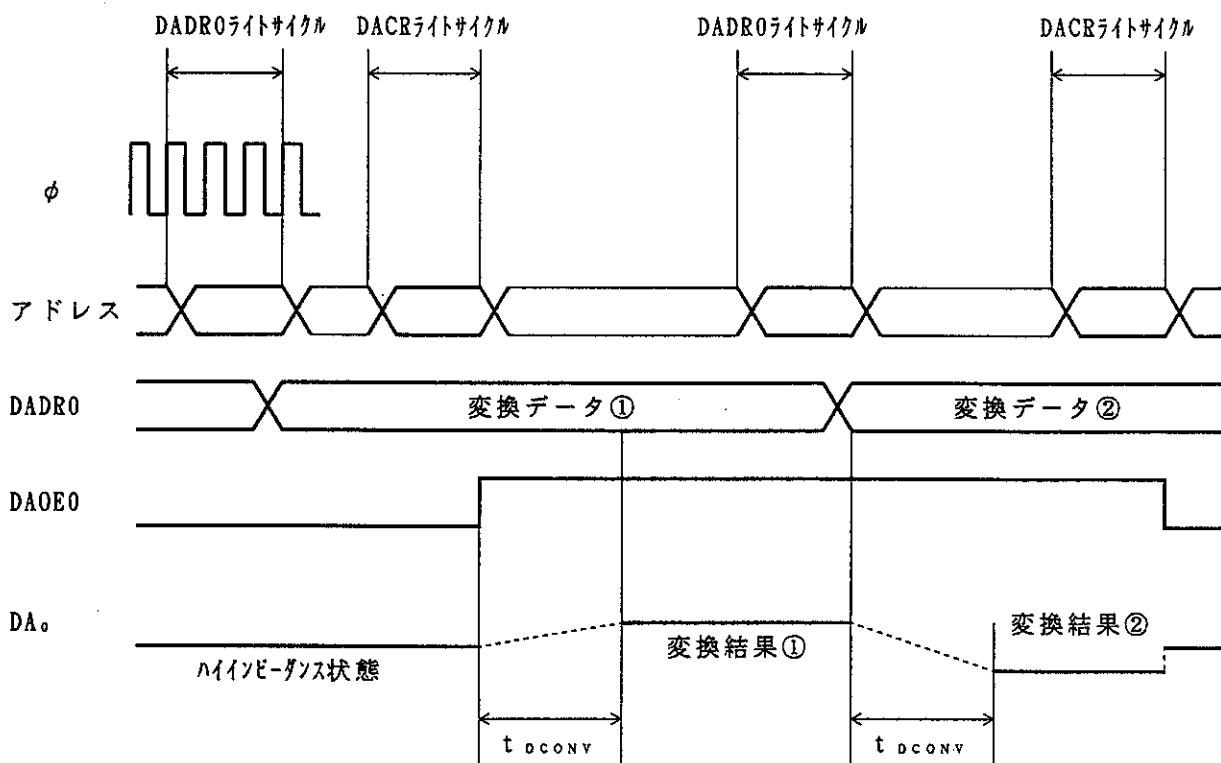

チャネル0のD/A変換を行う場合の動作例を示します。動作タイミングを図16.2に示します。

- (1) DADR0に変換データをライトします。

- (2) DACRのDAOE0ビットを“1”にセットします。D/A変換が開始され、DA0端子が

出力端子になります。変換時間経過後に変換結果が出力されます。出力値は  $\frac{\text{DADRの内容}}{256} \times V_{REF}$

です。

- 次にDADR0を書き換えるか、DAOE0ビットを“0”にクリアするまでこの変換結果が

出力され続けます。

- (3) DADR0を書き換えるとただちに変換が開始されます。変換時間経過後に変換結果が出力さ

れます。

- (4) DAOE0ビットを“0”にクリアすると、DA0端子は入力端子になります。

〈記号説明〉

$t_{DCONV}$  : D/A変換時間

図16.2 D/A変換器の動作例

## 16.4 D/A 出力制御

H8/3048シリーズは、ソフトウェアスタンバイモードでD/A変換器の出力を許可または禁止することができます。

DASTCRのDASTEビットを“1”にセットすると、ソフトウェアスタンバイモードにおいてもD/A変換器の出力が許可されます。このとき、D/A変換器のレジスタはソフトウェアスタンバイモードに遷移する直前の値を保持します。

なお、ソフトウェアスタンバイモードでD/A出力を許可した場合、リファレンス電源電流は動作時と同じとなります。

## 16.5 使用上の注意

D/A変換器を使用する際は、以下のことに注意してください。

### ■アナログ電源電圧について

D/A変換器を使用する場合は、電源電圧を以下の関係に従って設定してください。

- (1)  $V_{cc} \geq A_{Vcc} - 0.3\text{ V}$

- (2)  $A_{Vcc} \geq V_{ref} \geq A_{Nn} \geq A_{Vss} = V_{ss}$

( $n = 0 \sim 7$ )

【注】ZTAT版のみの制限事項です。ZTATのSマスク版、フラッシュメモリ版およびマスクROM版では、通常の使用が可能であり制限はありません。