# 17. RAM

1

---

## 第17章 目次

|                             |     |

|-----------------------------|-----|

| 17.1 概要                     | 609 |

| 17.1.1 ブロック図                | 609 |

| 17.1.2 レジスタ構成               | 610 |

| 17.2 システムコントロールレジスタ (SYSCR) | 611 |

| 17.3 動作説明                   | 612 |

---

## 17.1 概要

H8/3048、H8/3047は4kバイト、H8/3044、H8/3045は2kバイトのスタティックRAMを内蔵しています。RAMはCPUと16ビット幅のデータバスで接続されており、アクセスはバイトデータ、ワードデータにかかわらず2ステートで行われます。したがって、データの高速転送が可能です。

H8/3048、H8/3047の内蔵RAMは、モード1、2、5、7のときH'FEF10～H'FFF0Fに、モード3、4、6のときH'FFEF10～H'FFFF0Fに割り当てられています。

H8/3044、H8/3045の内蔵RAMは、モード1、2、5、7のときH'FF710～H'FFF0Fに、モード3、4、6のときH'FFF710～H'FFFF0Fに割り当てられています。システムコントロールレジスタ(SYSCR)のRAMイネーブル(RAME)ビットにより内蔵RAM有効／無効の制御を行います。

### 17.1.1 ブロック図

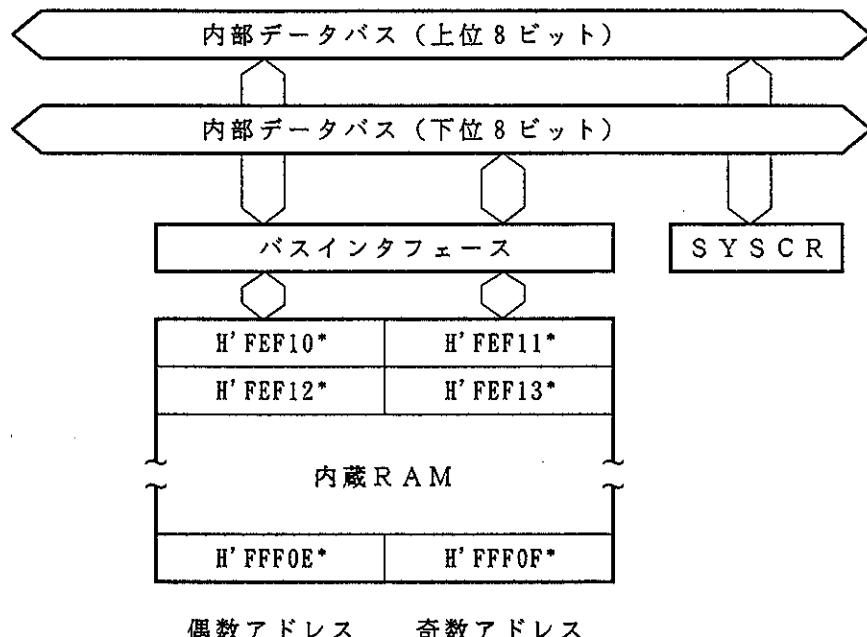

RAMのブロック図を図17.1に示します。

#### 《記号説明》

SYSCR : システムコントロールレジスタ

【注】\* アドレスは下位20ビットを示しています。また、H8/3048、モード7の場合の例を示しています。

図17.1 RAMのブロック図

## 17.1.2 レジスタ構成

内蔵RAMは、SYSCTRで制御されます。

SYSCTRのアドレスと初期値を表17.1に示します。

表17.1 レジスタ構成

| アドレス*  | 名 称            | 略 称    | R/W | 初期値  |

|--------|----------------|--------|-----|------|

| H'FFF2 | システムコントロールレジスタ | SYSCTR | R/W | H'0B |

【注】\* アドレスは下位16ビットを示しています。

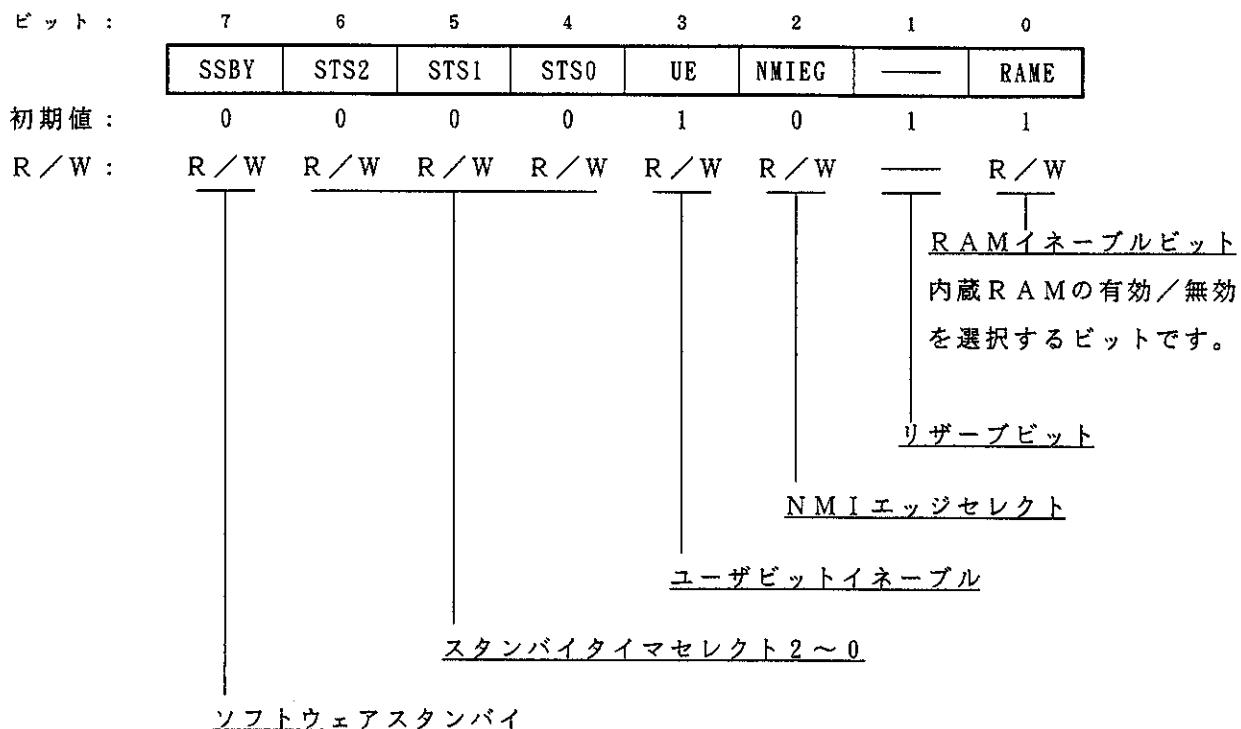

## 17.2 システムコントロールレジスタ (SYSCR)

SYSCRは、内蔵RAMへのアクセスを許可／禁止するレジスタです。内蔵RAMはSYSCRのRAMEビットにより有効／無効が選択されます。なお、SYSCRのその他のビットについての詳細は「3.3 システムコントロールレジスタ」を参照してください。

### ビット0: RAMイネーブル (RAME)

内蔵RAMの有効または無効を選択します。RAMEビットはRES端子の立上がりエッジでイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

| ビット0 | 説       | 明     |

|------|---------|-------|

| RAME |         |       |

| 0    | 内蔵RAM無効 |       |

| 1    | 内蔵RAM有効 | (初期値) |

### 17.3 動作説明

RAMEビットを“1”にセットすると内蔵RAMが有効になります。H8／3048、H8／3047では、モード1、2、5、7のときH'FEF10～H'FFF0Fを、モード3、4、6のときH'FFEF10～H'FFFF0Fをアクセスすると内蔵RAMがアクセスされます。H8／3044、H8／3045では、モード1、2、5、7のときH'FF710～H'FFF0Fを、モード3、4、6のときH'FFF710～H'FFFF0Fをアクセスすると内蔵RAMがアクセスされます。また、モード1～6（拡張モード）ではRAM Eビットが“0”にクリアされているときは、外部アドレス空間がアクセスされます。モード7（シングルチップモード）では、RAMEビットが“0”にクリアされているときは、内蔵RAMはアクセスされません。リードすると常にH'FFがリードされ、ライトは無効です。

RAMはCPUと内部16ビットデータバスで接続されており、ワード単位のリード／ライトが可能です。また、バイト単位のリード／ライトも可能です。

バイトデータは、データバス上位8ビットを使い2ステートでアクセスされ、また、偶数番地から始まるワードデータはデータバス16ビットを使い2ステートでアクセスできます。