# 19. クロック発振器

19

## 第19章 目次

|                                  |     |

|----------------------------------|-----|

| 19.1 概要                          | 695 |

| 19.1.1 ブロック図                     | 695 |

| 19.2 発振器                         | 696 |

| 19.2.1 水晶発振子を接続する方法              | 696 |

| 19.2.2 外部クロックを入力する方法             | 698 |

| 19.3 デューティ補正回路                   | 701 |

| 19.4 プリスケーラ                      | 701 |

| 19.5 分周器                         | 701 |

| 19.5.1 レジスタ構成                    | 701 |

| 19.5.2 分周比コントロールレジスタ (D I V C R) | 701 |

| 19.5.3 使用上の注意                    | 702 |

## 19.1 概要

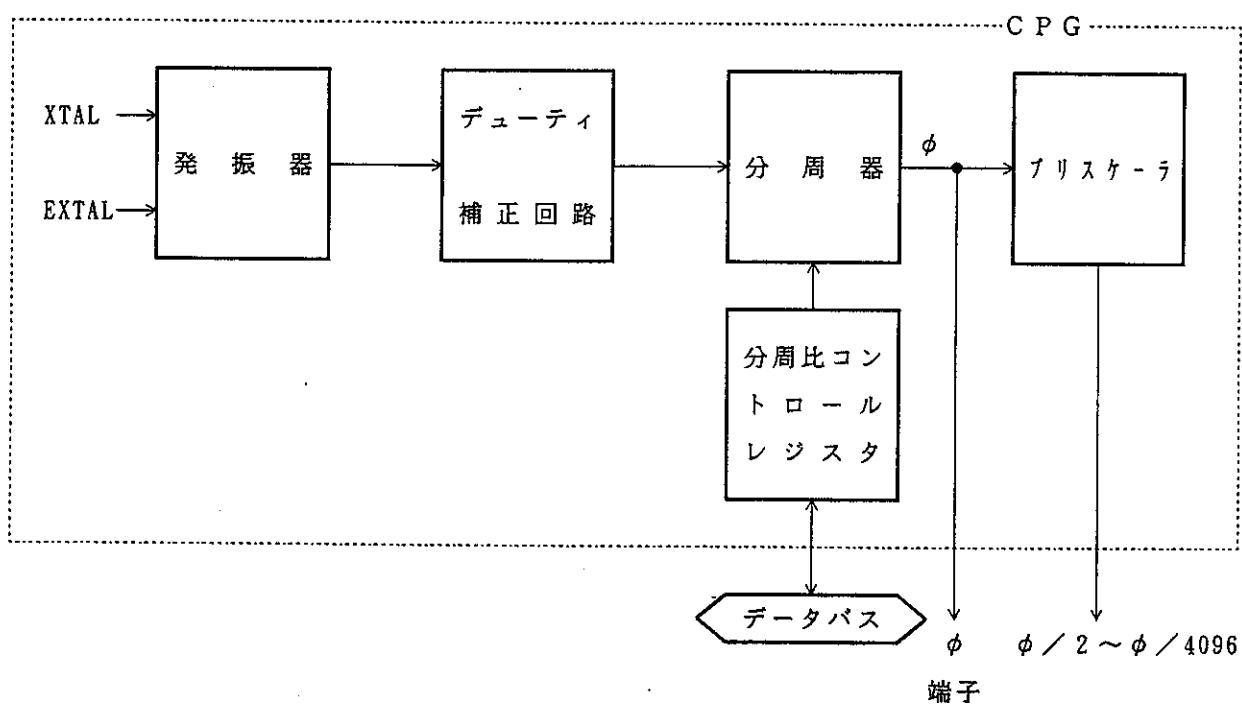

本LSIは、クロック発振器(CPG : Clock Pulse Generator)を内蔵しており、クロック発振器はシステムクロック( $\phi$ )、および内部クロック( $\phi/2 \sim \phi/4096$ )を生成します。

分周器は、デューティ補正されたクロックを分周してシステムクロック( $\phi$ )を生成します。 $\phi$ は $\phi$ 端子に出力される<sup>\*</sup>とともに内部モジュールへクロックを供給するプリスケーラの基本クロックとなります。なお、分周器の分周比は分周比コントロールレジスタ(DIVCR)により $1/1$ 、 $1/2$ 、 $1/4$ 、 $1/8$ の中から選択できます<sup>\*\*</sup>。チップ内の消費電流は分周比にはほぼ比例して低減します。

### 19.1.1 ブロック図

図19.1にクロック発振器のブロック図を示します。

図19.1 クロック発振器のブロック図

【注】<sup>\*</sup>  $\phi$ 端子の状態はチップの動作モードおよびモジュールスタンバイコントロールレジスタ(MSTCR)のPSTOPの設定により異なります。詳細は「20.7  $\phi$ クロック出力禁止機能」を参照してください。

<sup>\*\*</sup> 分周比の変更は動作中ダイナミックに変更することができます。 $\phi$ 端子のクロック出力も分周比を変更することにより変化します。このとき $\phi$ 端子から出力される周波数は、以下のようになります。

$$\phi = \text{EXTAL} \times n \quad \text{EXTAL : 水晶発振子または外部クロックの周波数}$$

$$n : \text{分周比 } (n = 1/1, 1/2, 1/4, 1/8)$$

## 19.2 発振器

クロックを供給する方法には、水晶発振子を接続する方法と外部クロックを入力する方法の2つがあります。

### 19.2.1 水晶発振子を接続する方法

#### (1) 回路構成

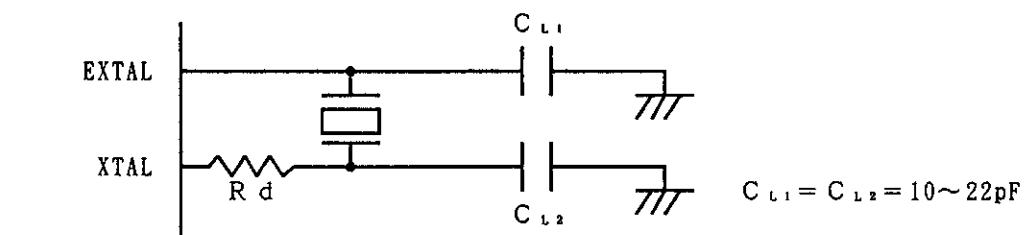

水晶発振子を接続する場合の接続例を図19.2に示します。ダンピング抵抗 $R_d$ は、表19.1に示すものを使用してください。また、水晶発振子は、ATカット並列共振形を使用してください。

図19.2 水晶発振子を接続する場合の接続例

表19.1 ダンピング抵抗値

| ダンピング抵抗値           |                        | 周波数 $f$ (Hz) |                |                |                 |                  |                  |                  |

|--------------------|------------------------|--------------|----------------|----------------|-----------------|------------------|------------------|------------------|

|                    |                        | 2            | $2 < f \leq 4$ | $4 < f \leq 8$ | $8 < f \leq 10$ | $10 < f \leq 13$ | $13 < f \leq 16$ | $16 < f \leq 18$ |

| $R_d$ ( $\Omega$ ) | 下記 <sup>*1</sup> 製品に適用 | 1 k          | 500            | 200            | 0               | 0                | 0                | 0                |

|                    | HD64F3048              | 1 k          | 1 k            | 500            | 200             | 100              | 0                | /                |

【注】 水晶発振子は、2MHz～18MHz(フラッシュメモリ版では2MHz～16MHz)が使用できます。

2MHz未満で動作させる場合は、内蔵の分周器を使用してください。(2MHz未満の水晶発振子は使用できません)

\*1 HD6473048, HD6433048, HD6433047, HD6433045, HD6433044

## (2) 水晶発振子

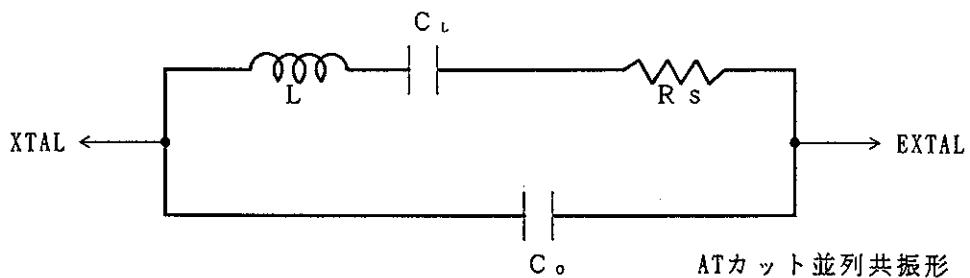

図19.3に水晶発振子の等価回路を示します。水晶発振子は表19.2に示す特性のものを使用してください。

図19.3 水晶発振子の等価回路

表19.2 水晶発振子のパラメータ

| 周波数 (MHz)              | 2        | 4   | 8  | 10 | 12 | 16 | 18 |

|------------------------|----------|-----|----|----|----|----|----|

| R <sub>s</sub> max (Ω) | 500      | 120 | 80 | 70 | 60 | 50 | 40 |

| C <sub>o</sub> (pF)    | 7 pF max |     |    |    |    |    |    |

水晶発振子は、 $\omega$ と同一の周波数のものを使用してください。

## (3) ボード設計上の注意

水晶発振子を接続して発振させる場合、次の点に注意してください。

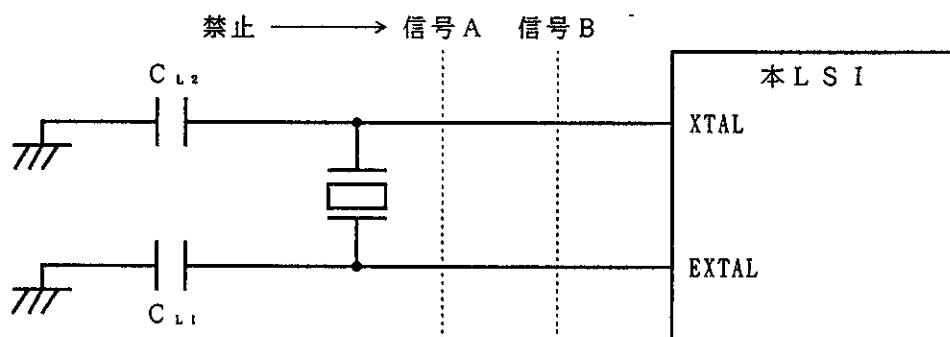

発振回路部の近くで信号線を通過させないでください。誘導により正しい発振ができなくなる場合があります（図19.4）。

また、ボード設計に際しては、水晶発振子および負荷容量はできるだけXTAL、EXTAL端子の近くに配置してください。

図19.4 発振回路部のボード設計に関する注意事項

## 19.2.2 外部クロックを入力する方法

### (1) 回路構成

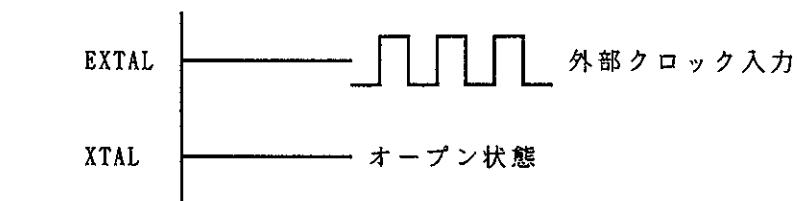

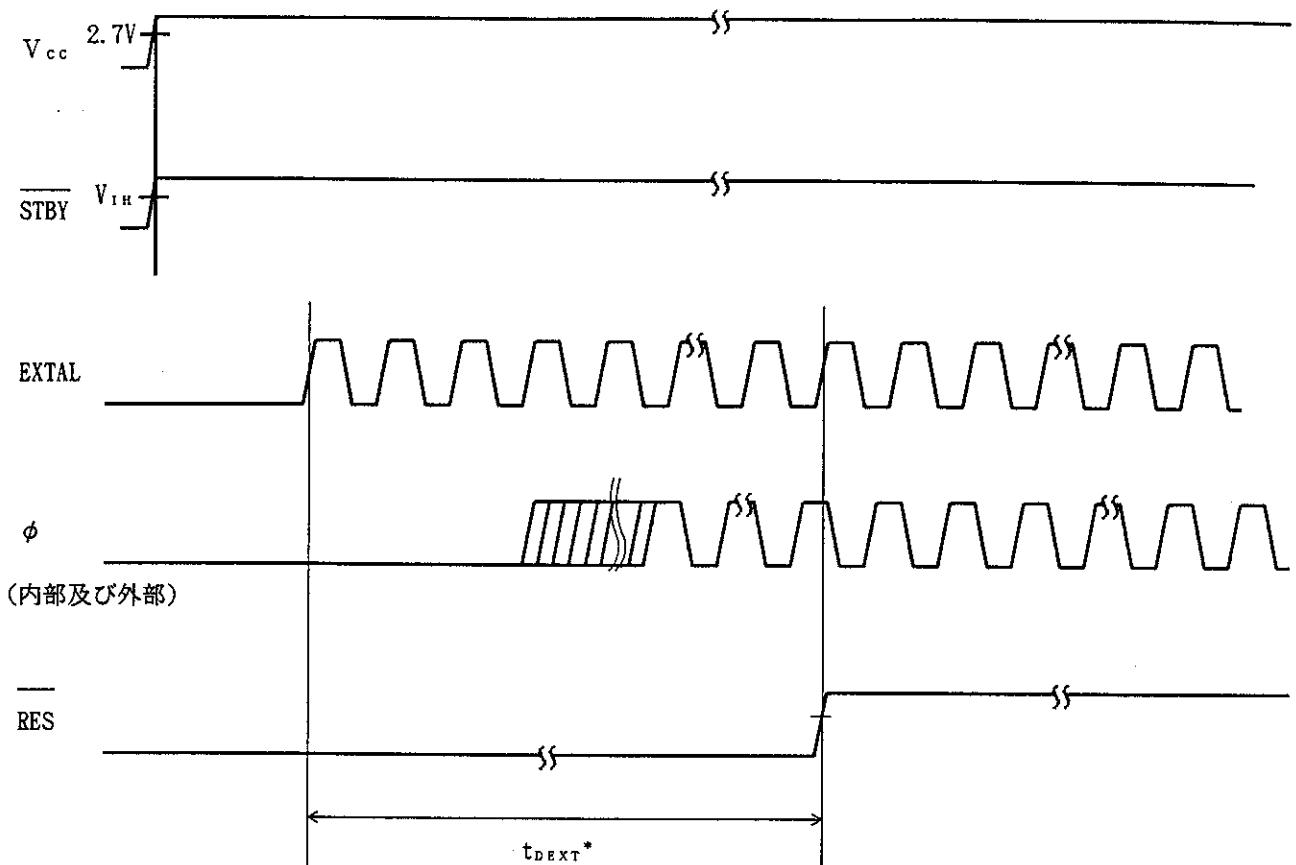

外部クロック入力の接続例を図19.5に示します。XTAL端子をオープン状態にする場合は、XTAL端子の寄生容量は10pF以下としてください。XTAL端子の寄生容量が10pFを越える場合は(b)のように接続し、スタンバイモード時には外部クロックが“High”レベルとなるようにしてください。

(a) XTAL端子をオープンにする接続例

(b) XTAL端子に逆相クロックを入力する接続例

図19.5 外部クロックを入力する場合の接続例

### (2) 外部クロック

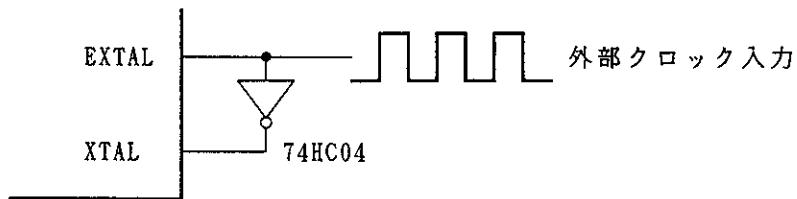

外部クロックの周波数は、分周器によって分周しないときの周波数と同一にしてください。表19.3にクロックタイミング、図19.6に外部クロック入力タイミングを示します。

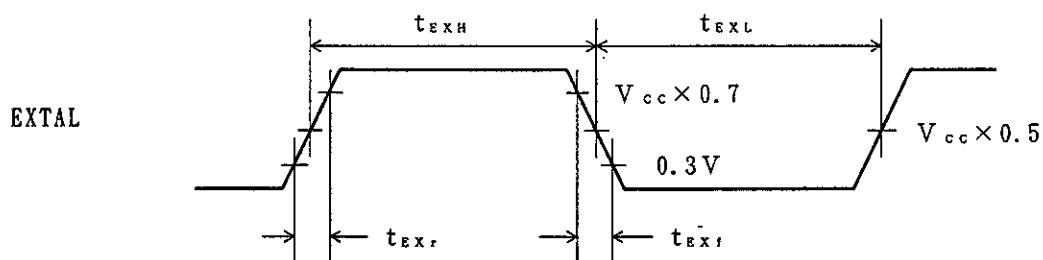

図19.7に外部クロック出力安定遅延時間タイミングを示します。発振器とデューティ補正回路は、EXTAL端子に入力した外部クロック入力の波形を調整する機能持っています。

EXTAL端子に規定のクロック信号を入力すると、外部クロック出力安定遅延時間( $t_{d_{ext}}$ )経過後に内部のクロック信号出力が確定します。 $t_{d_{ext}}$ 期間中はクロック信号出力が確定していないので、リセット信号を“Low”にし、リセット状態に保持してください。

表19.3 クロックタイミング

| 項目                        | 記号           | $V_{cc} = 2.7 \sim 5.5V$ |     | $V_{cc} = 5.0V \pm 10\%$ |     | 単位            | 測定条件                      |  |

|---------------------------|--------------|--------------------------|-----|--------------------------|-----|---------------|---------------------------|--|

|                           |              | min                      | max | min                      | max |               |                           |  |

| 外部クロック入力<br>パルス幅“Low”レベル  | $t_{exL}$    | 40                       | —   | 20                       | —   | ns            | 図19.6                     |  |

| 外部クロック入力<br>パルス幅“High”レベル | $t_{exH}$    | 40                       | —   | 20                       | —   | ns            |                           |  |

| 外部クロック<br>立上がり時間          | $t_{exr}$    | —                        | 10  | —                        | 5   | ns            |                           |  |

| 外部クロック<br>立下がり時間          | $t_{exf}$    | —                        | 10  | —                        | 5   | ns            |                           |  |

| クロックパルス幅<br>“Low”レベル      | $t_{clL}$    | 0.4                      | 0.6 | 0.4                      | 0.6 | $t_{cyc}$     | $\phi \geq 5 \text{ MHz}$ |  |

|                           |              | 80                       | —   | 80                       | —   | ns            | $\phi < 5 \text{ MHz}$    |  |

| クロックパルス幅<br>“High”レベル     | $t_{chH}$    | 0.4                      | 0.6 | 0.4                      | 0.6 | $t_{cyc}$     | $\phi \geq 5 \text{ MHz}$ |  |

|                           |              | 80                       | —   | 80                       | —   | ns            | $\phi < 5 \text{ MHz}$    |  |

| 外部クロック<br>出力安定遅延時間        | $t_{DEXT}^*$ | 500                      | —   | 500                      | —   | $\mu\text{s}$ | 図19.7                     |  |

【注】\* :  $t_{DEXT}$ は、RES パルス幅 ( $t_{RESW}$ ) を10  $t_{cyc}$  含みます。

図19.6 外部クロック入力タイミング

【注】\* :  $t_{DEXT}$ は、RES パルス幅 ( $t_{RESW}$ ) を $10 t_{cyc}$  含みます。

図19.7 外部クロック出力安定遅延時間タイミング

### 19.3 デューティ補正回路

デューティ補正回路は、周波数 5 MHz 以上の発振に対し発振器からのクロックのデューティを補正し、 $\phi$ を生成します。

### 19.4 プリスケーラ

プリスケーラは、 $\phi$ を分周し内部クロック ( $\phi/2 \sim \phi/4096$ ) を生成します。

### 19.5 分周器

分周器はデューティ補正されたクロックを分周して $\phi$ を生成します。分周比は以下に説明する D I V C R の値を書き換えることにより動作中ダイナミックに変更できます。チップ内の消費電流は分周比にはほぼ比例して低減します。また分周器で生成した $\phi$ は $\phi$ 端子より出力することができます。

#### 19.5.1 レジスタ構成

表19.4に分周器のレジスタ構成を示します。

表19.4 分周器のレジスタ構成

| アドレス*  | 名 称           | 略 称       | R/W | 初期値  |

|--------|---------------|-----------|-----|------|

| H'FF5D | 分周比コントロールレジスタ | D I V C R | R/W | H'FC |

【注】\* アドレスの下位16ビットを示しています。

#### 19.5.2 分周比コントロールレジスタ (D I V C R)

D I V C R は 8 ビットのリード/ライト可能なレジスタで分周器の分周比を選択します。

| ビット : | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

|       | — | — | — | — | — | — | DIV1 | DIV0 |

| 初期値 : | 1 | 1 | 1 | 1 | 1 | 1 | 0    | 0    |

| R/W : | — | — | — | — | — | — | R/W  | R/W  |

リザーブビット

分周比ビット 1, 0

分周比を設定するビットです。

D I V C R はリセットまたはハードウェアスタンバイモード時に H'FC にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

#### ビット7～2：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット1、0：分周比(DIV1、0)

分周比を選択します。DIV1、0ビットと分周比の関係は以下のとおりです。

| ビット1<br>DIV1 | ビット0<br>DIV0 | 分周比 |       |

|--------------|--------------|-----|-------|

| 0            | 0            | 1/1 | (初期値) |

| 0            | 1            | 1/2 |       |

| 1            | 0            | 1/4 |       |

| 1            | 1            | 1/8 |       |

#### 19.5.3 使用上の注意

DIVCRの設定により $\phi$ の周波数が変わりますので、以下の点に注意してください。

- (1) 分周比は電気的特性のACタイミングのクロックサイクル時間 $t_{cyc}$ の動作保証範囲内におさまるように選択してください。すなわち $\phi_{min} = 1\text{MHz}$ とし、 $\phi < 1\text{MHz}$ とならないように注意してください。

- (2) 内部モジュールは、全て $\phi$ を基準に動作します。

このため、分周比変更の前後でタイマやSCIなどの時間処理が変わりますので注意してください。

またソフトウェアスタンバイ解除時の待機時間も分周比を変更することで変わります。詳細は「20.4.3 ソフトウェアスタンバイモード解除後の発振安定待機時間の設定」を参照してください。