# 20. 低消費電力状態

## 第20章 目次

20

|                                      |     |

|--------------------------------------|-----|

| 20.1 概要                              | 705 |

| 20.2 レジスタ構成                          | 707 |

| 20.2.1 システムコントロールレジスタ (SYSCR)        | 707 |

| 20.2.2 モジュールスタンバイコントロールレジスタ (MSTCR)  | 709 |

| 20.3 スリープモード                         | 712 |

| 20.3.1 スリープモードへの遷移                   | 712 |

| 20.3.2 スリープモードの解除                    | 712 |

| 20.4 ソフトウェアスタンバイモード                  | 713 |

| 20.4.1 ソフトウェアスタンバイモードへの遷移            | 713 |

| 20.4.2 ソフトウェアスタンバイモードの解除             | 713 |

| 20.4.3 ソフトウェアスタンバイモード解除後の発振安定待機時間の設定 | 714 |

| 20.4.4 ソフトウェアスタンバイモードの応用例            | 715 |

| 20.4.5 使用上の注意                        | 715 |

| 20.5 ハードウェアスタンバイモード                  | 716 |

| 20.5.1 ハードウェアスタンバイモードへの遷移            | 716 |

| 20.5.2 ハードウェアスタンバイモードの解除             | 716 |

| 20.5.3 ハードウェアスタンバイモードのタイミング          | 716 |

| 20.6 モジュールスタンバイモード機能                 | 717 |

| 20.6.1 モジュールスタンバタイトミング               | 717 |

| 20.6.2 モジュールスタンバイ中のリード／ライト           | 717 |

| 20.6.3 使用上の注意                        | 717 |

| 20.7 クロック出力禁止機能                      | 718 |

## 20.1 概要

H8/3048シリーズには、C P U機能を停止して消費電力を著しく低下させる低消費電力状態および、内蔵モジュールの機能を選択的に停止させることにより消費電力を低減させるモジュールスタンバイ機能があります。

低消費電力状態には、次の3種類のモードがあります。

- (1) スリープモード

- (2) ソフトウェアスタンバイモード

- (3) ハードウェアスタンバイモード

モジュールスタンバイ機能は低消費電力状態とは独立に内蔵モジュールのうち、I T U、S C I 0、S C I 1、D M A C、リフレッシュコントローラ、A／D変換器を停止させることができます。

各モードへ遷移する条件とC P Uや周辺機能などの状態、および各モードの解除方法を表20.1に示します。

表20.1 低消費電力狀態

| モード            | 遷移条件                          | 状態   |     |      |                  |                  |                  |      |      |      |      | 解除方法 |     |                          |                                                                           |

|----------------|-------------------------------|------|-----|------|------------------|------------------|------------------|------|------|------|------|------|-----|--------------------------|---------------------------------------------------------------------------|

|                |                               | クロック | CPU | レジスタ | DIMAC            | リフリッシュメモリ        | I/O              | SC10 | SC11 | A/D  | 電源機能 | RAM  | φ出力 | I/Oポート                   |                                                                           |

| スリープモード        | SYSSCRのSSBY=“0”的状態でSLEEP命令を実行 | 動作   | 停止  | 保持   | 動作               | 動作               | 動作               | 動作   | 動作   | 動作   | 動作   | 動作   | 保持  | 保持                       | ・割込み<br>・RES端子<br>・STBY端子                                                 |

| ソフトウェアスタンバイモード | SYSSCRのSSBY=“1”的状態でSLEEP命令を実行 | 停止   | 停止  | 保持   | 停止               | 停止               | 停止               | リセット | リセット | リセット | リセット | リセット | 停止  | “High”出力                 | ・NMI端子<br>・IRQ <sub>0</sub> ～<br>IRQ <sub>7</sub> 端子<br>・RES端子<br>・STBY端子 |

| ハードウェアスタンバイモード | STBY端子を“Low”レベル               | 停止   | 停止  | 不定   | 停止               | リセット             | リセット             | リセット | リセット | リセット | リセット | リセット | 停止  | 停止                       | ・STBY端子<br>・RES端子                                                         |

| モジュールスタンバイ機能   | MSTCRの該当ビットを“1”にセット           | 動作   | 動作  | —    | 停止 <sup>*2</sup> | 停止 <sup>*2</sup> | 停止 <sup>*2</sup> | リセット | リセット | リセット | リセット | リセット | 動作  | 停止 <sup>*2</sup><br>リセット | ・STBY端子<br>・RES端子<br>・MSTCRの<br>該当ビットを<br>“0”リセット                         |

【注】\*1 DTCNT DTMCSBT7 64ビットライブキーワードは既に実装されています。

\*2 RICN1、RICN2、RIMCSRのビット1、0はオーナーシャドウされ、その他は保持となります。

\*3 MSTCRの該当するビットを“1”にセットした状態です。詳細は「20.2.2 モジュールスタンバイコントロールレジスタ(MSTCR)」を参照してください。

ノログラム実効状態に達する場合には、事前に **SYS-CRAME** ビットを “0” にクリアする必要があります。**MSTCR** の各ビットを “1” にセットすると該当する周辺モジュールのレジスタは初期化されます。したがって周辺モジュールを再起動する場合は **MSTCR** の該当ビットを “0” にクリア後レジスタの再設定を行ってください。

《記号說明》

SYSSCR：システムコントロールレジスター

トビラ・バーンバウアーズ

S S B I : フラントリエヌベランバウヒトロールレジスター

M S T C R : モジュールスタルバンバイコントロールレジスター

## 20.2 レジスタ構成

本LSIには低消費電力状態の制御を行うシステムコントロールレジスタ(SYSCR)とモジュールスタンバイ機能の制御を行うモジュールスタンバイコントロールレジスタ(MSTCR)があります。レジスタ構成を表20.2に示します。

表20.2 レジスタ構成

| アドレス*  | 名 称                  | 略 称   | R/W | 初期値  |

|--------|----------------------|-------|-----|------|

| H'FFF2 | システムコントロールレジスタ       | SYSCR | R/W | H'0B |

| H'FF5E | モジュールスタンバイコントロールレジスタ | MSTCR | R/W | H'40 |

【注】\* アドレスの下位16ビットを示しています。

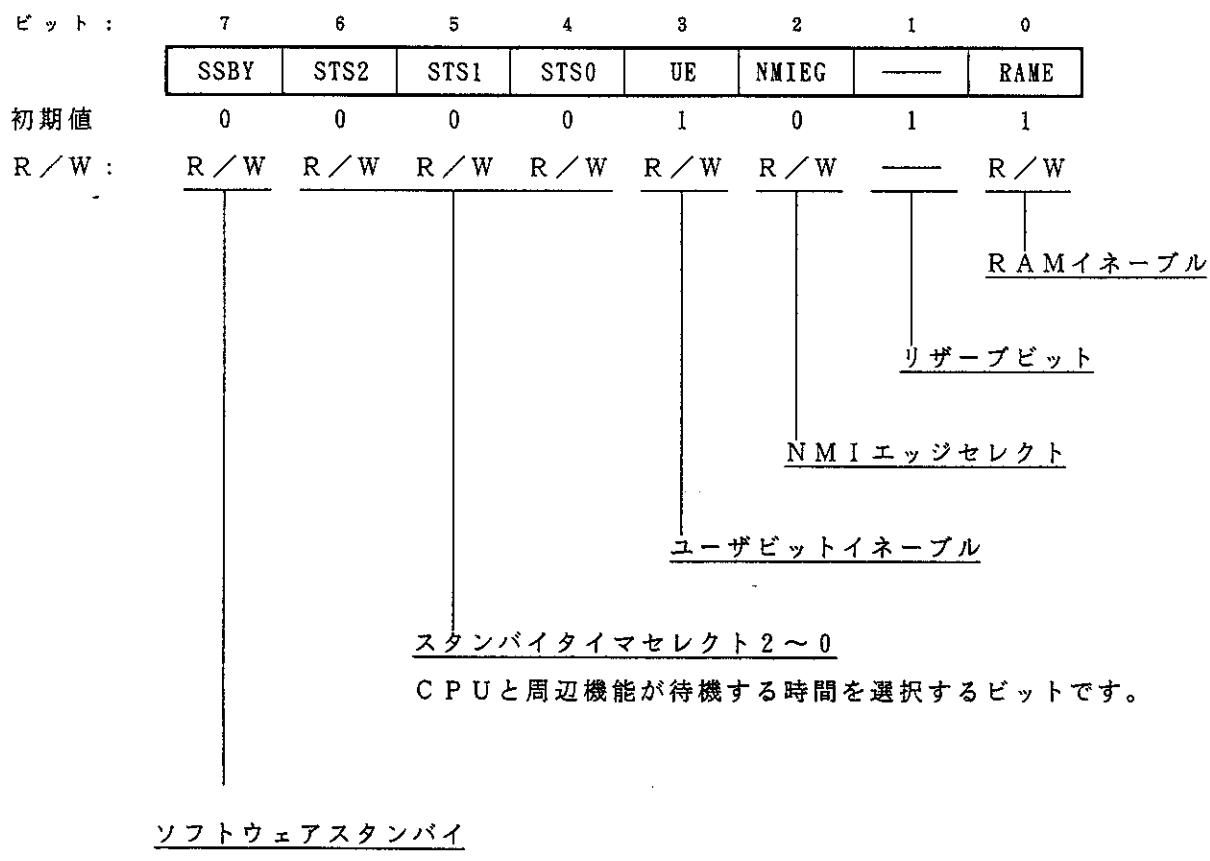

### 20.2.1 システムコントロールレジスタ(SYSCR)

SYSCRは8ビットのリード/ライト可能なレジスタで、ビット7のSSBYビットとビット6~4のSTS2~STS0ビットにより低消費電力状態の制御を行います。なお、SYSCRの他のビットについての詳細は「3.3 システムコントロールレジスタ」を参照してください。

### ビット7：ソフトウェアスタンバイ (S S B Y)

ソフトウェアスタンバイモードへの遷移を指定します。

なお、外部割込みによりソフトウェアスタンバイモードが解除され、通常動作に遷移したときこのビットは“1”にセットされたままです。クリアする場合は、“0”をライトしてください。

| ビット7    | 説明                                |       |

|---------|-----------------------------------|-------|

| S S B Y |                                   |       |

| 0       | S L E E P 命令実行後、スリープモードに遷移        | (初期値) |

| 1       | S L E E P 命令実行後、ソフトウェアスタンバイモードに遷移 |       |

### ビット6～4：スタンバイタイマセレクト2～0 (S T S 2～0)

外部割込みによって、ソフトウェアスタンバイモードを解除する場合に、クロックが安定するまでC P Uと周辺機能が待機する時間を選択します。水晶発振の場合、表20.3を参照し動作周波数に応じて待機時間が7ms(発振安定時間)以上となるように選択してください。外部クロックの場合、任意の選択が可能です。

| ビット6    | ビット5    | ビット4    | 説明                    |

|---------|---------|---------|-----------------------|

| S T S 2 | S T S 1 | S T S 0 |                       |

| 0       | 0       | 0       | 待機時間 = 8192ステート (初期値) |

| 0       | 0       | 1       | 待機時間 = 16384ステート      |

| 0       | 1       | 0       | 待機時間 = 32768ステート      |

| 0       | 1       | 1       | 待機時間 = 65536ステート      |

| 1       | 0       | 0       | 待機時間 = 131072ステート     |

| 1       | 0       | 1       | 待機時間 = 1024ステート       |

| 1       | 1       | —       | 使用禁止                  |

## 20.2.2 モジュールスタンバイコントロールレジスタ (M S T C R)

M S T C R は、 8 ビットのリード／ライト可能なレジスタです。 φクロック出力の制御を行い、また、内蔵モジュールをモジュールごとにスタンバイ状態にするモジュールスタンバイ機能を設定します。モジュールスタンバイ機能を設定できるモジュールは、 I T U 、 S C I 0 、 S C I 1 、 D M A C 、リフレッシュコントローラ、 A ／ D 変換器です。

| ビット :   | 7     | 6 | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|-------|---|--------|--------|--------|--------|--------|--------|

| R / W : | PSTOP | — | MSTOP5 | MSTOP4 | MSTOP3 | MSTOP2 | MSTOP1 | MSTOP0 |

| 初期値     | 0     | 1 | 0      | 0      | 0      | 0      | 0      | 0      |

|         | R / W | — | R / W  | R / W  | R / W  | R / W  | R / W  | R / W  |

|         |       |   |        |        |        |        |        |        |

モジュールスタンバイ 5 ~ 0

モジュールをスタンバイ状態に

するための選択ビットです。

リザーブビット

φクロックストップ

φクロックの出力を許可

または禁止するビットです。

M S T C R はリセット、またはハードウェアスタンバイモード時に、H'40にイニシャライズされます。ソフトウェアスタンバイモードではイニシャライズされません。

### ビット 7 : φクロックストップ (P S T O P)

φクロックの出力を許可または禁止します。

| ビット 1     | 説明          | 明     |

|-----------|-------------|-------|

| P S T O P |             |       |

| 0         | φクロックの出力を許可 | (初期値) |

| 1         | φクロックの出力を禁止 |       |

### ビット 6 : リザーブビット

リザーブビットです。リードすると常に “1” が読み出されます。ライトは無効です。

**ビット 5 : モジュールスタンバイ 5 (MSTOP 5)**

I T U をスタンバイ状態にするかを選択します。

| ビット 5   | 説明             |

|---------|----------------|

| MSTOP 5 |                |

| 0       | I T U は通常動作    |

| 1       | I T U はスタンバイ状態 |

**ビット 4 : モジュールスタンバイ 4 (MSTOP 4)**

S C I 0 をスタンバイ状態にするかを選択します。

| ビット 4   | 説明               |

|---------|------------------|

| MSTOP 4 |                  |

| 0       | S C I 0 は通常動作    |

| 1       | S C I 0 はスタンバイ状態 |

**ビット 3 : モジュールスタンバイ 3 (MSTOP 3)**

S C I 1 をスタンバイ状態にするかを選択します。

| ビット 3   | 説明               |

|---------|------------------|

| MSTOP 3 |                  |

| 0       | S C I 1 は通常動作    |

| 1       | S C I 1 はスタンバイ状態 |

**ビット 2 : モジュールスタンバイ 2 (MSTOP 2)**

D M A C をスタンバイ状態にするかを選択します。

| ビット 2   | 説明               |

|---------|------------------|

| MSTOP 2 |                  |

| 0       | D M A C は通常動作    |

| 1       | D M A C はスタンバイ状態 |

**ビット1：モジュールスタンバイ1（MSTOP1）**

リフレッシュコントローラをスタンバイ状態にするかを選択します。

| ビット1   | 説明                         |

|--------|----------------------------|

| MSTOP1 |                            |

| 0      | リフレッシュコントローラは通常動作<br>(初期値) |

| 1      | リフレッシュコントローラはスタンバイ状態       |

**ビット0：モジュールスタンバイ0（MSTOP0）**

A/D変換器をスタンバイ状態にするかを選択します。

| ビット0   | 説明                   |

|--------|----------------------|

| MSTOP0 |                      |

| 0      | A/D変換器は通常動作<br>(初期値) |

| 1      | A/D変換器はスタンバイ状態       |

## 20.3 スリープモード

### 20.3.1 スリープモードへの遷移

S Y S C R の S S B Y ビットを“0”にクリアした状態で S L E E P 命令を実行すると、プログラム実行状態からスリープモードに遷移します。C P U の動作は、S L E E P 命令実行直後に停止します。C P U の動作は停止しますが、C P U のレジスタの内容は保持されます。スリープモードではD M A コントローラ（D M A C）、リフレッシュコントローラ、および内蔵周辺モジュールの機能は停止しません。ただし、モジュールスタンバイ機能により、スタンバイ状態となっている内蔵モジュールの機能は動作しません。

### 20.3.2 スリープモードの解除

スリープモードの解除は、割込み、RES端子、STBY端子によって行われます。

#### (1) 割込みによる解除

割込み要求が発生すると、割込み例外処理状態に遷移し、スリープモードは解除されます。なお、内蔵周辺モジュールによる割込みがモジュール側で禁止されている場合、また、N M I 以外の割込みがC C R の I 、U I ビット、I P R によってマスクされている場合にはスリープモードは解除されません。

#### (2) RES端子による解除

RES端子を“Low”レベルにするとリセット状態に遷移し、スリープモードは解除されます。

#### (3) STBY端子による解除

STBY端子を“Low”レベルにすると、ハードウェアスタンバイモードに遷移します。

## 20.4 ソフトウェアスタンバイモード

### 20.4.1 ソフトウェアスタンバイモードへの遷移

ソフトウェアスタンバイモードに遷移するにはSYSCRのSSBYビットを“1”にセットした状態で、SLEEP命令を実行します。

ソフトウェアスタンバイモードでは、CPUだけでなくクロックをはじめ内蔵周辺モジュールの機能が停止するため、消費電力は著しく低減されます。DMAC、内蔵周辺モジュールはリセット状態になり、停止します。規定の電圧が与えられている限り、CPUのレジスタ、および内蔵RAMのデータは保持されます。I/Oポートおよびリフレッシュコントローラ\*の状態も保持されています。

【注】\* RTCNT、RTMCSRのビット7、6はイニシャライズされ、その他は保持となります。

### 20.4.2 ソフトウェアスタンバイモードの解除

ソフトウェアスタンバイモードの解除は、外部割込み(NMI端子、IRQ<sub>0</sub>～IRQ<sub>15</sub>端子)、RES端子、またはSTBY端子によって行われます。

#### (1) 割込みによる解除

NMI、IRQ<sub>0</sub>～IRQ<sub>15</sub>割込み要求信号が入力されると、クロックの発振が開始され、SYSCRのSTS2～STS0ビットによって設定された時間が経過した後、安定したクロックが本LSI全体に供給されて、ソフトウェアスタンバイモードは解除され、割込み例外処理を開始します。なお、IRQ<sub>0</sub>～IRQ<sub>15</sub>割込みは、対応するイネーブルビットが“0”にクリアされている場合、またはCPUでマスクされている場合には、ソフトウェアスタンバイモードは解除されません。

#### (2) RES端子による解除

RES端子を“Low”レベルにすると、クロックの発振が開始されます。クロックの発振開始と同時に、本LSI全体にクロックが供給されます。このときRES端子は必ずクロックの発振が安定するまで“Low”レベルに保持してください。RES端子を“High”レベルにすると、CPUはリセット例外処理を開始します。

#### (3) STBY端子による解除

STBY端子を“Low”レベルにすると、ハードウェアスタンバイモードに遷移します。

### 20.4.3 ソフトウェアスタンバイモード解除後の発振安定待機時間の設定

SYSCRのSTS2～STS0ビットおよびDIVCRのDIV1、0ビットの設定は、以下のようにしてください。

#### (1) 水晶発振の場合

待機時間が7ms（発振安定時間）以上となるようにSTS2～STS0、DIV1、0を設定してください。

表20.3は動作周波数とSTS2～STS0、DIV1、0ビットの設定値に対する待機時間を示します。

#### (2) 外部クロックの場合

任意の値を選択可能です。

表20.3 動作周波数と発振安定待機時間

| DIV1 | DIV0 | STS2 | STS1 | STS0 | 待機時間       | 18MHz | 16MHz | 12MHz | 10MHz | 8MHz  | 6MHz  | 4MHz  | 2MHz  | 1MHz   | 単位 |

|------|------|------|------|------|------------|-------|-------|-------|-------|-------|-------|-------|-------|--------|----|

| 0    | 0    | 0    | 0    | 0    | 8192ステート   | 0.46  | 0.51  | 0.65  | 0.8   | 1.0   | 1.3   | 2.0   | 4.1   | 8.2    | ms |

|      |      | 0    | 0    | 1    | 16384ステート  | 0.91  | 1.0   | 1.3   | 1.6   | 2.0   | 2.7   | 4.1   | 8.2   | 16.4   |    |

|      |      | 0    | 1    | 0    | 32768ステート  | 1.8   | 2.0   | 2.7   | 3.3   | 4.1   | 5.5   | 8.2   | 16.4  | 32.8   |    |

|      |      | 0    | 1    | 1    | 65536ステート  | 3.6   | 4.1   | 5.5   | 6.6   | 8.2   | 10.9  | 16.4  | 32.8  | 65.5   |    |

|      |      | 1    | 0    | 0    | 131072ステート | 7.3   | 8.2   | 10.9  | 13.1  | 16.4  | 21.8  | 32.8  | 65.5  | 131.1  |    |

|      |      | 1    | 0    | 1    | 1024ステート   | 0.057 | 0.064 | 0.085 | 0.10  | 0.13  | 0.17  | 0.26  | 0.51  | 1.0    |    |

|      |      | 1    | 1    | —    | 使用禁止       |       |       |       |       |       |       |       |       |        |    |

| 0    | 1    | 0    | 0    | 0    | 8192ステート   | 0.91  | 1.02  | 1.4   | 1.6   | 2.0   | 2.7   | 4.1   | 8.2   | 16.4   | ms |

|      |      | 0    | 0    | 1    | 16384ステート  | 1.8   | 2.0   | 2.7   | 3.3   | 4.1   | 5.5   | 8.2   | 16.4  | 32.8   |    |

|      |      | 0    | 1    | 0    | 32768ステート  | 3.6   | 4.1   | 5.5   | 6.6   | 8.2   | 10.9  | 16.4  | 32.8  | 65.5   |    |

|      |      | 0    | 1    | 1    | 65536ステート  | 7.3   | 8.2   | 10.9  | 13.1  | 16.4  | 21.8  | 32.8  | 65.5  | 131.1  |    |

|      |      | 1    | 0    | 0    | 131072ステート | 14.6  | 16.4  | 21.8  | 26.2  | 32.8  | 43.7  | 65.5  | 131.1 | 262.1  |    |

|      |      | 1    | 0    | 1    | 1024ステート   | 0.11  | 0.13  | 0.17  | 0.20  | 0.26  | 0.34  | 0.51  | 1.0   | 2.0    |    |

|      |      | 1    | 1    | —    | 使用禁止       |       |       |       |       |       |       |       |       |        |    |

| 1    | 0    | 0    | 0    | 0    | 8192ステート   | 1.8   | 2.0   | 2.7   | 3.3   | 4.1   | 5.5   | 8.2   | 16.4  | 32.8   | ms |

|      |      | 0    | 0    | 1    | 16384ステート  | 3.6   | 4.1   | 5.5   | 6.6   | 8.2   | 10.9  | 16.4  | 32.8  | 65.5   |    |

|      |      | 0    | 1    | 0    | 32768ステート  | 7.3   | 8.2   | 10.9  | 13.1  | 16.4  | 21.8  | 32.8  | 65.5  | 131.1  |    |

|      |      | 0    | 1    | 1    | 65536ステート  | 14.6  | 16.4  | 21.8  | 26.2  | 32.8  | 43.7  | 65.5  | 131.1 | 262.1  |    |

|      |      | 1    | 0    | 0    | 131072ステート | 29.1  | 32.8  | 43.7  | 52.4  | 65.5  | 87.4  | 131.1 | 262.1 | 524.3  |    |

|      |      | 1    | 0    | 1    | 1024ステート   | 0.23  | 0.26  | 0.34  | 0.41  | 0.51  | 0.68  | 1.02  | 2.0   | 4.1    |    |

|      |      | 1    | 1    | —    | 使用禁止       |       |       |       |       |       |       |       |       |        |    |

| 1    | 1    | 0    | 0    | 0    | 8192ステート   | 3.6   | 4.1   | 5.5   | 6.6   | 8.2   | 10.9  | 16.4  | 32.8  | 65.5   | ms |

|      |      | 0    | 0    | 1    | 16384ステート  | 7.3   | 8.2   | 10.9  | 13.1  | 16.4  | 21.8  | 32.8  | 65.5  | 131.1  |    |

|      |      | 0    | 1    | 0    | 32768ステート  | 14.6  | 16.4  | 21.8  | 26.2  | 32.8  | 43.7  | 65.5  | 131.1 | 262.1  |    |

|      |      | 0    | 1    | 1    | 65536ステート  | 29.1  | 32.8  | 43.7  | 52.4  | 65.5  | 87.4  | 131.1 | 262.1 | 524.3  |    |

|      |      | 1    | 0    | 0    | 131072ステート | 58.3  | 65.5  | 87.4  | 104.9 | 131.1 | 174.8 | 262.1 | 524.3 | 1048.6 |    |

|      |      | 1    | 0    | 1    | 1024ステート   | 0.46  | 0.51  | 0.68  | 0.82  | 1.0   | 1.4   | 2.0   | 4.1   | 8.2    |    |

|      |      | 1    | 1    | —    | 使用禁止       |       |       |       |       |       |       |       |       |        |    |

□ : 推奨設定時間

#### 20.4.4 ソフトウェアスタンバイモードの応用例

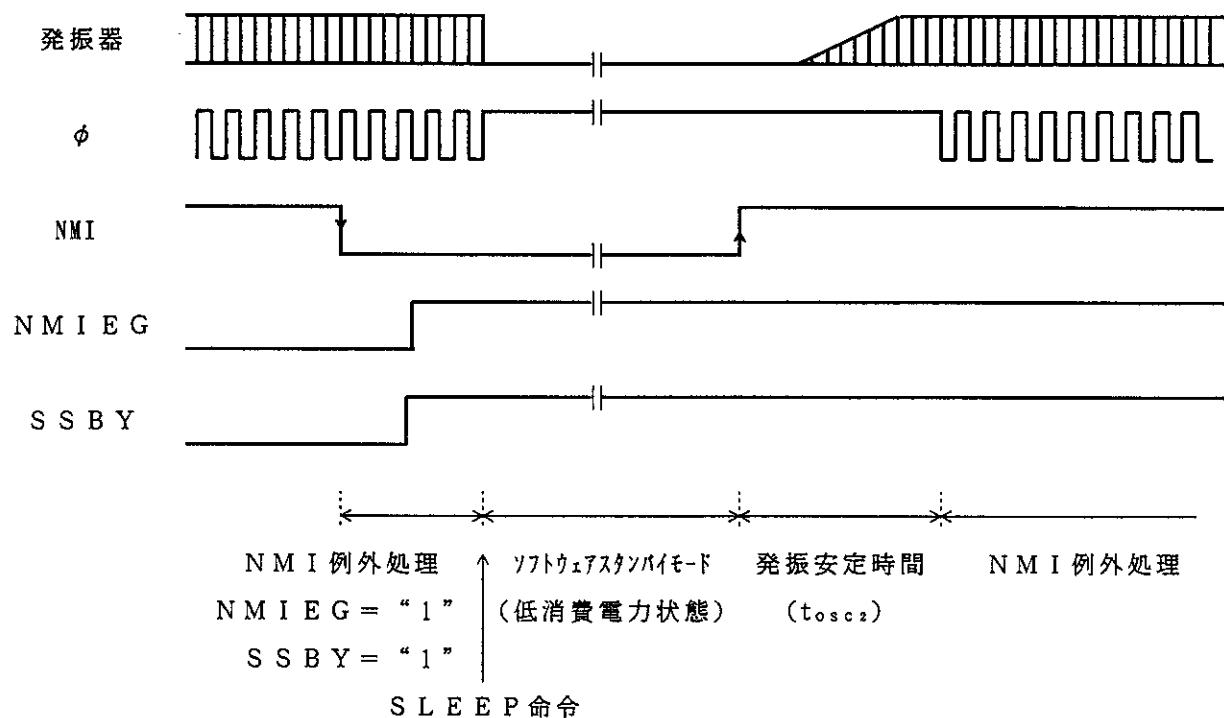

ここでは、NMI端子の立下がりでソフトウェアスタンバイモードに遷移し、NMI端子の立上がりで解除を行う例を、図20.1に示します。

SYSCRのNMIエッジ（NMIEG）ビットが“0”にクリアされている（立下がりエッジ指定）状態でNMI割込みを受け付けた後、NMIEGビットを“1”にセットします（立上がりエッジ指定）。SSBYビットを“1”にセットした後、SLEEP命令を実行してソフトウェアスタンバイモードに遷移します。

その後、NMI端子の立上がりエッジで、ソフトウェアスタンバイモードが解除されます。

図20.1 ソフトウェアスタンバイモード時のNMIタイミング（例）

#### 20.4.5 使用上の注意

ソフトウェアスタンバイモードでは、I/Oポートの状態が保持されます。したがって、“High”レベルを出力している場合、出力電流分の消費電流は低減されません。

## 20.5 ハードウェアスタンバイモード

### 20.5.1 ハードウェアスタンバイモードへの遷移

STBY端子を“Low”レベルにすると、どの処理状態からでもハードウェアスタンバイモードに遷移します。

ハードウェアスタンバイモードでは、CPU、DMAC、リフレッシュコントローラ、および内蔵周辺モジュールの機能が停止するため、消費電力は著しく低減します。内蔵RAM以外のすべてのモジュールはリセット状態になりますが、規定の電圧が与えられている限り、内蔵RAMのデータは保持されます。I/Oポートは、ハイインピーダンス状態になります。

内蔵RAMのデータを保持するためには、STBY端子を“Low”レベルにする前に、SYSCTRのRAMEビットを“0”にクリアしてください。

ハードウェアスタンバイモード中には、モード端子(MD2～MD0)の状態を変化させないでください。

### 20.5.2 ハードウェアスタンバイモードの解除

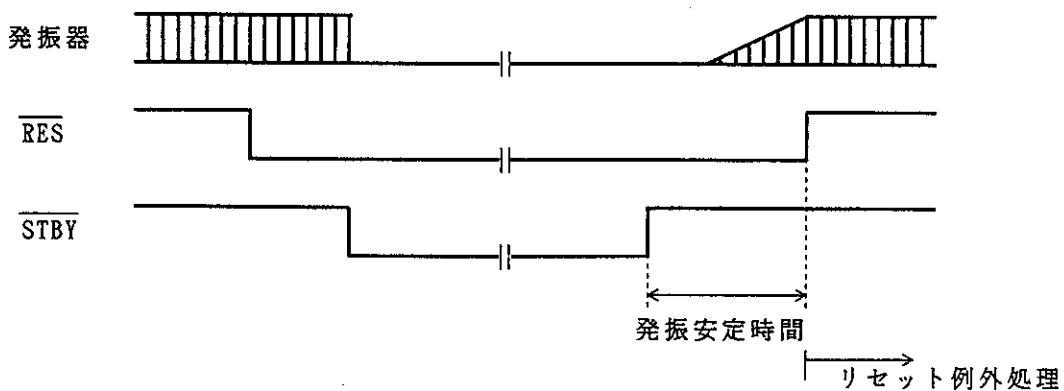

ハードウェアスタンバイモードの解除は、STBY端子とRES端子とで行われます。RES端子を“Low”レベルにした状態で、STBY端子を“High”レベルにすると、クロックは発振を開始します。このとき、RES端子は必ずクロックの発振が安定するまで“Low”レベルに保持してください。RES端子を“High”レベルにするとリセット例外処理を経て、プログラム実行状態に遷移します。

### 20.5.3 ハードウェアスタンバイモードのタイミング

ハードウェアスタンバイモードの各端子のタイミング例を図20.2に示します。

RES端子を“Low”レベルにした後、STBY端子を“Low”レベルにすると、ハードウェアスタンバイモードに遷移します。解除は、STBY端子を“High”レベルにし、クロックの発振安定時間経過後、RES端子を“Low”レベルから“High”レベルにすることにより行われます。

図20.2 ハードウェアスタンバイモードのタイミング

## 20.6 モジュールスタンバイ機能

### 20.6.1 モジュールスタンバイタイミング

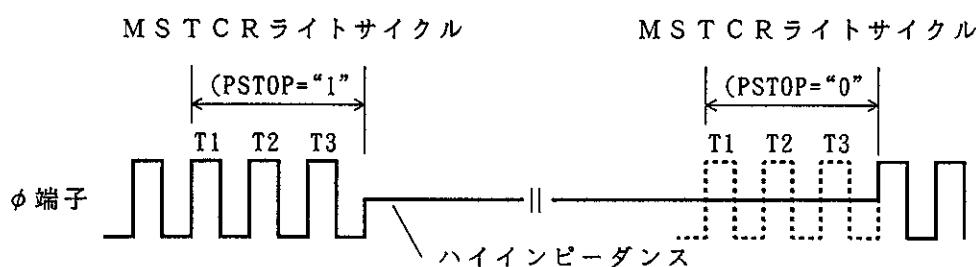

モジュールスタンバイ機能は、MSTCRのMSTOP5～0ビットにより、内蔵モジュールのうちITU、SCI0、SCI1、DMAC、リフレッシュコントローラ、A/D変換器を低消費電力状態とは独立に停止させることができます。MSTOP5～0ビットを“1”にセットすると、MSTCRのライトサイクルの次のバスサイクルの先頭で上記周辺モジュールはスタンバイ状態となり動作が停止します。

### 20.6.2 モジュールスタンバイ中のリード／ライト

モジュールスタンバイ中の周辺モジュールのレジスタに対するリード／ライトはできません。リードすると常にH'FFが読み出されます。ライトは無効です。

### 20.6.3 使用上の注意

モジュールスタンバイ機能を使用するうえで以下のことに注意してください。

#### (1) DMACおよびリフレッシュコントローラの処置

モジュールスタンバイ機能を使用する場合、DMACおよびリフレッシュコントローラはバス権要求が発生しない状態でMSTOP2、1ビットを“1”にセットしてください。バス権要求が発生した状態でMSTOP2、1ビットが“1”にセットされると、バスアービタの動作が不確定となり誤動作の原因となります。

#### (2) 内蔵周辺モジュール割込み

MSTCRのビットを“1”にセットする場合、事前に当該モジュールの割込みを禁止してください。モジュールスタンバイ機能によって、スタンバイ状態となった周辺モジュールはレジスタがすべて初期化されます。

#### (3) 端子の状態

モジュールスタンバイ機能によって、停止したモジュールが使用していた端子は、モジュールの機能が失われます。その後の端子状態については端子ごとに異なりますので、詳細は「第9章 I/Oポート」を参照してください。端子の状態が入力から出力に変化する場合には、特に注意が必要です。例えば、SCI1をモジュールスタンバイにした場合、受信端子はモジュールスタンバイと同時に受信端子としての機能が無くなりポートとなります。ポートのDDRが“1”にセットされていると、端子はデータ出力となり外部SCI送信データと衝突する可能性があります。この場合、ポートのDDRを“0”にクリアするなどの対策をとってください。

#### (4) レジスタの再設定

モジュールスタンバイ機能によって、停止した周辺モジュールのレジスタはすべて初期化されます。このため再動作させる際には、MSTOPビットを“0”にクリアした後、レジスタの再設定が必要です。なおMSTOPビットが“1”にセットされた状態ではレジスタへのライトはできません。

#### (5) DMAによるMSTCRのライト禁止

MSTCRは誤動作の防止のためCPU以外のライトはできません。したがってDMAによるリードはできますがライトはできません。

### 20.7 φクロック出力禁止機能

MSTCRのPSTOPビットにより、φクロックの出力を制御することができます。PSTOPビットを“1”にセットすると、φクロックは停止し、φ端子はハイインピーダンスになります。図20.3にφクロックの発振開始、発振停止のタイミングを示します。PSTOPビットを“0”にクリアした状態では、φクロックの出力は許可されます。表20.4に各処理状態におけるφ端子の状態を示します。

図20.3 φクロック発振開始、発振停止タイミング

表20.4 各処理状態におけるφ端子の状態

| 処理状態        | PSTOP = 0 | PSTOP = 1 |

|-------------|-----------|-----------|

| ハードウェアスタンバイ | ハイインピーダンス | ハイインピーダンス |

| ソフトウェアスタンバイ | “H”固定     | ハイインピーダンス |

| スリープモード     | φ出力       | ハイインピーダンス |

| 通常動作状態      | φ出力       | ハイインピーダンス |